# **Aerial CUDA-Accelerated RAN**

Release 25-1

**NVIDIA Corporation**

Apr 18, 2025

# CONTENTS

| 1  | Aeria  | al cuBB                       | 7   |

|----|--------|-------------------------------|-----|

|    | 1.1    | Getting Started               | 7   |

|    | 1.2    | Product Brief                 | 8   |

|    | 1.3    | cuBB Release Notes            | 108 |

|    | 1.4    | cuBB Installation Guide       | 187 |

|    | 1.5    | cuBB Quickstart Guide         | 250 |

|    | 1.6    | cuBB Integration Guide        | 360 |

|    | 1.7    | cuBB Developer Guide          | 381 |

|    | 1.8    | Glossary                      | 431 |

| 2  | Aeria  | al cuMAC                      | 435 |

|    | 2.1    | Getting Started with cuMAC    | 435 |

|    | 2.2    | cuMAC API Reference           | 437 |

|    | 2.3    | Examples                      | 446 |

|    | 2.4    | cuMAC-CP integration guide    | 452 |

| 3  | Aeria  | al Data Lake                  | 479 |

|    | 3.1    | Target Audience               | 479 |

|    | 3.2    | Key Features                  | 479 |

|    | 3.3    | Design                        | 480 |

|    | 3.4    | Installation                  | 481 |

|    | 3.5    | Usage                         | 482 |

|    | 3.6    | Multi-Cell                    | 482 |

|    | 3.7    | Using Data Lake in Notebooks  | 482 |

|    | 3.8    | Database Administration       | 483 |

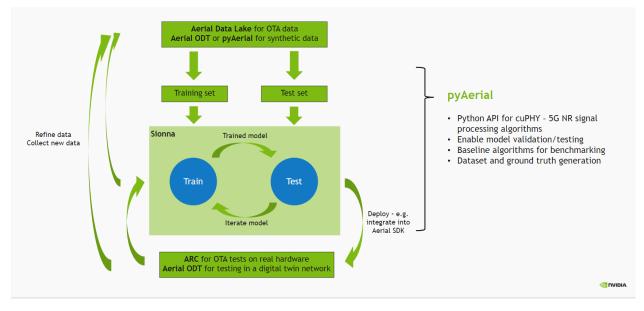

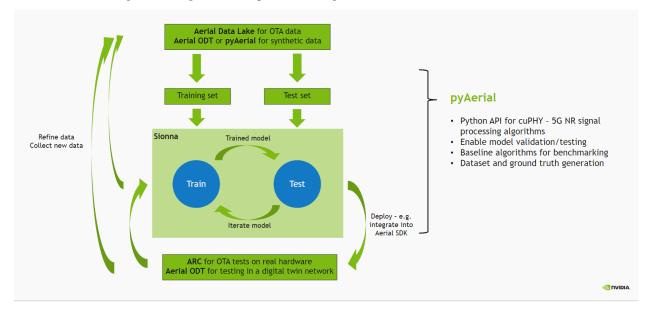

| 4  | руАе   |                               | 489 |

|    | 4.1    | Overview                      | 489 |

|    | 4.2    | Getting Started with pyAerial | 493 |

|    | 4.3    | Examples of Using pyAerial    | 495 |

|    | 4.4    | API Reference                 | 613 |

| Ру | thon N | Module Index                  | 663 |

| In | dex    |                               | 665 |

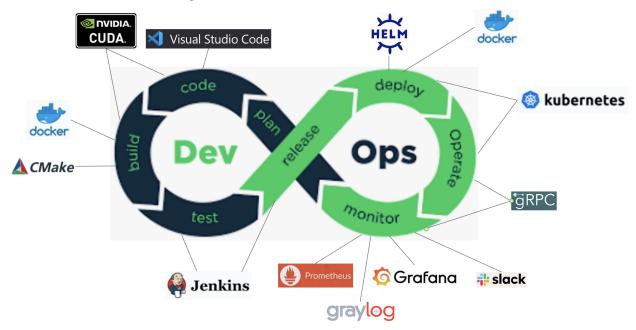

Aerial CUDA-Accelerated RAN brings together the Aerial software for 5G and AI frameworks and the NVIDIA accelerated computing platform, enabling TCO reduction and unlocking infrastructure monetization for telcos.

Aerial CUDA-Accelerated RAN has the following key features:

- Software-defined, scalable, modular, highly programmable and cloud-native, without any fixed function accelerators. Enables the ecosystem to flexibly adopt necessary modules for their commercial products.

- Full-stack acceleration of DU L1, DU L2+, CU, UPF and other network functions, enabling workload consolidation for maximum performance and spectral efficiency, leading to best-in-class system TCO.

- General purpose infrastructure, with multi-tenancy that can power both traditional workloads and cutting-edge AI applications for best-in-class RoA.

#### What's New in 25-1

The following new features are available in release 25-1 for Aerial CUDA-Accelerated RAN:

- Aerial cuPHY: CUDA accelerated inline PHY

- cuPHY 4TR

- \* 20x100MHz 4TR Peak Cells on GH200

- \* NN PUSCH Channel Estimate

- cuPHY 64TR

- \* 3x100MHz 64TR Ave Cells w/ Mod Comp, on GH200

- \* Reconfiguration of static beam weights to RU

- SRS Configuration

- \* Extended number of SRS UEs for mMIMO

- \* BFW calculation for SRS unallocated RBs

- \* Support 4 SRS symbols on S-slot

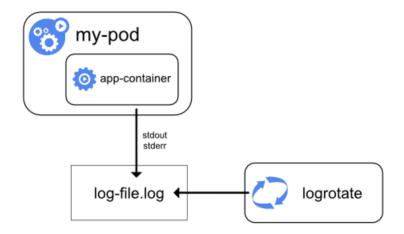

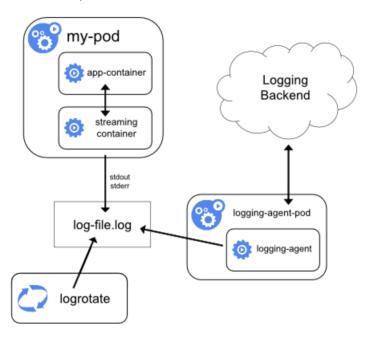

- Operation/Redundancy/Resiliency

- \* Dynamic OAM (Out-Of-Service) configuration or modification of dl/ulBandwidth and eAxCID.

- \* Logging on cloud platform

- \* Version check for YAML configuration files

- \* Enhanced cuBB\_system\_checks script to check versions and configurations required for cuBB test

- \* Cooperative cancellation of GPU workload for PUSCH

- \* Support for FH UL I/Q sample capture in case of CRC errors

- Aerial cuMAC: CUDA accelerated MAC scheduler

- cuMAC-CP

- \* Functional Interface for 4T4R L2

- cuMAC-Sch 4TR

- \* 40x100MHz 4TR Ave Cells on GH200

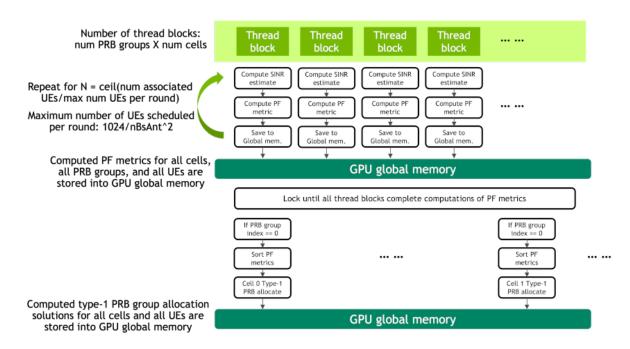

- \* Type 0 & 1, PF Parallel Riding Peaks.

- \* UE Down Selection / TTI

- \* PRB Allocation & Layer Selection

- \* Link Adaptation (MCS OLLA) & AI DRL-MCS

- cuMAC-Sch 64TR

- \* 3x100MHz 64TR Ave Cells on GH200

- \* UE Sorting & down Selection

- \* MU-MIMO user grouping (PRB allocation & Layer Selection) Type 1 & flexible layers per UE.

- \* Link Adaptation (MCS OLLA).

- SRS Configuration

- \* Wideband SRS, Aperiodic, non-inter cell

- \* 40x100MHz 4TR Ave Cells

- Baseline Scheduler on CPU

- \* MU-MIMO Type 1 SU-MIMO PRB allocation for Anchor UE and PF-Based greedy MU-MIMO user grouping.

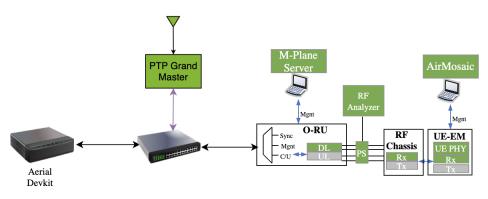

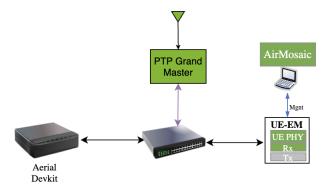

- Aerial E2E: System level / End-to-End validation

- 4T4R 100MHz

- \* 8 Peak Cells in E2E configuration (CN + RAN + UE-EM) validated in eCPRI setup.

- \* Achieving aggregate DL throughput of 11.2Gbps and aggregate UL throughput of 1.68Gbps

- \* AI- RAN: Validated 8 peak cell performance with MIG enabled

- pyAerial: Python interface to Aerial cuPHY

- CuPy-based API, in addition to the existing Numpy-based API

- \* Significantly reduce copies between GPU and host memory

- \* Improve interoperability with other frameworks supporting the CUDA array interface (PyTorch, Numba, etc.)

- New configuration API for configuring pyAerial pipelines and components

- SRS transmitter and receiver pipelines

- SRS example notebook

- CRC encoding

- Performance

- 1x100MHz 64T64R Peak cell / 3x100MHz 64T64R average cells

- 20x100MHz 4T4R Peak cells

#### What's New in 24-3

The following new features are available in release 24-3 for Aerial CUDA-Accelerated RAN:

- Aerial cuPHY: CUDA accelerated inline PHY

- Multi-cell support for mMImO (up to 3 cells)

- Scheduling DL in special slots

- Increase SRS slots in 4T4R and mMIMO

- SRS CS multiplexing for different UEs

- UL PUSCH channel estimation at PRG level

- RKHS channel estimation

- Aerial E2E: System level / End-to-End validation

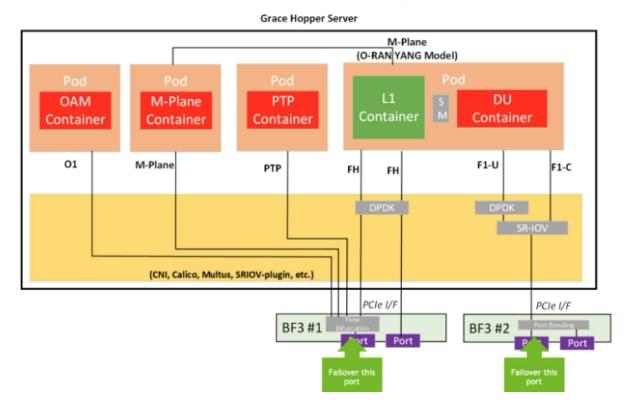

- Fronthaul Port Failover Validation (Active-Standby) of C/U/S-Planes

- Concluded Ch.8 Conformance testing with PRACH

- MIG validation of AI + RAN

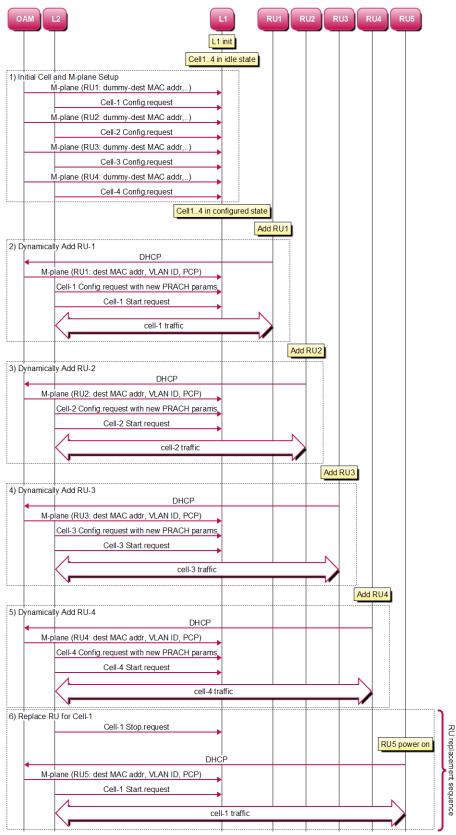

- Aerial Redundancy/Resiliency: CUDA accelerated RAN Redundancy/Resiliency features

- RU Health Monitor actively detect FH connectivity issues with ORU and take corrective action

- Introduce L1 recovery period If L1 is running late, drop FAPI messages for some time to allow L1 to recover

- nvIPC pcap acquisition improvements Introduced capability to add filters (cell-id, msg-id level) to nvIPC pcap acquisition

- Backtrace output on console Aerial prints backtrace on console in case of crash

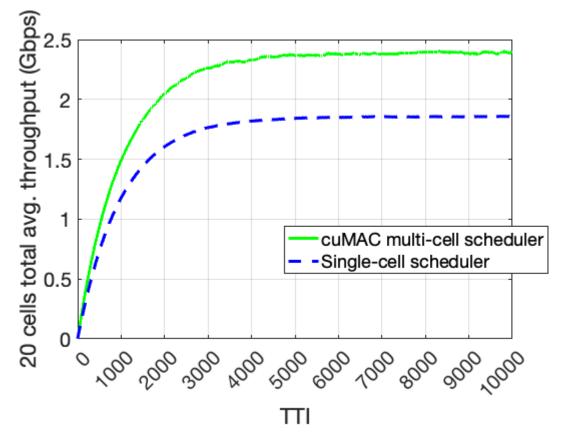

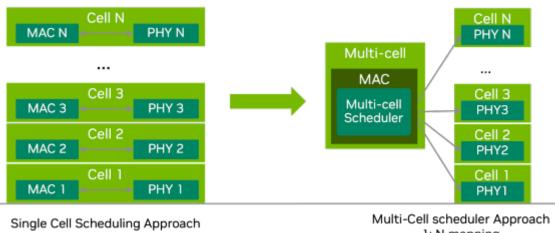

- Aerial cuMAC: CUDA accelerated MAC scheduler

- DRL MCS selection module

- \* Pre-trained neural networks available under aerial\_sdk/cuMAC/testVectors

- \* Inference based on TensorRT

- 64TR MU-MIMO scheduler

- \* UE sorting algorithm based on SRS SNR estimates

- \* UE grouping algorithm based on SRS channel coefficient estimates

- Aperiodic SRS resource manager

- \* Combined with MU-MIMO UE sorting algorithm

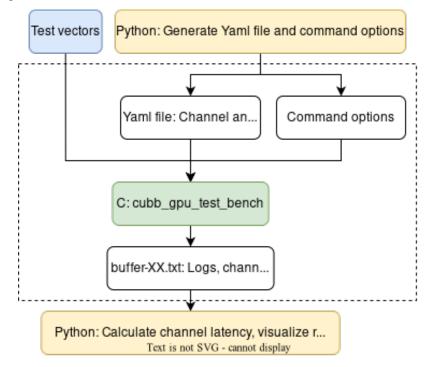

- 4T4R system simulation with GPU-based TDL channel model

- Improved algorithms & CUDA implementation for type-0 and type-1 4T4R schedulers

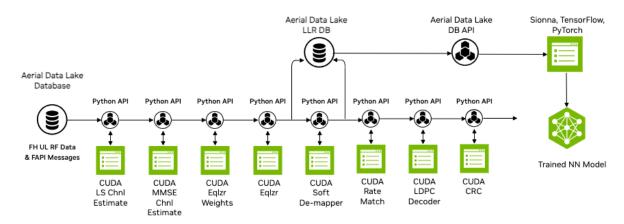

- pyAerial: Python interface to Aerial cuPHY

- CSI-RS transmission pipeline

- RSRP and pre- and post-equalizer SINR estimation

- Carrier frequency offset and timing advance estimation

- CRC checking

- OFDM fading channel simulation

- Support of multiple UE groups for PUSCH receiver pipeline and its components

- An improved API to PUSCH receiver pipeline and its components

#### What's New in 24-2.1

The following new features are available in release 24-2.1 for Aerial CUDA-Accelerated RAN:

- Aerial cuPHY: CUDA accelerated inline PHY

- 64T64R Massive MIMO:

- \* 100 MHz DL max combined 16 layers + UL max combined 8 layers + SRS

- \* 64T64R SRS + Dynamic + Static Beamforming Weights

- \* Support multiple dynamic UE groups

- \* Support flexible PRG size and PRB number

- \* Support SRS buffer indexing from L2

- \* Support non 2<sup>n</sup> layers

- \* Use different section IDs when splitting the C-Plane section

- \* FH messaging for CSIRS + PDSCH and other channel combinations

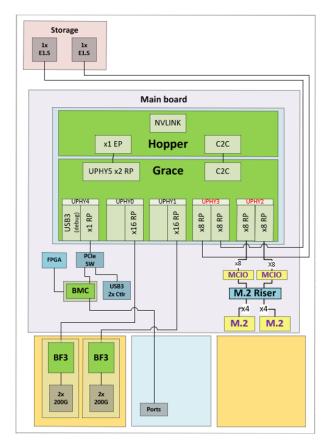

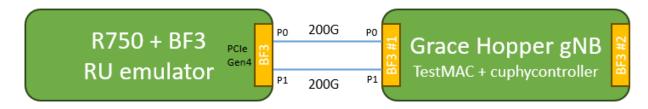

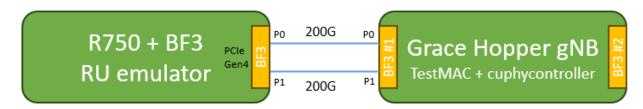

- Support GH200+BF3 as RU emulator platform

#### What's New in 24-2

The following new features are available in release 24-2 for Aerial CUDA-Accelerated RAN:

- Aerial cuPHY: CUDA accelerated inline PHY

- MGX Grace Hopper multicell capacity w/ telco-grade traffic model

- \* 20 peak loaded 4T4R @ 100MHz

- \* Capacity also validated with more challenging traffic model

- · PUSCH and PDCCH symbols in the S-slot

- L1-L2 interface enhancements

- \* Separate FAPI request timelines for PDSCH and PDCCH

- Aerial cuMAC: CUDA accelerated MAC scheduler

- cuMAC-Sch

- \* 4T4R CUDA implementation complete

- cuMAC-CP

- \* 4T4R implementation (Functional early access)

- Aerial cuBB/E2E: System level / End-to-End validation

- Over-The-Air (OTA) validation:

- \* CBRS O-RU

- \* 8 UE OTA w/ 6 UE/TTI for > 8 hours

- RedHat-OCP:

- \* Multicell capacity validated on MGX (GH200+BF3)

- O-RAN Fronthaul:

- \* 16-bit fixed point IQ sample validated E2E (Keysight eLSU)

- \* Simultaneous dual-port FH capability (8 peak cells; 4 per port)

- L2 integration:

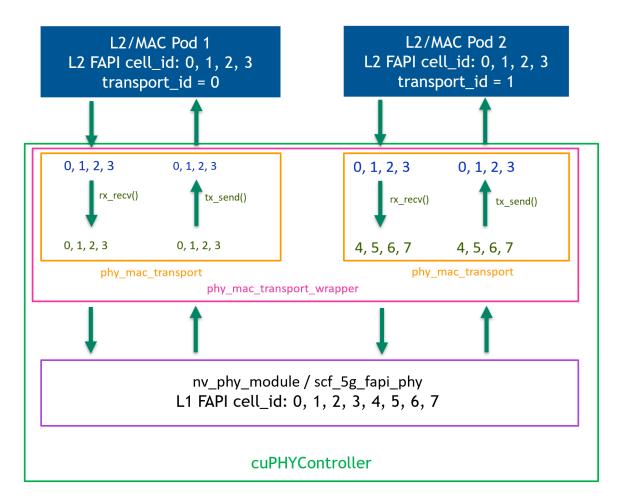

- \* Multi-L2 container instances per L1 validated E2E

- pyAerial: Python interface to Aerial cuPHY

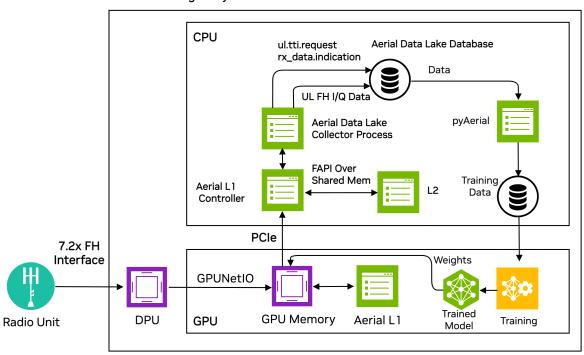

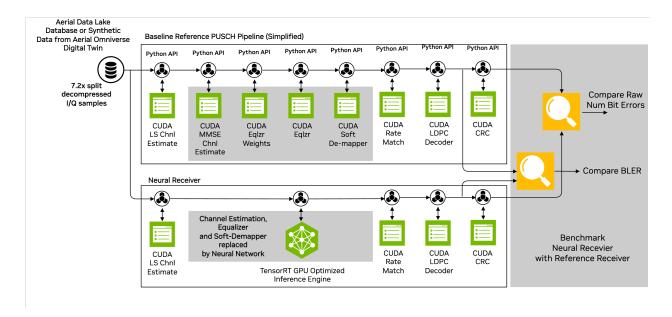

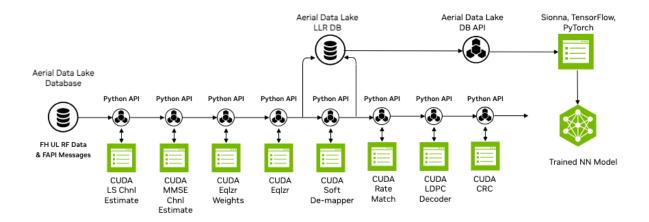

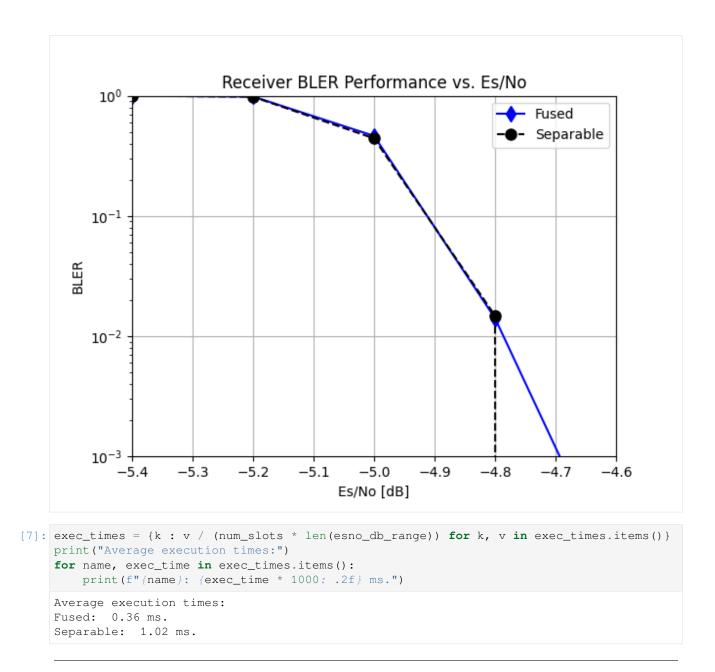

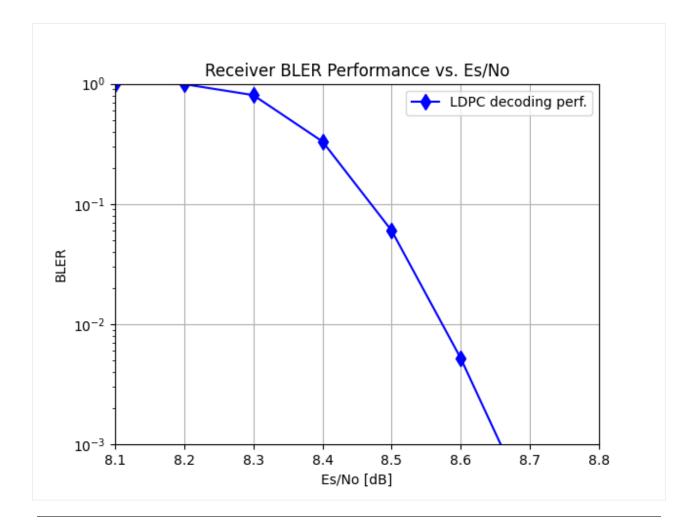

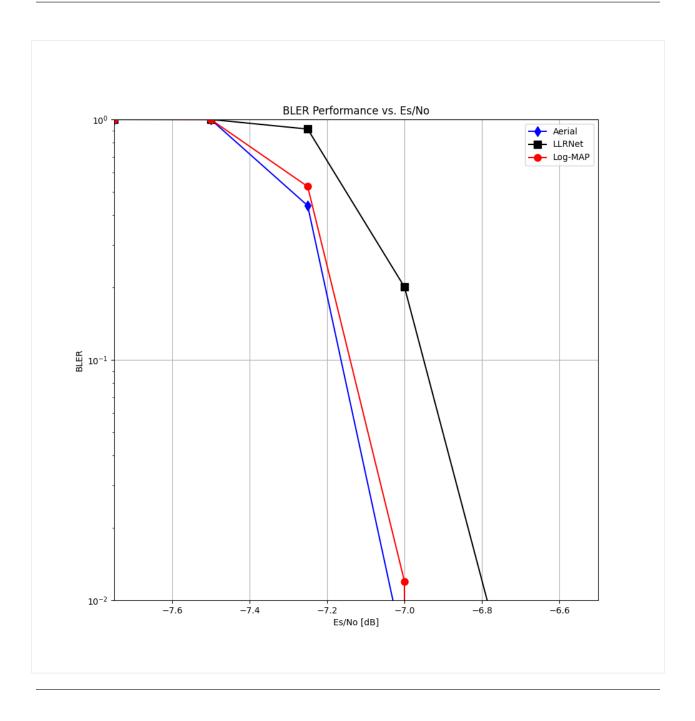

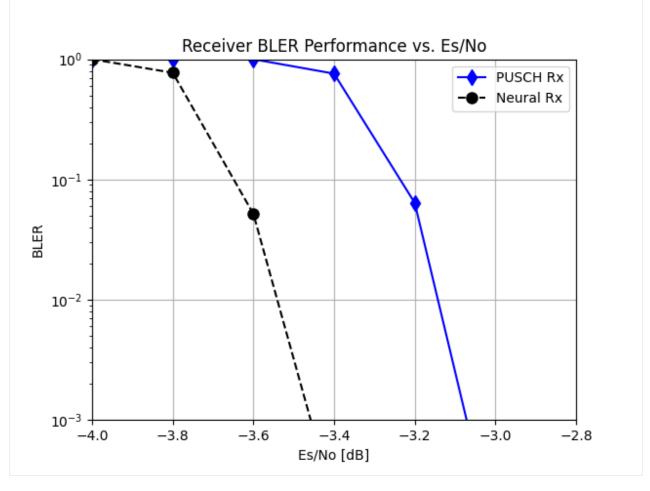

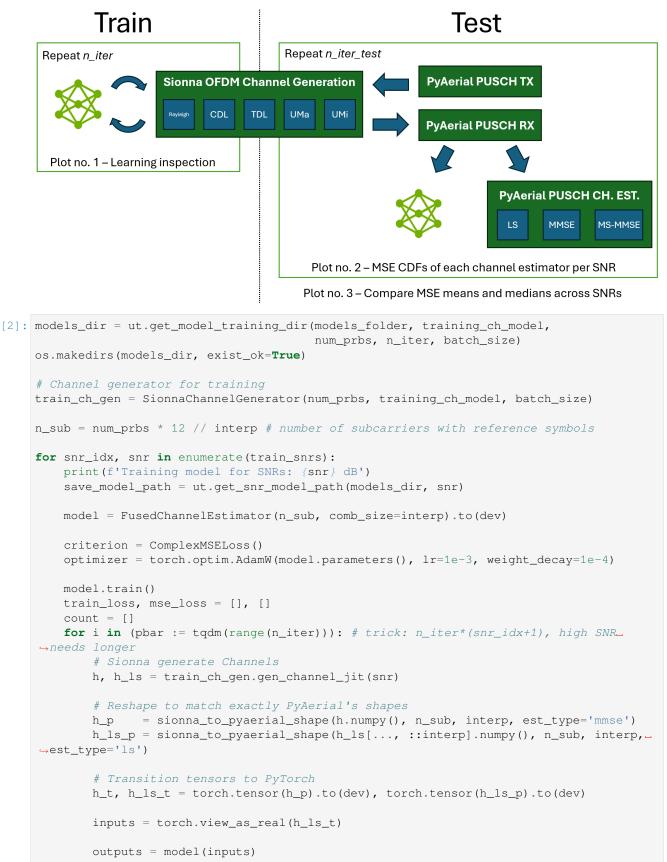

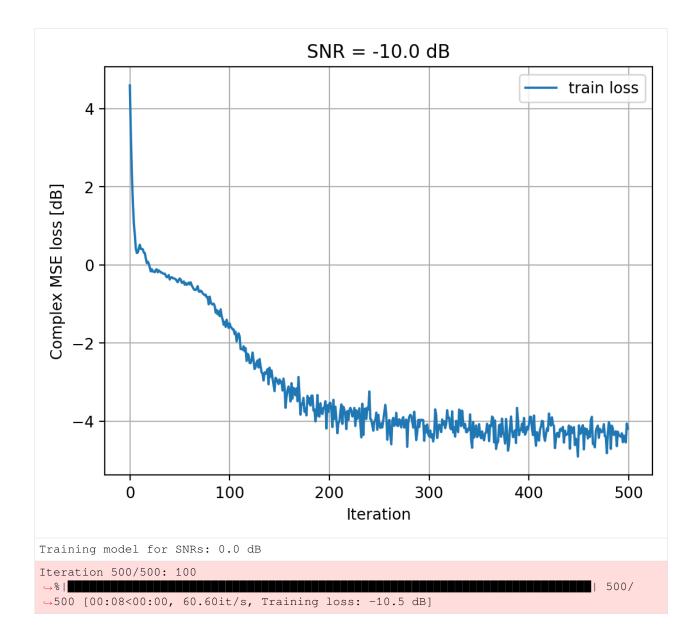

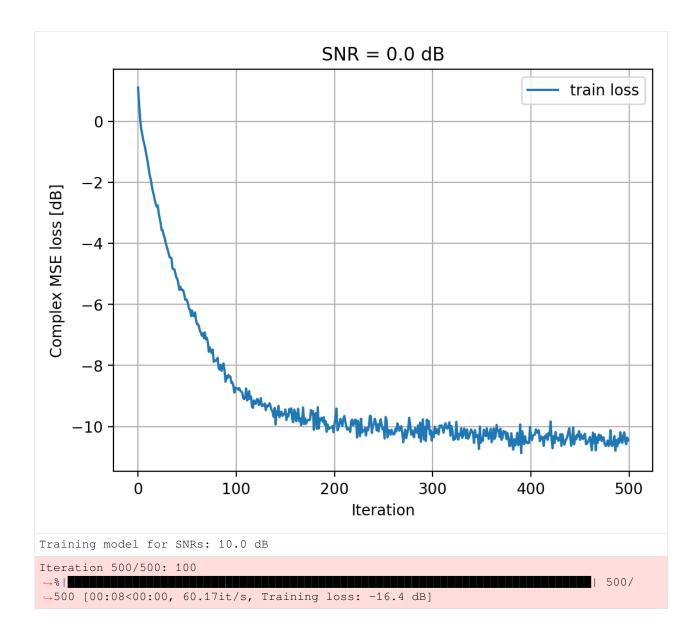

- TensorRT inference engine

- \* Jupyter notebook example using pyAerial to validate a neural PUSCH receiver

- LDPC API improvements

- \* Added soft outputs to LDPC decoder

- LS channel estimation

- Limited support for Grace Hopper

- \* Run pyAerial together with Aerial Data Lakes

#### CHAPTER

# **AERIAL CUBB**

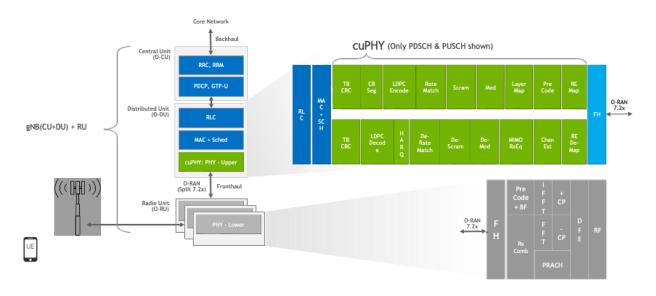

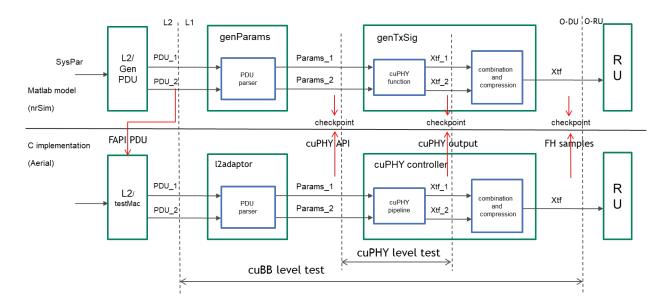

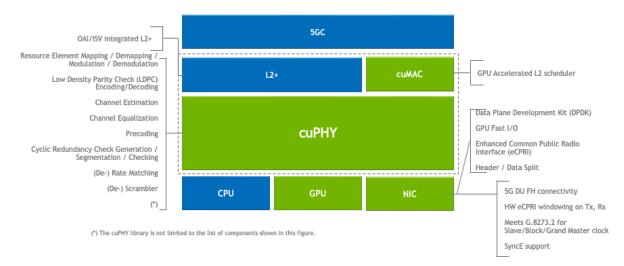

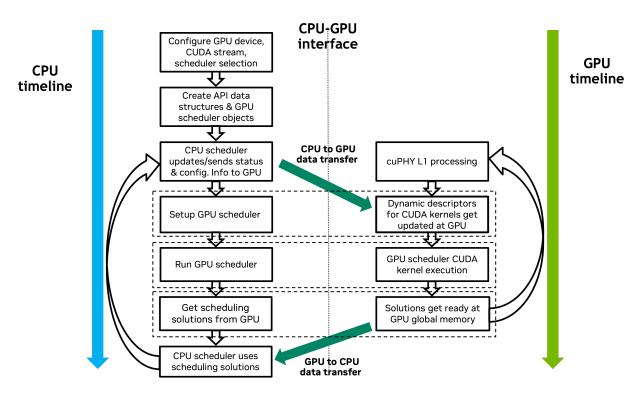

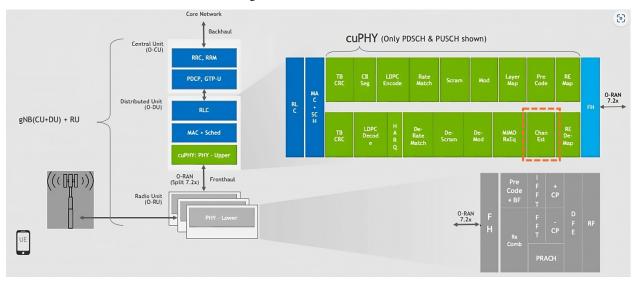

The NVIDIA cuBB SDK provides GPU accelerated 5G signal processing pipeline including cuPHY for Layer 1 PHY, cuMAC for L2 scheduler, delivering unprecedented throughput and efficiency by keeping all the processing within the high-performance GPU memory.

Aerial cuBB is a software-defined, scalable, modular, highly programmable and cloud-native, without any fixed function accelerators. Enables the ecosystem to flexibly adopt necessary modules for their commercial products.

Aerial cuBB has the following key components:

- **cuPHY**: L1 library of the Aerial CUDA-Accelerated RAN. It is designed as an inline accelerator to run on NVIDIA GPUs and it does not require any additional hardware accelerator.

- **cuMAC**: L2 MAC Scheduler library of the Aerial CUDA-Accelerated RAN for accelerating 5G/6G MAC layer scheduler functions with NVIDIA GPUs.

# 1.1 Getting Started

Aerial cuBB brings together the Aerial software for 5G and AI frameworks and the NVIDIA accelerated computing platform, enabling TCO reduction and unlocking infrastructure monetization for telcos.

# 1.1.1 Aerial cuBB Content Map

The following table describes the different sections of the Aerial cuBB developer documentation.

| Section          | Description                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------|

| Product Brief    | Provides an in-depth exploration of the standards and configurations supported by Aerial cuBB.    |

| cuBB Release     | Outlines what Aerial cuBB features and settings have changed in the most recent release of Aerial |

| Notes            | CUDA-Accelerated RAN.                                                                             |

| cuBB Installa-   | Describes how to install Aerial cuBB.                                                             |

| tion Guide       |                                                                                                   |

| cuBB Quickstart  | Describes how to run cuBB software examples.                                                      |

| cuBB Integration | Provides reference information related to the CUDA RAN MAC Scheduler Control Plane                |

| Guide            | (cuMAC-CP) and NVIPC messaging standard.                                                          |

| cuBB Developer   | Provides reference information for the cuPHY library software stack.                              |

| Guide            |                                                                                                   |

# **1.2 Product Brief**

This section includes an in-depth exploration of the standards and configurations supported by Aerial cuBB.

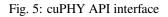

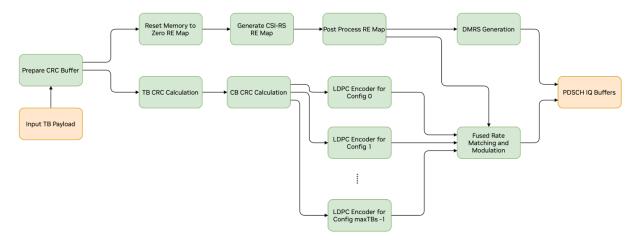

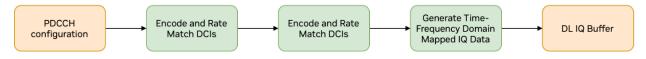

# 1.2.1 cuPHY Features Overview

This section provides an overview of supported features in cuPHY.

#### **Supported Features**

#### **Aerial CUDA-Accelerated RAN Layer 1**

Aerial CUDA-Accelerated RAN adheres to 3GPP Release 15 standard specifications to deliver the necessary Layer 1 capabilities for a gNB.

#### **3GPP Release 15**

Aerail cuPHY adheres to 3GPP Release 15 standard specifications to deliver the following capabilities for gNB Layer 1. Overall PHY capabilities include:

- · Error detection on the transport channel and indication to higher layers

- FEC encoding/decoding of the transport channel

- Hybrid ARQ soft-combining

- Rate matching of the coded transport channel to physical channels

- Mapping of the coded transport channel onto physical channels

- Power weighting of physical channels

- Modulation and demodulation of physical channels including:

- Frequency and time synchronization

- Radio characteristics measurements and indication to higher layers

- Multiple Input Multiple Output (MIMO) antenna processing

- Transmit Diversity (TX diversity)

- Digital and Analog Beamforming

- RF processing

# **PHY FH Interface**

# Aerial CUDA-Accelerated RAN PHY Overall Capabilities

| Features                                                                                                | Configuration                                   | Supported |

|---------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------|

| Standard support                                                                                        | 3GPP 5G NR Rel 15                               | Р         |

| Duplexing Mode                                                                                          | TDD                                             | Y         |

| Nawrrow Bandwidth (MHz)                                                                                 | 30MHz, 40 MHz, 50MHz, 80 MHz                    | Р         |

| Channel Bandwidth (MHz)                                                                                 | 100 MHz                                         | Y         |

| Subcarrier Spacing (kHz)                                                                                | 30khz                                           | Y         |

| Maximum Number of Subcarriers<br>(Max number of RBs x Num of Sub-<br>carriers per RB) = $273 \times 12$ | 3276                                            | Y         |

| Downlink Waveform                                                                                       | CP-OFDM                                         | Y         |

| Uplink Waveform                                                                                         | CP-OFDM                                         | Y         |

|                                                                                                         | DFT-s-OFDM (for data and control)               | Y         |

|                                                                                                         | Configurable to DFT-s-OFDM (for data & Control) | Y         |

| Number of Downlink SU-MIMO layers                                                                       | Up to 4                                         | Y         |

| Number of Uplink SU-MIMO layers                                                                         | 1, 2                                            | Y         |

| Number of Tx physical antennas                                                                          | 1                                               | Ν         |

|                                                                                                         | 2                                               | Y         |

|                                                                                                         | 4                                               | Y         |

|                                                                                                         | 8                                               | Ν         |

|                                                                                                         | 64                                              | Y         |

| Number of Rx physical antennas                                                                          | 1                                               | Ν         |

|                                                                                                         | 2                                               | Y         |

|                                                                                                         | 4                                               | Y         |

|                                                                                                         | 8                                               | Ν         |

|                                                                                                         | 64                                              | Y         |

| Slot format                                                                                             | DDDSUUDDDD<br>S = $6:4:4$ (DL: G: UL)           | Y         |

| Carrier Aggregation                                                                                     | Configurable component carriers                 | Y         |

| Configurable BW Parts                                                                                   | Up to 4                                         | Y         |

| BBU-RRU split option                                                                                    | 7.1                                             | Y         |

|                                                                                                         | 7.2                                             | Y         |

|                                                                                                         | 8                                               | Ν         |

| Maximum Downlink throughput per<br>user (Mbps) 4T4R configuration                                       | 1870                                            | Y         |

| Maximum Uplink throughput per<br>user (Mbps) 4T4R configuration                                         | 467                                             | Y         |

# TS 38.211 Numerologies, Physical Resources, Modulation, Sequence, Signal Generation

#### Aerial CUDA-Accelerated RAN PHY Numerologies

| Feature                     | Configuration                                                                                                          | Sup-<br>ported |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------|----------------|

| Numerologies:Normal<br>CP   | $\mu$ =0:SCS=15kHz, 14symbol/slot, 10slot/frame, 1slot/subframe, Normal CP                                             | N              |

|                             | $\mu$ =1:SCS=30kHz, 14symbol/slot, 20slot/frame, 2slot/subframe, Normal CP                                             | Y              |

|                             | $\mu$ =2:SCS=60kHz, 14symbol/slot, 40slot/frame, 4slot/subframe, Normal CP                                             | Ν              |

|                             | $\mu$ =3:SCS=120kHz, 14symbol/slot, 80slot/frame, 8slot/subframe, Normal CP                                            | Ν              |

|                             | μ=4:SCS=240kHz, 14symbol/slot, 160slot/frame, 16slot/subframe,<br>Normal CP                                            | Ν              |

| Numerologies:Extended<br>CP | $\mu {=} 2: {\tt SCS} {=} 60 {\tt kHz}, 12 {\tt symbol/slot}, 40 {\tt slot/frame}, 4 {\tt slot/subframe}, Extended CP$ | N              |

# Aerial CUDA-Accelerated RAN Overall PHY Physical Resources

| Feature                                                                                                  | Sup-<br>portec |

|----------------------------------------------------------------------------------------------------------|----------------|

| Antenna Ports                                                                                            | Y              |

| Resource Grid                                                                                            | Y              |

| Resource Elements                                                                                        | Y              |

| Resource Block                                                                                           | Y              |

| Resource Block - Common Resource Block(CRB)                                                              | Y              |

| Resource Block - Physical Resource Block(PRB)                                                            | Y              |

| Resource Block - Virtual Resource Block (VRB)                                                            | Y              |

| Bandwidth Part (BWP)                                                                                     | Y              |

| Dynamically adapt the carrier bandwidth and numerology in which a UE operates                            |                |

| A bandwidth part is a subset of contiguous common resource blocks for a given numerology µi in bandwidth |                |

| part i on a given carrier.                                                                               |                |

| A UE can be configured with up to four bandwidth parts in UL and DL                                      |                |

# Aerial CUDA-Accelerated RAN PHY Physical Resources – BWP

| Feature                                                                                                  | Sup-<br>ported |

|----------------------------------------------------------------------------------------------------------|----------------|

| Bandwidth Part (BWP)                                                                                     | Y              |

| Dynamically adapt the carrier bandwidth and numerology in which a UE operates                            |                |

| A bandwidth part is a subset of contiguous common resource blocks for a given numerology µi in bandwidth |                |

| part i on a given carrier                                                                                |                |

| A UE can be configured with up to four bandwidth parts in both UL and DL                                 |                |

| Default Aerial CUDA-Accelerated RAN startup configuration to not use BWP, can be enabled to support BWP  | Ν              |

| on a per carrier basis (while cell OOS)                                                                  |                |

| Default Aerial CUDA-Accelerated RAN startup configuration to not use BWP, can be enabled to support BWP  | Ν              |

| on a per carrier basis at startup                                                                        |                |

# Aerial CUDA-Accelerated RAN Overall Carrier Aggregation

| Feature                                    | Description                                                                                               | Supported (emulated) |

|--------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------|

| Carrier Aggregation                        | Transmissions in multiple cells can be aggregated to support inter-<br>band and intra-band configurations | Y                    |

| 100MHz                                     | Up to 2 cells aggregation(1CC,2CC)                                                                        | Y                    |

|                                            | Up to 4 cells aggregation(1CC,2CC,3CC, 4CC)                                                               | Y                    |

| Narrowband Carrier Aggre-<br>gation (ZMhz) | Configurable upto 4 component carriers                                                                    | Y                    |

#### Aerial CUDA-Accelerated RAN PHY Modulation Mapper

| Modulation Scheme | Supported |

|-------------------|-----------|

| Pi/2 BPSK         | Y         |

| BPSK              | Y         |

| QPSK              | Y         |

| 16QAM             | Y         |

| 64QAM             | Y         |

| 256QAM            | Y         |

#### Aerial CUDA-Accelerated RAN PHY Sequence Generation

| Feature                  | Description                                                                                                   | Sup-<br>ported |

|--------------------------|---------------------------------------------------------------------------------------------------------------|----------------|

| Sequence Gen-<br>eration | Pseudo-random sequence generation<br>Generic pseudo-random sequences are defined by a length-31 Gold sequence | Y              |

|                          | Low-PAPR sequence generation type 1                                                                           | Y              |

|                          | Low-PAPR sequence generation type 2                                                                           | Y              |

# OFDM Baseband Signal Generation (UL DFT-S-OFDM)

| Feature                                                                                                 | Configuration                                                                                                                                                                                                                                                      | Supported           |

|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Signal generation for all channels ex-<br>cept PRACH & RIM-RS                                           |                                                                                                                                                                                                                                                                    | RU support expected |

| PRACH                                                                                                   |                                                                                                                                                                                                                                                                    | RU support expected |

| RIM-RS                                                                                                  |                                                                                                                                                                                                                                                                    | RU support expected |

| Uplink waveform<br>Support concurrent UE configuration<br>to use CP-OFDM or DFT-S-OFDM<br>on same cell. | <ul> <li>DFT-S-OFDM for UL.</li> <li>Some specific parameters:</li> <li>Support for PUSCH and for<br/>PUCCH format 3</li> <li>Support 0.5 pi-BPSK for Mod-<br/>ulation</li> <li>Support DMRS group hopping</li> <li>Support DMRS sequence hop-<br/>ping</li> </ul> | Υ                   |

TS 38.211 Channels

| Category                         | L1 requirement                                                                             | Sup-<br>ported |

|----------------------------------|--------------------------------------------------------------------------------------------|----------------|

| Downlink Channels (TX<br>)       | PDSCH processing                                                                           | Y              |

|                                  | PDCCH processing                                                                           | Y              |

|                                  | PBCH processing                                                                            | Y              |

| Downlink signals (TX)            | DMRS for PDSCH                                                                             | Y              |

|                                  | DMRS for PDCCH                                                                             | Y              |

|                                  | DMRS for PBCH                                                                              | Y              |

|                                  | PSS, SSS                                                                                   | Y              |

|                                  | CSI-RS, TRS                                                                                | Y              |

|                                  | PT-RS                                                                                      | Ν              |

| Downlink Physical Re-<br>sources | Antenna ports starting with 1000 for PDSCH                                                 | Y              |

|                                  | Antenna ports starting with 2000 for PDCCH                                                 | Y              |

|                                  | Antenna ports starting with 3000 for channel-state information reference sig-<br>nals      | Y              |

|                                  | Antenna ports starting with 4000 for SS/PBCH block transmission                            | Y              |

| Uplink Channels (RX)             | PUSCH processing                                                                           | Y              |

|                                  | PUCCH processing                                                                           | Y              |

|                                  | PRACH processing                                                                           |                |

| Uplink signals (RX)              | DMRS for PUSCH                                                                             | Y              |

|                                  | DMRS for PUCCH                                                                             | Y              |

|                                  | SRS                                                                                        | Y              |

|                                  | PT-RS                                                                                      | Ν              |

| Uplink physical Re-<br>sources   | Antenna ports starting with 0 for PUSCH and associated demodulation ref-<br>erence signals | Y              |

|                                  | Antenna ports starting with 1000 for SRS                                                   | Y              |

|                                  | Antenna ports starting with 2000 for PUCCH                                                 | Y              |

|                                  | Antenna port 4000 for PRACH                                                                | Y              |

# Aerial CUDA-Accelerated RAN Physical Overall Channels and Reference Signals

| Features                           | Configuration                             | Supported |

|------------------------------------|-------------------------------------------|-----------|

| Number of codewords                | 1                                         | Y         |

| Scrambling                         |                                           | Y         |

| Modulation schemes                 | Pi/2-BPSK                                 | Y         |

|                                    | QPSK                                      | Y         |

|                                    | 16 QAM                                    | Y         |

|                                    | 64 QAM                                    | Y         |

|                                    | 256 QAM                                   | Y         |

| PUSCH transform precoding mode     | Disable                                   | Y         |

|                                    | Enable                                    | Y         |

| Precoding                          | Implemented in UE for UL                  | Y         |

| HARQ process                       | Number of HARQ process = $1$              | Y         |

| HARQ process                       | Maximum number of HARQ process is 16      | Y         |

| Mapping to virtual resource blocks |                                           | Y         |

| VRB to PRB mapping Type            | Non-interleaved                           | Y         |

|                                    | Interleaved                               | Ν         |

| Transmission Mode                  | SU-MIMO up to 4 layers                    | Y         |

|                                    | MU-MIMO up to 8 layers                    | Y         |

| PUSCH DMRS CDM group without data  | PUSCH DMRS CDM group without data 1       | Y         |

|                                    | PUSCH DMRS CDM group without data 2       | Y         |

| PUSCH users per TTI                | 16                                        | Y         |

| Uplink algorithm                   | UL HARQ control                           | Y         |

|                                    | UL Channel Estimation LS                  | Y         |

|                                    | MRC, MMSE for equalizer                   | Y         |

|                                    | IRC, MMSE for equalizer                   | Y         |

|                                    | Frequency Offset Correction               | Y         |

| Rate Matching                      | I_LBRM = 1 (Limited Buffer Rate Matching) | Y         |

|                                    | I_LBRM = 0 (Limited Buffer Rate Matching) | Y         |

# Aerial CUDA-Accelerated RAN Overall Channel - PUSCH (Physical Uplink Shared Channel)

Aerial CUDA-Accelerated RAN Overall Channel - PUCCH (Physical Uplink Control Channel

| Format                                      | Configuration                         | Supported |

|---------------------------------------------|---------------------------------------|-----------|

| Format                                      | 0                                     | Y         |

|                                             | 1                                     | Y         |

|                                             | 2                                     | Y         |

|                                             | 3                                     | Y         |

|                                             | 4                                     | Ν         |

| UCI sched coding, AFC, DFT (Format 1)       |                                       | Ν         |

| Modulation schemes                          | Pi/2-BPSK, BPSK, QPSK                 | Y         |

| Scheduling Request SR                       | Support needed                        | Y         |

| Group hopping                               | neither                               | Y         |

|                                             | disable                               | Y         |

|                                             | enable                                | Y         |

| Sequence cyclic shift                       | Zadoff-Chu sequence                   | Y         |

| Intra-slot Frequency hopping/second hop PRB | Support                               | Y         |

| Inter-slot Frequency hopping/second hop PRB | Support                               | Y         |

| PUCCH over multiple slots                   | Number of slots - 2,4,8               | Ν         |

| Frequency Offset Correction                 | PUCCH format 1, 3                     | Ν         |

| Multi-UE support                            | 24 UEs / TTI                          | Y         |

| PUCCH UCI HARQ-ACK Polar                    | codeblock CB size < 359, liftsize = 8 | Y         |

# 1-Capabilities-TSx211-6-3-3] Aerial CUDA-Accelerated RAN Overall Channel - PRACH(PHY Random Access Channel)

| Feature                           | Configuration                                   | Supported |

|-----------------------------------|-------------------------------------------------|-----------|

| Format                            | A1                                              | Ν         |

|                                   | A2                                              | Ν         |

|                                   | A3                                              | Ν         |

|                                   | B1                                              | Ν         |

|                                   | B2                                              | Ν         |

|                                   | B3                                              | Ν         |

|                                   | B4                                              | Y         |

|                                   | C0                                              | Ν         |

|                                   | C2                                              | Ν         |

|                                   | 0                                               | Ν         |

|                                   | 1                                               | Ν         |

|                                   | 2                                               | Ν         |

|                                   | 3                                               | Ν         |

| Subcarrier Spacing (kHz)          | 1.25                                            | Ν         |

|                                   | 5                                               | Ν         |

|                                   | 15                                              | Ν         |

|                                   | 30                                              | Y         |

| Sequence cyclic shift             | Zadoff-Chu sequence                             | Y         |

| Preamble length                   | 839                                             | Ν         |

|                                   | 139                                             | Y         |

| Number of PRACH occasions per TTI | 4 FDM                                           | Y         |

| Contention based Random Access    | Configurable non-contention based Random Access | Ν         |

# Aerial CUDA-Accelerated RAN Overall PHY - UL Reference Signals

#### PUSCH

| Signal                                                                   | Configuration                                                  | Sup-<br>ported |

|--------------------------------------------------------------------------|----------------------------------------------------------------|----------------|

| PUSCH DMRS sequence generation when transform pre-<br>coding is disabled |                                                                | Y              |

| PUSCH DMRS sequence generation when transform pre-<br>coding is enabled  | Neither group, nor sequence hopping is en-<br>abled            | Y              |

| -                                                                        | Group hopping is enabled and sequence hopping is disabled      | Y              |

|                                                                          | Sequence hopping is enabled and group hop-<br>ping is disabled | Y              |

| Demodulation reference signal for PUSCH Mapping to                       | DM-RS configuration type 1                                     | Y              |

| physical resources                                                       | DM-RS configuration type 2                                     | Ν              |

|                                                                          | UL-DMRS-max-len=1                                              | Y              |

|                                                                          | UL-DMRS-max-len=2                                              | Y              |

|                                                                          | UL-DMRS-add-pos=0                                              | Y              |

|                                                                          | UL-DMRS-add-pos=1                                              | Y              |

|                                                                          | UL-DMRS-add-pos=2                                              | Y              |

|                                                                          | UL-DMRS-add-pos=3                                              | Y              |

| Phase-tracking reference signals for PUSCH Sequence                      | transform precoding is not enabled                             | Ν              |

| generation                                                               | transform precoding is enabled                                 | Ν              |

| Phase-tracking reference signals for PUSCH Mapping to                    | transform precoding is disabled                                | Ν              |

| physical resources                                                       | transform precoding is enabled                                 | Ν              |

#### PUCCH

| Signal                                                                    | Configuration                             | Sup-<br>ported |

|---------------------------------------------------------------------------|-------------------------------------------|----------------|

| Demodulation reference signal for PUCCH format 1                          | no intra-slot frequency hopping           | Y              |

|                                                                           | intra-slot frequency hopping en-<br>abled | Y              |

| Demodulation reference signal for PUCCH format 2                          |                                           | Y              |

| Demodulation reference signal for PUCCH format 3 (Format 4 not supported) | No additional DM-RS, No hop-<br>ping      | Y              |

|                                                                           | No Additional DM-RS, hopping              | Y              |

|                                                                           | Additional DM-RS, No hopping              | Y              |

|                                                                           | Additional DM-RS, hopping                 | Y              |

SRS

| Signal                                                       | Configuration                                  | Sup-<br>ported |

|--------------------------------------------------------------|------------------------------------------------|----------------|

| Sounding reference signal resource                           | Antenna ports=1, 10FDM symbols                 | Y              |

|                                                              | Antenna ports=1, 20FDM symbols                 | Y              |

|                                                              | Antenna ports=1, 40FDM symbols                 | Y              |

|                                                              | Antenna ports=2, 10FDM symbpls                 | Y              |

|                                                              | Antenna ports=2, 20FDM symbols                 | Y              |

|                                                              | Antenna ports=2, 40FDM symbols                 | Y              |

|                                                              | Antenna ports=4, 10FDM symbpls                 | Y              |

|                                                              | Antenna ports=4, 20FDM symbols                 | Y              |

|                                                              | Antenna ports=4, 40FDM symbols                 | Y              |

| Sounding reference signal Sequence generation                | KTC=2                                          | Y              |

|                                                              | KTC=4                                          | Y              |

|                                                              | KTC=8                                          | Y              |

| Sounding reference signal Mapping to physical re-<br>sources | CSRS=0~63                                      | Y              |

| Sounding reference signal slot configuration                 | Indicated by higher layer parameter SRS-Config | Y              |

#### PTRS

| Signal | Configuration | Supported |

|--------|---------------|-----------|

| PTRS   |               | Ν         |

# Aerial CUDA-Accelerated RAN Overall Channel - PDSCH(PHY DL Shared Channel)

| Feature                          | Configuration                   | Supported |

|----------------------------------|---------------------------------|-----------|

| Scrambling                       |                                 | Y         |

| Modulation schemes               | QPSK                            | Y         |

|                                  | 16 QAM                          | Y         |

|                                  | 64 QAM                          | Y         |

|                                  | 256 QAM                         | Y         |

| Transmission Mode                | 4T4R SU-MIMO up to 4 layers     | Y         |

|                                  | 64T64R MU-MIMO up to 16 layers  | Y         |

| Number of codewords              | 1                               | Y         |

|                                  | 2                               | Ν         |

| Number of antenna ports          | 1000 - 1011                     | Y         |

| Number of physical antennas      | 4                               | Y         |

|                                  | 64                              | Y         |

| Beam Forming weights computation | BF m2                           | Ν         |

| Precoding                        | non-codebook                    | Y         |

|                                  | pre-coding weight               | Y         |

|                                  | Type I Single-Panel Codebook    | Ν         |

|                                  | Type I Multi-Panel Codebook     | Ν         |

|                                  | Type II Codebook                | Ν         |

|                                  | Type II Port Selection Codebook | Ν         |

| PDSCH mapping type               | Type A                          | Y         |

continues on next page

| Feature                            | Configuration      | Supported |

|------------------------------------|--------------------|-----------|

|                                    | Type B             | Y         |

| Resource allocation type           | Type 0 (4T4R only) | Y         |

|                                    | Type 1             | Y         |

| VRB to PRB mapping Type            | Non-interleaved    | Y         |

|                                    | Interleaved        | Ν         |

| PDSCH DMRS CDM groups without data | 1                  | Y         |

|                                    | 2                  | Y         |

|                                    | 3                  | N/A       |

| Number PDSCH users per TTI         | 16                 | Y         |

| Power Control                      | PDSCH              | Y         |

|                                    | DMRS - PDSCH       | Y         |

| Table 3 | - continued fro | om previous page |

|---------|-----------------|------------------|

|---------|-----------------|------------------|

# Aerial CUDA-Accelerated RAN Overall Channel - PDCCH (Physical DL Control Channel)

| Feature                                          | Configuration                                  | Supported |

|--------------------------------------------------|------------------------------------------------|-----------|

| Scrambling                                       | Up to 2 codewords                              | Ν         |

| CORESET                                          | Normal                                         | Y         |

|                                                  | RMSI CORESET                                   | Y         |

| SSB - RMSI CORESET multiplexing pattern          | Pattern 1                                      | Y         |

| Aggregation Level                                | 1                                              | Y         |

|                                                  | 2                                              | Y         |

|                                                  | 4                                              | Y         |

|                                                  | 8                                              | Y         |

|                                                  | 16                                             | Y         |

| Modulation schemes                               | QPSK                                           | Y         |

| Layer mapping                                    | Supported                                      | Y         |

| Antenna port mapping                             | Supported                                      | Y         |

| Mapping to virtual resource blocks               | Supported                                      | Y         |

| Mapping from virtual to physical resource blocks | Non-interleaved VRB-to-PRB mapping             | Y         |

| Polar code                                       | Block length up to 128 bits                    | Y         |

| DMRS (Demodulation Reference Signal)             | m-sequence                                     | Y         |

| CCE To REG Mapping Type                          | Non-interleaved                                | Y         |

|                                                  | Interleaved                                    | Y         |

| Number OFDM symbol of CORESET                    | 1                                              | Y         |

|                                                  | 2                                              | Y         |

|                                                  | 3                                              | Y         |

| Power Control                                    | PDCCH                                          | Y         |

|                                                  | DMRS-PDCCH                                     | Y         |

| DCI format                                       | 0_0                                            | NA        |

|                                                  | 0_1                                            | NA        |

|                                                  | 1_0                                            | NA        |

|                                                  | 1_1                                            | NA        |

|                                                  | 2_x                                            | NA        |

| Precoding                                        | Precoding Matrix Idx based precoding in the DU | Y         |

|                               | Configuration               | cuBB Tested |

|-------------------------------|-----------------------------|-------------|

| Precoding                     |                             | Y           |

| Scrambling                    | SS/PBCH block index Lmax=4  | Ν           |

|                               | SS/PBCH block index Lmax=8  | Ν           |

|                               | SS/PBCH block index Lmax=64 | Ν           |

| Modulation schemes            | QPSK                        | Y           |

| Mapping to Physical Resources |                             | Y           |

| DMRS Support                  | Support                     | Y           |

| DMRS config type              | Type 1                      | Y           |

|                               | Type 2                      | Ν           |

| DMRS type A Pos               | Pos2                        | Y           |

|                               | Pos3                        | Y           |

| DMRS max length               | 1                           | Y           |

|                               | 2                           | Y           |

| DMRS Additional Position      | Pos0                        | Y           |

|                               | Pos1                        | Y           |

|                               | Pos2                        | Y           |

|                               | Pos3                        | Y           |

# Aerial CUDA-Accelerated RAN Overall Channel - PBCH (Physical Broadcast Channel)

# Aerial CUDA-Accelerated RAN Overall - PHY DL Reference Signals

#### PDSCH

| Feature                                                                | Configuration                 | Sup-<br>ported |

|------------------------------------------------------------------------|-------------------------------|----------------|

| Demodulation reference signals for PDSCH Sequence generation           |                               | Y              |

| Demodulation reference signals for PDSCH Mapping to physical resources | DM-RS configuration<br>type 1 | Y              |

|                                                                        | DM-RS configuration<br>type 2 | Ν              |

|                                                                        | DL-DMRS-max-len=1             | Y              |

|                                                                        | DL-DMRS-max-len=2             | Y              |

|                                                                        | DL-DMRS-add-pos=0             | Y              |

|                                                                        | DL-DMRS-add-pos=1             | Y              |

|                                                                        | DL-DMRS-add-pos=2             | Y              |

|                                                                        | DL-DMRS-add-pos=3             | Y              |

| Phase-tracking reference signals (PTRS) for PDSCH Mapping to physical  | LPT-RS=1                      | Ν              |

| resources                                                              | LPT-RS=2                      | Ν              |

|                                                                        | LPT-RS=4                      | Ν              |

#### PDCCH

| Feature                                                                | Configuration | Supported |

|------------------------------------------------------------------------|---------------|-----------|

| Demodulation reference signals for PDCCH Sequence generation           |               | Y         |

| Demodulation reference signals for PDCCH Mapping to physical resources |               | Y         |

# PBCH

| Feature                                             | Configuration                                                     | Supported |

|-----------------------------------------------------|-------------------------------------------------------------------|-----------|

| Demodulation reference signals for PBCH Se-         |                                                                   | Y         |

| quence generation                                   |                                                                   |           |

| Demodulation reference signals for PBCH Mapping     |                                                                   | Y         |

| to physical resources                               |                                                                   |           |

| CSI reference signals                               | 7                                                                 | V         |

| CSI reference signals                               | Zero-power                                                        | Y         |

| CSI reference signals Sequence generation           | non-zero-power                                                    | Y<br>Y    |

|                                                     | nID equals the higher-layer parameter ScramblingID                | I         |

| CSI reference signals Mapping to physical resources | Row 1: 1 port, Density = 3, CDMtype = No<br>CDM                   | Y         |

|                                                     | Row 2: 1 port, Density = 1, 0.5, CDMtype<br>= No CDM              | Y         |

|                                                     | Row 3: 2 port, Density = 1, 0.5, CDMtype<br>= FD-CDM2             | Y         |

|                                                     | Row 4: 4 port, Density = 1, CDMtype = FD-<br>CDM2                 | Y         |

|                                                     | Row 5: 4 port, Density = 1, CDMtype = FD-<br>CDM2                 | Y         |

|                                                     | Row 6: 8 port, Density = 1, CDMtype = FD-<br>CDM2                 | Y         |

|                                                     | Row 7: 8 port, Density = 1, CDMtype = FD-<br>CDM2                 | Y         |

|                                                     | Row 8: 8 port, Density = 1, CDMtype =<br>CDM4 (FD2, TD2)          | Y         |

|                                                     | Row 9: 12 port, Density = 1, CDMtype =<br>FD-CDM2                 | Ν         |

|                                                     | Row 10: 12 port, Density = 1, CDMtype =<br>CDM4 (FD2, TD2)        | N         |

|                                                     | Row 11: 16 port, Density = 1, 0.5, CDM-<br>type = $FD$ -CDM2      | Ν         |

|                                                     | Row 12: 16 port, Density = 1, 0.5, CDM-<br>type = CDM4 (FD2, TD2) | N         |

|                                                     | Row 13: 24 port, Density = 1, 0.5, CDM-<br>type = FD-CDM2         | N         |

|                                                     | Row 14: 24 port, Density = 1, 0.5, CDM-<br>type = CDM4(FD2, TD2)  | Ν         |

|                                                     | Row 15: 24 port, Density = 1, 0.5, CDM-<br>type = CDM8(FD2, TD4)  | Ν         |

|                                                     | Row 16: 32 port, Density = 1, 0.5, CDM-<br>type = $FD$ -CDM2      | N         |

|                                                     | Row 17: 32 port, Density = 1, 0.5, CDM-<br>type = CDM4(FD2, TD2)  | Ν         |

|                                                     | Row 18: 32 port, Density = 1, 0.5, CDM-<br>type = CDM8(FD2, TD4)  | Ν         |

RIM

| Feature                                                 | Configuration                                                | Sup-<br>ported |

|---------------------------------------------------------|--------------------------------------------------------------|----------------|

| RIM reference signal General                            | The first RIM-RS type can be used to convey in-<br>formation | Ν              |

|                                                         | The second RIM-RS type depends on configura-<br>tion only    | Ν              |

| RIM reference signal Sequence generation                |                                                              | Ν              |

| RIM reference signal Mapping to physical re-<br>sources |                                                              | Ν              |

| RIM reference signal RIM-RS configuration               | Enough Indication is disabled                                | Ν              |

|                                                         | Enough Indication is enabled                                 | Ν              |

| Positioning Reference                                   |                                                              |                |

| Positioning reference signal Sequence generation        |                                                              | Ν              |

| Positioning reference signal Mapping to physical        | LPRS = 2, Kcomb = 2                                          | Ν              |

| resources                                               | LPRS = 4, $Kcomb = 2$                                        | Ν              |

|                                                         | LPRS = 6, Kcomb = 2                                          | Ν              |

|                                                         | LPRS = 12, Kcomb = 2                                         | Ν              |

|                                                         | LPRS = 4, Kcomb = 4                                          | Ν              |

|                                                         | LPRS = 12, $Kcomb = 4$                                       | Ν              |

|                                                         | LPRS = 6, Kcomb = 6                                          | Ν              |

|                                                         | LPRS = 12, $Kcomb = 6$                                       | Ν              |

|                                                         | LPRS = 12, Kcomb = 12                                        | Ν              |

# Synchronization Signals

| Feature                           | Configuration                                                  | Sup-<br>ported |

|-----------------------------------|----------------------------------------------------------------|----------------|

| SSB numerology                    | 30 kHz                                                         | Y              |

| SSB precoding                     | supported                                                      | Y              |

| SSB burst set configuration       | 2 SS blocks w/ single SSB burst set                            | Y              |

| Synchronization signal generation | PSS generation and mapping to physical resources               | Y              |

|                                   | SSS generation and mapping to physical resources               | Y              |

| SS/PBCH block                     | Mapping of PSS within an SS/PBCH block                         | Y              |

|                                   | Mapping of SSS within an SS/PBCH block                         | Y              |

|                                   | Mapping of PBCH and DM-RS within an SS/PBCH block              | Y              |

|                                   | Time-frequency structure and time location of an SS/PBCH block | Y              |

# TS 38.212 Multiplexing and Channel Coding

# Aerial CUDA-Accelerated RAN Overall Multiplexing and Channel Coding

| Feature            | Configuration                                               | Supported |

|--------------------|-------------------------------------------------------------|-----------|

| General Procedures | CRC calculation<br>All CRC len supported<br>(6, 11, 16, 24) | Y         |

continues on next page

| Feature                                                  | Configuration                                                                                                                                                              | Supported |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|                                                          | Code block segmentation and code block<br>CRC attachment<br>• Polar coding<br>• Low density parity check coding                                                            | Y         |

| Transport to physical channel mapping - UL               | UL-SCH -> PUSCH                                                                                                                                                            | Y         |

|                                                          | RACH -> PRACH                                                                                                                                                              | Y         |

|                                                          | UCI -> PUCCH,PUSCH                                                                                                                                                         | Y         |

| Transport to physical channel mapping - DL               | DL-SCH -> PDSCH                                                                                                                                                            | Y         |

|                                                          | BCH -> PBCH                                                                                                                                                                | Y         |

|                                                          | PCH -> PDSCH                                                                                                                                                               | Y         |

|                                                          | DCI -> PDCCH                                                                                                                                                               | Y         |

| Channel coding schemes                                   | Polar coding                                                                                                                                                               | Y         |

|                                                          | Low density parity check coding (LDPC)                                                                                                                                     | Y         |

|                                                          | Channel coding of small block lengths                                                                                                                                      | Y         |

| Rate matching                                            | Rate matching for Polar code                                                                                                                                               | Y         |

| C C                                                      | Rate matching for LDPC code                                                                                                                                                | Y         |

|                                                          | Rate matching for channel coding of small block lengths                                                                                                                    | Y         |

| Code block concatenation                                 | <ul> <li>sequentially concatenating the rate matching<br/>outputs for the different code blocks</li> <li>LDPC</li> <li>Polar Coding</li> </ul>                             | Y         |

| uplink transport channels and control information        | Random access channel                                                                                                                                                      | Y         |

|                                                          | <ul> <li>Uplink shared channel</li> <li>LDPC graph selection</li> <li>Rate Matching</li> <li>Code block concatenation</li> <li>Data &amp; Control Mulitiplexing</li> </ul> | Y         |

|                                                          | Uplink control information<br>• Uplink control information on<br>PUCCH<br>• Uplink control information on<br>PUSCH                                                         | Y         |

| downlink transport channels and control informa-<br>tion | Broadcast channel                                                                                                                                                          | Y         |

|                                                          | Downlink shared channel and paging chan-<br>nel                                                                                                                            | Y         |

|                                                          | Downlink control information <ul> <li>DCI formats</li> <li>CRC attachment</li> <li>Channel coding</li> </ul>                                                               | Y         |

| UCI multiplexing on PUCCH                                | support muxing mode as per 38.212 - 6.3.1.1                                                                                                                                | Y         |

| Table | 5 - continued from | n previous page |

|-------|--------------------|-----------------|

|-------|--------------------|-----------------|

# TS 38.213 Physical Layer Procedures for Control

#### Aerial CUDA-Accelerated RAN Overall - PHY Control Procedures

# UE procedures (Not applicable to base station)

| Category                   | L1 requirement                                      | Supported |

|----------------------------|-----------------------------------------------------|-----------|

| Synchronization procedures | Cell search                                         | NA        |

|                            | Transmission timing adjustments                     | NA        |

|                            | Timing for secondary cell activation / deactivation | NA        |

| Radio link monitoring      | SSB based                                           | NA        |

|                            | CSI-RS based                                        | NA        |

| Link recovery procedures   | radio link failure                                  | NA        |

|                            | beam failure recovery                               | NA        |

| Uplink power control       | Physical uplink shared channel                      | NA        |

|                            | Physical uplink control channel                     | NA        |

|                            | Sounding reference signal                           | NA        |

|                            | Physical random access channel                      | NA        |

|                            | Power ramping counter suspention                    | NA        |

|                            | Dual connectivity                                   | NA        |

|                            | Power headroom report                               | NA        |

#### PHY RACH

| Category | L1 requirement                 | Supported |

|----------|--------------------------------|-----------|

|          | Type-1 random access procedure | Y         |

|          | Type-2 random access procedure | Ν         |

#### UE procedures (Not applicable to base station)

| Category                             | L1 requirement                                                            | Sup-<br>ported |

|--------------------------------------|---------------------------------------------------------------------------|----------------|

| HARQ-ACK codebook deter-<br>mination | CBG-based HARQ-ACK codebook determination                                 | NA             |

|                                      | Type-1 HARQ-ACK codebook determination in physical uplink control channel | NA             |

|                                      | Type-1 HARQ-ACK codebook determination in physical uplink shared channel  | NA             |

|                                      | Type-2 HARQ-ACK codebook determination in physical uplink control channel | NA             |

|                                      | Type-2 HARQ-ACK codebook determination in physical uplink shared channel  | NA             |

|                                      | Type-3 HARQ-ACK codebook determination                                    | NA             |

#### UCI reporting on PUSCH

| Category                                | L1 Requirement                                                                 | Sup-<br>ported |

|-----------------------------------------|--------------------------------------------------------------------------------|----------------|

| Short block codes for UCI               | Input: 1 - 11 bits output 32 bits                                              | Y              |

| Multiplexing of coded UCI bits to PUSCH | CSI part 1, support maximum 48 bit                                             | Y              |

|                                         | CSI part 1 and CSI part 2, support maximum 48 bit                              | Y              |

|                                         | Decoding UCI on PUSCH with PUSCH data (UCI-ON-PUSCH scaling) 0.5/0.65/0.8/1    | Ν              |

|                                         | Decoding UCI on PUSCH without PUSCH data (UCI-ON-PUSCH scaling) 0.5/0.65/0.8/1 | Ν              |

|                                         | HARQ information length maximum 128                                            | Y              |

|                                         | Semi-static offset                                                             | Ν              |

|                                         | Dynamic offset                                                                 | Ν              |

# UCI Reporting on PUCCH

| Category               | L1 Requirement                                          | Supported |

|------------------------|---------------------------------------------------------|-----------|

| UCI reporting on PUCCH | PUCCH Resource Sets before RRC connection establishment | Ν         |

|                        | PUCCH Resource Sets for RRC connected UE                | Ν         |

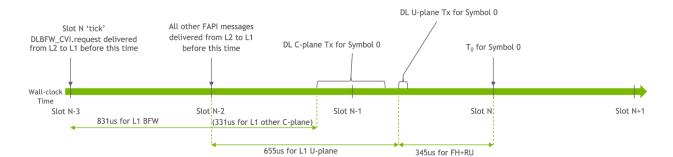

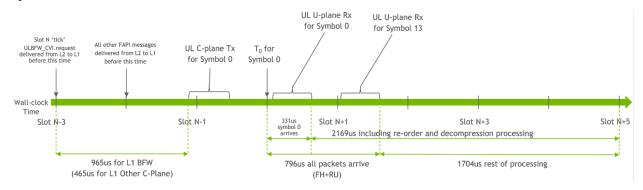

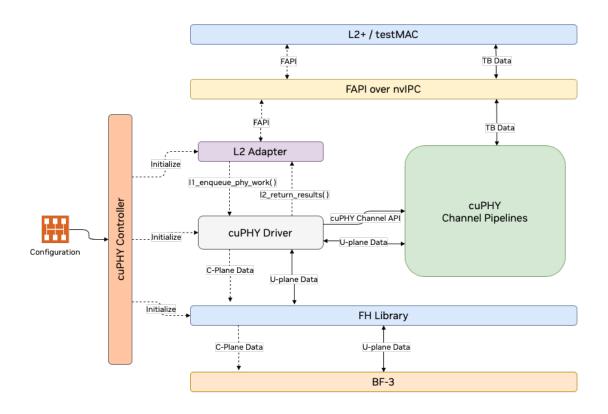

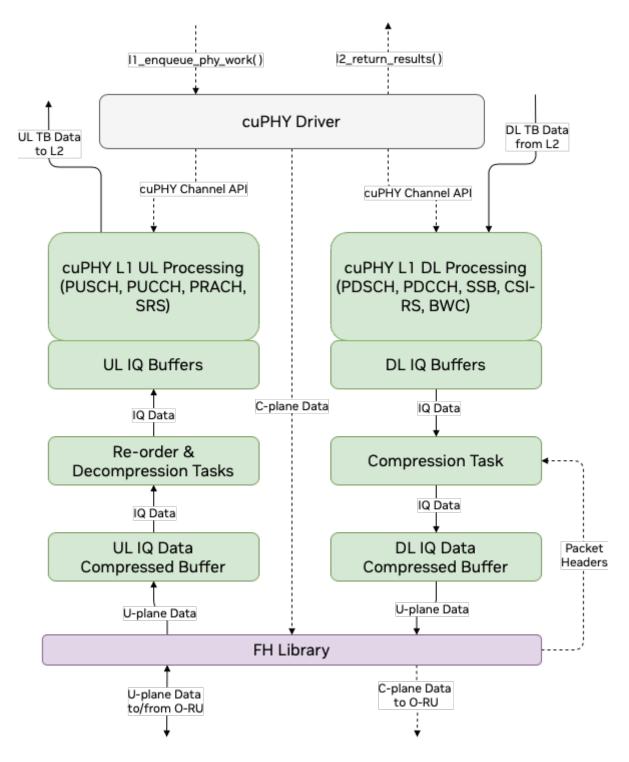

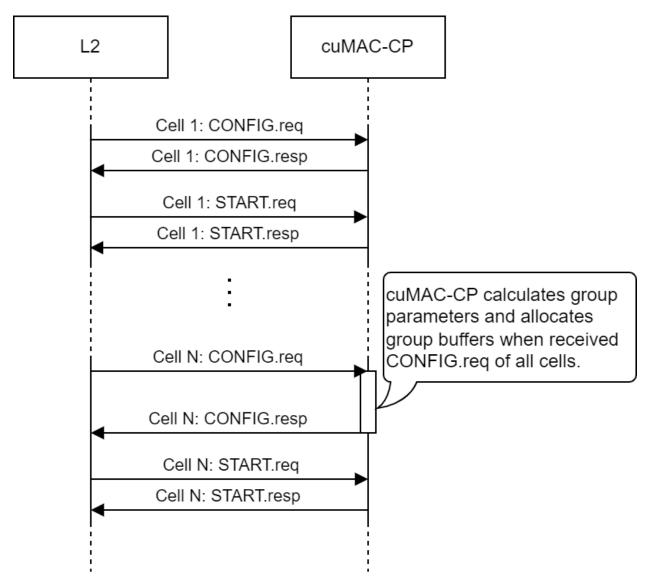

|                        | UE procedure for reporting multiple UCI types           | Ν         |