# NVIDIA Multi-Instance GPU User Guide

User Guide

## **Table of Contents**

| Chapter 1. Introduction                           | 1  |

|---------------------------------------------------|----|

| Chapter 2. Supported GPUs                         | 3  |

| Chapter 3. Supported Configurations               | 4  |

| Chapter 4. Virtualization                         | 5  |

| Chapter 5. Concepts                               | 6  |

| 5.1. Terminology                                  | 6  |

| 5.2. Partitioning                                 | 7  |

| 5.3. CUDA Concurrency Mechanisms                  | 12 |

| Chapter 6. Deployment Considerations              | 14 |

| 6.1. System Considerations                        | 14 |

| 6.2. Application Considerations                   | 15 |

| Chapter 7. MIG Device Names                       | 16 |

| 7.1. Device Enumeration                           | 17 |

| 7.2. CUDA Device Enumeration                      | 17 |

| Chapter 8. Supported MIG Profiles                 | 19 |

| 8.1. A30 MIG Profiles                             |    |

| 8.2. A100 MIG Profiles                            | 20 |

| 8.3. H100 MIG Profiles                            | 21 |

| 8.4. H200 MIG Profiles                            | 24 |

| Chapter 9. Getting Started with MIG               | 27 |

| 9.1. Prerequisites                                | 27 |

| 9.2. Enable MIG Mode                              | 27 |

| 9.2.1. GPU Reset on Hopper+ GPUs                  | 28 |

| 9.2.2. GPU Reset on Ampere GPUs                   |    |

| 9.2.3. Driver Clients                             |    |

| 9.3. List GPU Instance Profiles                   |    |

| 9.4. Creating GPU Instances                       |    |

| 9.5. Running CUDA Applications on Bare-Metal      |    |

| 9.5.1. GPU Instances                              |    |

| 9.5.2. Compute Instances                          |    |

| 9.6. Destroying GPU Instances                     |    |

| 9.7. Monitoring MIG Devices9.8. MIG with CUDA MPS |    |

| 9.9. Running CUDA Applications as Containers      |    |

| 5.5. Nationing CODA Applications as Containers    | 4∠ |

| 9.9.1. Install Docker                                  | 42 |

|--------------------------------------------------------|----|

| 9.9.2. Install NVIDIA Container Toolkit                | 42 |

| 9.9.3. Running Containers                              | 43 |

| 9.10. MIG with Kubernetes                              | 45 |

| 9.11. MIG with Slurm                                   | 45 |

| Chapter 10. Device Nodes and Capabilities              | 46 |

| 10.1. /dev based nvidia-capabilities                   | 47 |

| 10.2. /proc based nvidia-capabilities (**Deprecated**) | 50 |

| Chapter 11. Changelog                                  | 52 |

# Chapter 1. Introduction

The new Multi-Instance GPU (MIG) feature allows GPUs (starting with NVIDIA Ampere architecture) to be securely partitioned into up to seven separate GPU Instances for CUDA applications, providing multiple users with separate GPU resources for optimal GPU utilization. This feature is particularly beneficial for workloads that do not fully saturate the GPU's compute capacity and therefore users may want to run different workloads in parallel to maximize utilization.

For Cloud Service Providers (CSPs), who have multi-tenant use cases, MIG ensures one client cannot impact the work or scheduling of other clients, in addition to providing enhanced isolation for customers.

With MIG, each instance's processors have separate and isolated paths through the entire memory system - the on-chip crossbar ports, L2 cache banks, memory controllers, and DRAM address busses are all assigned uniquely to an individual instance. This ensures that an individual user's workload can run with predictable throughput and latency, with the same L2 cache allocation and DRAM bandwidth, even if other tasks are thrashing their own caches or saturating their DRAM interfaces. MIG can partition available GPU compute resources (including streaming multiprocessors or SMs, and GPU engines such as copy engines or decoders), to provide a defined quality of service (QoS) with fault isolation for different clients such as VMs, containers or processes. MIG enables multiple GPU Instances to run in parallel on a single, physical NVIDIA Ampere GPU.

With MIG, users will be able to see and schedule jobs on their new virtual GPU Instances as if they were physical GPUs. MIG works with Linux operating systems, supports containers using Docker Engine, with support for Kubernetes and virtual machines using hypervisors such as Red Hat Virtualization and VMware vSphere.

MIG supports the following deployment configurations:

- Bare-metal, including containers

- GPU pass-through virtualization to Linux quests on top of supported hypervisors

- vGPU on top of supported hypervisors

MIG allows multiple vGPUs (and thereby VMs) to run in parallel on a single GPU, while preserving the isolation guarantees that vGPU provides. For more information on GPU partitioning using vGPU and MIG, refer to the technical brief.

Figure 1. MIG Overview

# GPU Instance 1 -GPU Instance 2 -GPU Instance 3 -GPU Instance 4 — GPU Instance 5 —

#### MULTI-INSTANCE GPU ("MIG")

The purpose of this document is to introduce the concepts behind MIG, deployment considerations and provide examples of MIG management to demonstrate how users can run CUDA applications on MIG supported GPUs.

# Chapter 2. Supported GPUs

MIG is supported on GPUs starting with the NVIDIA Ampere generation (i.e. GPUs with compute capability >= 8.0). The following table provides a list of supported GPUs:

Table 1. Supported GPU Products

| Product          | Architecture     | Microarchitec | Compute<br>Capability | Memory Size | Max Number of Instances |

|------------------|------------------|---------------|-----------------------|-------------|-------------------------|

| H100-SXM5        | Hopper           | GH100         | 9.0                   | 80GB        | 7                       |

| H100-PCIE        | Hopper           | GH100         | 9.0                   | 80GB        | 7                       |

| H100-SXM5        | Hopper           | GH100         | 9.0                   | 94GB        | 7                       |

| H100-PCIE        | Hopper           | GH100         | 9.0                   | 94GB        | 7                       |

| H100 on<br>GH200 | Hopper           | GH100         | 9.0                   | 96GB        | 7                       |

| H200-SXM5        | Hopper           | GH100         | 9.0                   | 141GB       | 7                       |

| A100-SXM4        | NVIDIA<br>Ampere | GA100         | 8.0                   | 40GB        | 7                       |

| A100-SXM4        | NVIDIA<br>Ampere | GA100         | 8.0                   | 80GB        | 7                       |

| A100-PCIE        | NVIDIA<br>Ampere | GA100         | 8.0                   | 40GB        | 7                       |

| A100-PCIE        | NVIDIA<br>Ampere | GA100         | 8.0                   | 80GB        | 7                       |

| A30              | NVIDIA<br>Ampere | GA100         | 8.0                   | 24GB        | 4                       |

Additionally, MIG is supported on systems that include the supported products above such as DGX, DGX Station and HGX.

# Chapter 3. Supported Configurations

Supported deployment configurations with MIG include

- ▶ Bare-metal, including <u>containers</u> and <u>Kubernetes</u>

- GPU pass-through virtualization to Linux guests on top of supported hypervisors

- vGPU on top of supported hypervisors

# Chapter 4. Virtualization

MIG can be used with two types of virtualization:

- ▶ Under Linux guests on supported hypervisors, when MIG-supported GPUs are in GPU pass-through, the same workflows, tools and profiles available on bare-metal can be used.

- ▶ MIG allows multiple vGPUs (and thereby VMs) to run in parallel on a single MIGsupported GPU, while preserving the isolation guarantees that vGPU provides. To configure a GPU for use with vGPU VMs, refer to the chapter in the vGPU Software User Guide. Refer also to the technical brief for more information on GPU partitioning with vGPU.

# Chapter 5. Concepts

### 5.1. Terminology

This section introduces some terminology used to describe the concepts behind MIG.

#### Streaming Multiprocessor

A streaming multiprocessor (SM) executes compute instructions on the GPU.

#### **GPU Context**

A GPU context is analogous to a CPU process. It encapsulates all the resources necessary to execute operations on the GPU, including a distinct address space, memory allocations, etc. A GPU context has the following properties:

- Fault isolation

- Individually scheduled

- Distinct address space

#### **GPU** Engine

A GPU engine is what executes work on the GPU. The most commonly used engine is the Compute/Graphics engine that executes the compute instructions. Other engines include the copy engine (CE) that is responsible for performing DMAs, NVDEC for video decoding, NVENC for encoding, etc. Each engine can be scheduled independently and execute work for different GPU contexts.

#### **GPU Memory Slice**

A GPU memory slice is the smallest fraction of the GPU's memory, including the corresponding memory controllers and cache. A GPU memory slice is roughly one eighth of the total GPU memory resources, including both capacity and bandwidth.

#### **GPU SM Slice**

A GPU SM slice is the smallest fraction of the SMs on the GPU. A GPU SM slice is roughly one seventh of the total number of SMs available in the GPU when configured in MIG mode.

#### **GPU Slice**

A GPU slice is the smallest fraction of the GPU that combines a single GPU memory slice and a single GPU SM slice.

#### **GPU** Instance

A GPU Instance (GI) is a combination of GPU slices and GPU engines (DMAs, NVDECs, etc.). Anything within a GPU instance always shares all the GPU memory slices and other GPU engines, but it's SM slices can be further subdivided into compute instances (CI). A GPU instance provides memory QoS. Each GPU slice includes dedicated GPU memory resources which limit both the available capacity and bandwidth, and provide memory QoS. Each GPU memory slice gets 1/8 of the total GPU memory resources and each GPU SM slice gets 1/7 of the total number of SMs.

#### Compute Instance

A GPU instance can be subdivided into multiple compute instances. A Compute Instance (CI) contains a subset of the parent GPU instance's SM slices and other GPU engines (DMAs, NVDECs, etc.). The CIs share memory and engines.

### 5.2. Partitioning

Using the concepts introduced above, this section provides an overview of how the user can create various partitions on the GPU. For illustration purposes, the document will use the A100-40GB as an example, but the process is similar for other GPUs that support MIG.

#### **GPU Instance**

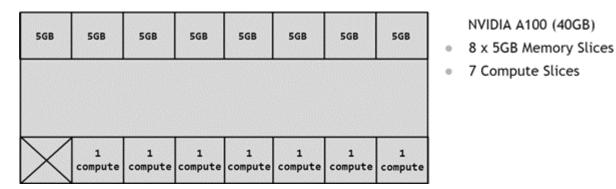

Partitioning of the GPU happens using memory slices, so the A100-40GB GPU can be thought of having 8x5GB memory slices and 7 SM slices as shown in the diagram below.

Figure 2. Available Slices on A100

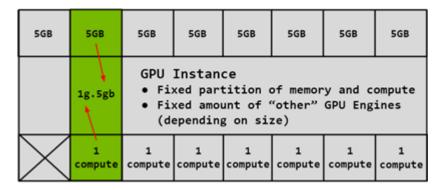

As explained above, then to create a GPU Instance (GI) requires combining some number of memory slices with some number of compute slices. In the diagram below, a 5GB memory slice is combined with 1 compute slice to create a 1g.5gb Gl profile:

Combining Memory and Compute Slices Figure 3.

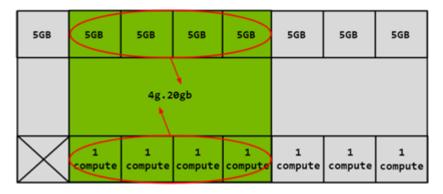

Similarly, 4x5GB memory slices can be combined with 4x1 compute slices to create the 4g.5gb GI profile:

Figure 4. Combining Memory and Compute Slices

#### **Compute Instance**

The compute slices of a GPU Instance can be further subdivided into multiple Compute Instances (CI), with the CIs sharing the engines and memory of the parent GI, but each CI has dedicated SM resources.

Using the same 4g.20gb example above, a CI may be created to consume only the first compute slice as shown below:

5GB 5GB 5GB 5GB 5GB 5GB 5GB 5GB 1c.4g.20gb compute compute compute ompute compute compute compute

Figure 5. Combining Memory and Compute Slices

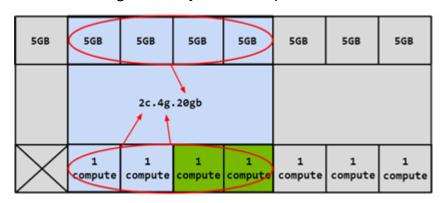

In this case, 4 different CIs can be created by choosing any of the compute slices. Two compute slices can also be combined together to create a 2c.4g.20gb profile:

Figure 6. Combining Memory and Compute Slices

In this example, 3 compute slices can also be combined to create a 3c.4q.20qb profile or all 4 can be combined to create a 4c.4g.20gb profile. When all 4 compute slices are combined, the profile is simply referred to as the 4g.20gb profile.

Refer to the sections on the canonical naming scheme and the CUDA device terminology.

#### Profile Placement

The number of slices that a GI can be created with is not arbitrary. The NVIDIA driver APIs provide a number of "GPU Instance Profiles" and users can create GIs by specifying one of these profiles.

On a given GPU, multiple GIs can be created from a mix and match of these profiles, so long as enough slices are available to satisfy the request.

#### Note:

The table below shows the profile names on the A100-SXM4-40GB product. For A100-SXM4-80GB, the profile names will change according to the memory proportion - for example, 1g.10gb, 2g.20gb, 3g.40gb, 4g.40gb, 7g.80gb respectively.

For a list of all supported combinations of profiles on MIG-enabled GPUs, refer to the section on supported profiles.

GPU Instance Profiles on A100 Table 2.

| Profile<br>Name      | Fraction of Memory | Fraction of SMs | Hardware<br>Units                | L2 Cache<br>Size | Copy<br>Engines | Number of<br>Instances<br>Available                        |

|----------------------|--------------------|-----------------|----------------------------------|------------------|-----------------|------------------------------------------------------------|

| MIG<br>1g.5gb        | 1/8                | 1/7             | 0<br>NVDECs /0<br>JPEG /0<br>OFA | 1/8              | 1               | 7                                                          |

| MIG<br>1g.5gb<br>+me | 1/8                | 1/7             | 1<br>NVDEC /1<br>JPEG /1<br>OFA  | 1/8              | 1               | 1 (A single 1g<br>profile can include<br>media extensions) |

| MIG<br>1g.10gb       | 1/8                | 1/7             | 1<br>NVDECs /0<br>JPEG /0<br>OFA | 1/8              | 1               | 4                                                          |

| MIG<br>2g.10gb       | 2/8                | 2/7             | 1<br>NVDECs /0<br>JPEG /0<br>OFA | 2/8              | 2               | 3                                                          |

| MIG<br>3g.20gb       | 4/8                | 3/7             | 2<br>NVDECs /0                   | 4/8              | 3               | 2                                                          |

| Profile<br>Name | Fraction of Memory | Fraction of SMs | Hardware<br>Units                | L2 Cache<br>Size | Copy<br>Engines | Number of<br>Instances<br>Available |

|-----------------|--------------------|-----------------|----------------------------------|------------------|-----------------|-------------------------------------|

|                 |                    |                 | JPEG /0<br>OFA                   |                  |                 |                                     |

| MIG<br>4g.20gb  | 4/8                | 4/7             | 2<br>NVDECs /0<br>JPEG /0<br>OFA | 4/8              | 4               | 1                                   |

| MIG<br>7g.40gb  | Full               | 7/7             | 5<br>NVDECs /1<br>JPEG /1<br>OFA | Full             | 7               | 1                                   |

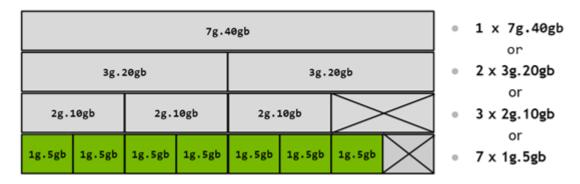

The diagram below shows a pictorial representation of how to build all valid combinations of GPU instances.

Figure 7. MIG Profiles on A100

In this diagram, a valid combination can be built by starting with an instance profile on the left and combining it with other instance profiles as you move to the right, such that no two profiles overlap vertically. For a list of all supported combinations and placements of profiles on A100 and A30, refer to the section on supported profiles.

Note that prior to NVIDIA driver release R510, the combination of a (4 memory, 4 compute) and a (4 memory, 3 compute) profile was not supported. This restriction no longer applies on newer drivers.

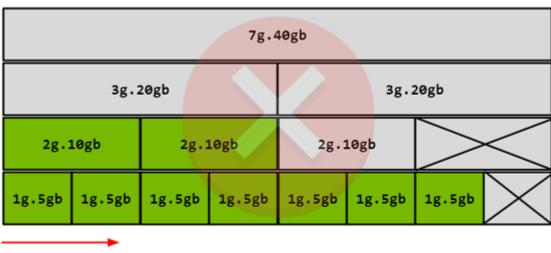

Profile Placements on A100 Figure 8.

### No Overlapping Verticals

Note that the diagram represents the physical layout of where the GPU Instances will exist once they are instantiated on the GPU. As GPU Instances are created and destroyed at different locations, fragmentation can occur, and the physical position of one GPU Instance will play a role in which other GPU Instances can be instantiated next to it.

#### 5.3. **CUDA Concurrency Mechanisms**

MIG has been designed to be largely transparent to CUDA applications - so that the CUDA programming model remains unchanged to minimize programming effort. CUDA already exposes multiple technologies for running work in parallel on the GPU and it is worthwhile showcasing how these technologies compare to MIG. Note that streams and MPS are part of the CUDA programming model and thus work when used with GPU Instances.

CUDA Streams are a CUDA Programming model feature where, in a CUDA application, different work can be submitted to independent queues and be processed independently by the GPU. CUDA streams can only be used within a single process and don't offer much isolation - the address space is shared, the SMs are shared, the GPU memory bandwidth, caches and capacity are shared. And lastly any errors affect all the streams and the whole process.

MPS is the CUDA Multi-Process service. It allows co-operative multi process applications to share compute resources on the GPU. It's commonly used by MPI jobs that cooperate, but it has also been used for sharing the GPU resources among unrelated applications, while accepting the challenges that such a solution brings. MPS currently does not offer error isolation between clients and while streaming multiprocessors used by each MPS client can be optionally limited to a percentage of all SMs, the scheduling hardware is still shared. Memory bandwidth, caches and capacity are all shared between MPS clients.

Lastly, MIG is the new form of concurrency offered by NVIDIA GPUs while addressing some of the limitations with the other CUDA technologies for running parallel work.

Table 3. **CUDA Concurrency Mechanisms**

|                             | Streams        | MPS                                   | MIG         |

|-----------------------------|----------------|---------------------------------------|-------------|

| Partition Type              | Single Process | Logical                               | Physical    |

| Max Partitions              | Unlimited      | 48                                    | 7           |

| SM Performance<br>Isolation | No             | Yes (by percentage, not partitioning) | Yes         |

| Memory Protection           | No             | Yes                                   | Yes         |

| Memory Bandwidth<br>QoS     | No             | No                                    | Yes         |

| Error Isolation             | No             | No                                    | Yes         |

| Cross-Partition<br>Interop  | Always         | IPC                                   | Limited IPC |

| Reconfigure                 | Dynamic        | Process Launch                        | When Idle   |

# Chapter 6. Deployment Considerations

MIG functionality is provided as part of the NVIDIA GPU driver.

- ▶ H100 GPUs are supported starting with CUDA 12/R525 drivers.

- A100 and A30 GPUs are supported starting with CUDA 11/R450 drivers.

### System Considerations

The following system considerations are relevant for when the GPU is in MIG mode.

MIG is supported only on Linux operating system distributions supported by CUDA. It is also recommended to use the latest NVIDIA Datacenter Linux. Refer to the quick start quide.

#### Note:

Also note the device nodes and nvidia-capabilities for exposing the MIG devices. The /proc mechanism for system-level interfaces is deprecated as of 450.51.06 and it is recommended to use the /dev based system-level interface for controlling access mechanisms of MIG devices through cgroups. This functionality is available starting with 450.80.02+ drivers.

- Supported configurations include

- Bare-metal, including containers

- GPU pass-through virtualization to Linux guests on top of supported hypervisors

- vGPU on top of supported hypervisors

MIG allows multiple vGPUs (and thereby VMs) to run in parallel on a single A100, while preserving the isolation guarantees that vGPU provides. For more information on GPU partitioning using vGPU and MIG, refer to the technical brief.

Setting MIG mode on the A100/A30 requires a GPU reset (and thus super-user privileges). Once the GPU is in MIG mode, instance management is then dynamic. Note that the setting is on a per-GPU basis.

- On NVIDIA Ampere GPUs, similar to ECC mode, MIG mode setting is persistent across. reboots until the user toggles the setting explicitly

- All daemons holding handles on driver modules need to be stopped before MIG enablement.

- This is true for systems such as DGX which may be running system health monitoring services such as nysm or GPU health monitoring or telemetry services such as DCGM.

- ▶ Toggling MIG mode requires the CAP SYS ADMIN capability. Other MIG management, such as creating and destroying instances, requires superuser by default, but can be delegated to non-privileged users by adjusting permissions to MIG capabilities in / proc/.

### **Application Considerations**

Users should note the following considerations when the A100 is in MIG mode:

- No graphics APIs are supported (e.g. OpenGL, Vulkan etc.)

- No GPU to GPU P2P (either PCIe or NVLink) is supported

- ▶ CUDA applications treat a Compute Instance and its parent GPU Instance as a single CUDA device. See this section on device enumeration by CUDA

- CUDA IPC across GPU instances is not supported. CUDA IPC across Compute instances is supported

- CUDA debugging (e.g. using cuda-gdb) and memory/race checking (e.g. using cudamemcheck or compute-sanitizer) is supported

- CUDA MPS is supported on top of MIG. The only limitation is that the maximum number of clients (48) is lowered proportionally to the Compute Instance size

- ▶ GPUDirect RDMA is supported when used from GPU Instances

# Chapter 7. MIG Device Names

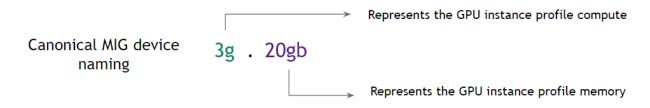

By default, a MIG device consists of a single "GPU Instance" and a single "Compute Instance". The table below highlights a naming convention to refer to a MIG device by its GPU Instance's compute slice count and its total memory in GB (rather than just its memory slice count).

When only a single CI is created (that consumes the entire compute capacity of the GI), then the CI sizing is implied in the device name.

Figure 9. MIG Device Name

#### Note:

The description below shows the profile names on the A100-SXM4-40GB product. For A100-SXM4-80GB, the profile names will change according to the memory proportion - for example, 1g.10gb, 2g.20gb, 3g.40gb, 4g.40gb, 7g.80gb respectively.

Table 4. Device names when using a single CI

| Memory              | 20gb        | 10gb    | 5gb    |

|---------------------|-------------|---------|--------|

| GPU Instance        | 3g          | 2g      | 1g     |

| Compute<br>Instance | 3c          | 2c      | 1c     |

| MIG Device          | 3g.20gb     | 2g.10gb | 1g.5gb |

|                     | GPC GPC GPC | GPC GPC | GPC    |

Each GI can be further sub-divided into multiple CIs as required by users depending on their workloads. The table below highlights what the name of a MIG device would look

like in this case. The example shown is for subdividing a 3q.20qb device into a set of subdevices with different Compute Instance slice counts.

Table 5. Device names when using multiple CIs

| Memory              |            | 20gb       |            | 20gb       |            |  |  |

|---------------------|------------|------------|------------|------------|------------|--|--|

| GPU Instance        |            | 3g         |            | 3g         |            |  |  |

| Compute<br>Instance | 1c         | 1c         | 1c         | 2c         | 1c         |  |  |

| MIG Device          | 1c.3g.20gb | 1c.3g.20gb | 1c.3g.20gb | 2c.3g.20gb | 1c.3g.20gb |  |  |

|                     | GPC        | GPC        | GPC        | GPC GPC    | GPC        |  |  |

#### **Device Enumeration** 7.1.

GPU Instances (GIs) and Compute Instances (CIs) are enumerated in the new /proc filesystem layout for MIG

```

$ ls -1 /proc/driver/nvidia-caps/

-r--r-- 1 root root 0 Nov 21 21:22 mig-minors

-r--r--r 1 root root 0 Nov 21 21:22 nvlink-minors

-r--r-- 1 root root 0 Nov 21 21:22 sys-minors

```

The corresponding device nodes (in mig-minors) are created under /dev/nvidia-caps. Refer to the chapter on device nodes and capabilities for more information.

#### 7.2. **CUDA Device Enumeration**

MIG supports running CUDA applications by specifying the CUDA device on which the application should be run. With CUDA 11/R450 and CUDA 12/R525, only enumeration of a single MIG instance is supported. In other words, regardless of how many MIG devices are created (or made available to a container), a single CUDA process can only enumerate a single MIG device.

CUDA applications treat a CI and its parent GI as a single CUDA device. CUDA is limited to use a single CI and will pick the first one available if several of them are visible. To summarize, there are two constraints:

- 1. CUDA can only enumerate a single compute instance

- 2. CUDA will not enumerate non-MIG GPU if any compute instance is enumerated on any other GPU

Note that these constraints may be relaxed in future NVIDIA driver releases for MIG.

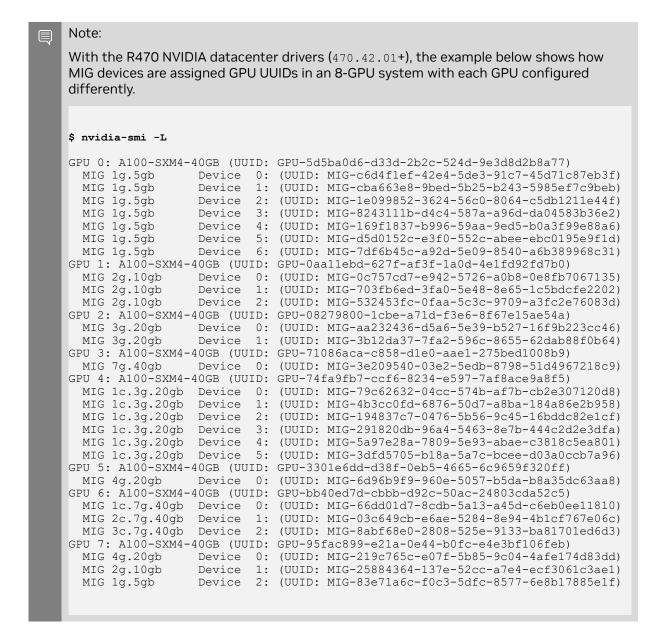

CUDA VISIBLE DEVICES has been extended to add support for MIG. Depending on the driver versions being used, two formats are supported:

- 1. With drivers >= R470 (470.42.01+), each MIG device is assigned a GPU UUID starting with MIG-<UUID>.

- 2. With drivers < R470 (e.g. R450 and R460), each MIG device is enumerated by specifying the CI and the corresponding parent GI. The format follows this convention: MIG-<GPU-UUID>/<GPU instance ID>/<compute instance ID>.

# Chapter 8. Supported MIG Profiles

This section provides an overview of the supported profiles and possible placements of the MIG profiles on supported GPUs.

### 8.1. A30 MIG Profiles

The following diagram shows the profiles supported on the NVIDIA A30:

Figure 10. Profiles on A30

| Config | GPC<br>Slice #0 | GPC<br>Slice #1 | GPC<br>Slice #2 | GPC<br>Slice #3 | OFA | NVDEC   | NVJPG | P2P | GPU Direct<br>RDMA |

|--------|-----------------|-----------------|-----------------|-----------------|-----|---------|-------|-----|--------------------|

| 1      |                 |                 | 4               |                 | 1   | 4       | 1     | No  | Supported          |

| 2      | :               | 2               |                 | 2               | 0   | 2+2     | 0     | No  | MemBW              |

| 3      | :               | 2               | 1               | 1               | 0   | 2+1+1   | 0     | No  | proportional       |

| 4      | 1               | 1               |                 | 2               | 0   | 1+1+2   | 0     | No  | to size of the     |

| 5      | 1               | 1               | 1               | 1               | 0   | 1+1+1+1 | 0     | No  | instance           |

The table below shows the supported profiles on the A30-24GB product.

Table 6. **GPU Instance Profiles on A30**

| Profile<br>Name      | Fraction of Memory | Fraction of SMs | Hardware<br>Units                | L2 Cache<br>Size | Copy<br>Engines | Number of<br>Instances<br>Available                        |

|----------------------|--------------------|-----------------|----------------------------------|------------------|-----------------|------------------------------------------------------------|

| MIG<br>1g.6gb        | 1/4                | 1/4             | 0<br>NVDECs /0<br>JPEG /0<br>OFA | 1/4              | 1               | 4                                                          |

| MIG<br>1g.6gb<br>+me | 1/4                | 1/4             | 1<br>NVDEC /1<br>JPEG /1<br>OFA  | 1/4              | 1               | 1 (A single 1g<br>profile can include<br>media extensions) |

| MIG<br>2g.12gb       | 2/4                | 2/4             | 2<br>NVDECs /0<br>JPEG /0<br>OFA | 2/4              | 2               | 2                                                          |

| Profile<br>Name       | Fraction of Memory | Fraction of SMs | Hardware<br>Units                | L2 Cache<br>Size | Copy<br>Engines | Number of<br>Instances<br>Available                        |

|-----------------------|--------------------|-----------------|----------------------------------|------------------|-----------------|------------------------------------------------------------|

| MIG<br>2g.12gb<br>+me | 2/4                | 2/4             | 2<br>NVDECs /1<br>JPEG /1<br>OFA | 2/4              | 2               | 1 (A single 2g<br>profile can include<br>media extensions) |

| MIG<br>4g.24gb        | Full               | 4/4             | 4<br>NVDECs /1<br>JPEG /1<br>OFA | Full             | 4               | 1                                                          |

#### Note:

The 1g.6gb+me profile is only available starting with R470 drivers.

The 2g.12gb+me profile is only available starting with R525 drivers.

#### 8.2. A 100 MIG Profiles

The following diagram shows the profiles supported on the NVIDIA A100:

Config GPU Direct RDMA OFA NVDEC NVJPG No 2 0 2+2 No 3 n 2+1+0 No 0 2+0+0+0 No 5 0 2+2 0 No 0 2+1+0 No 2+0+0+0 No 0 1+1+2 No Supported MemBW 1+0+0+2 No proportional to size of the 10 0 0+0+1+2 No 0+0+0+0+2 No instance 12 1+1+1+0 No 1 1+0+0+1+0 14 0 0+0+1+1+0 No 1+0+0+0+0 0+0+1+0+0+0 No 0+0+0+0+1+0 0+0+0+0+0+1

Profiles on A100 Figure 11.

The table below shows the supported profiles on the A100-SXM4-40GB product. For A100-SXM4-80GB, the profile names will change according to the memory proportion - for example, 1g.10gb, 1g.10gb+me, 1g.20gb, 2g.20gb, 3g.40gb, 4g.40gb, 7g.80gb respectively.

Table 7. **GPU Instance Profiles on A100**

| Profile<br>Name      | Fraction of<br>Memory | Fraction of SMs | Hardware<br>Units                | L2 Cache<br>Size | Copy<br>Engines | Number of<br>Instances<br>Available                        |

|----------------------|-----------------------|-----------------|----------------------------------|------------------|-----------------|------------------------------------------------------------|

| MIG<br>1g.5gb        | 1/8                   | 1/7             | 0<br>NVDECs /0<br>JPEG /0<br>OFA | 1/8              | 1               | 7                                                          |

| MIG<br>1g.5gb<br>+me | 1/8                   | 1/7             | 1<br>NVDEC /1<br>JPEG /1<br>OFA  | 1/8              | 1               | 1 (A single 1g<br>profile can include<br>media extensions) |

| MIG<br>1g.10gb       | 1/8                   | 1/7             | 1<br>NVDECs /0<br>JPEG /0<br>OFA | 1/8              | 1               | 4                                                          |

| MIG<br>2g.10gb       | 2/8                   | 2/7             | 1<br>NVDECs /0<br>JPEG /0<br>OFA | 2/8              | 2               | 3                                                          |

| MIG<br>3g.20gb       | 4/8                   | 3/7             | 2<br>NVDECs /0<br>JPEG /0<br>OFA | 4/8              | 3               | 2                                                          |

| MIG<br>4g.20gb       | 4/8                   | 4/7             | 2<br>NVDECs /0<br>JPEG /0<br>OFA | 4/8              | 4               | 1                                                          |

| MIG<br>7g.40gb       | Full                  | 7/7             | 5<br>NVDECs /1<br>JPEG /1<br>OFA | Full             | 7               | 1                                                          |

#### Note:

The 1g.5gb+me profile is only available starting with R470 drivers.

The 1g.10gb profile is only available starting with R525 drivers.

#### H100 MIG Profiles 8.3.

The following diagram shows the profiles supported on the NVIDIA H100:

Figure 12. Profiles on H100

| Config | GPC<br>Slice #0 | GPC<br>Slice #1 | GPC<br>Slice #2 | GPC<br>Slice #3 | GPC<br>Slice #4 | GPC<br>Slice #5 | GPC<br>Slice #6 | OFA | NVDEC         | NVJPG         | P2P | GPU Direct<br>RDMA |

|--------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----|---------------|---------------|-----|--------------------|

| 1      |                 |                 |                 | 7               |                 |                 |                 | 1   | 7             | 7             | No  |                    |

| 2      |                 |                 | 4               |                 |                 | 3               |                 | 0   | 4+3           | 4+3           | No  | 1                  |

| 3      |                 |                 | 4               |                 |                 | 2               | 1               | 0   | 4+2+1         | 4+2+1         | No  | 1                  |

| 4      |                 |                 | 4               |                 | 1               | 1               | 1               | 0   | 4+1+1+1       | 4+1+1+1       | No  | 1                  |

| 5      |                 | 3               |                 |                 | 3               |                 |                 | 0   | 3+3           | 3+3           | No  | 1                  |

| 6      |                 | 3               |                 | :               | 2               | 1               |                 | 0   | 3+2+1         | 3+2+1         | No  | 1                  |

| 7      |                 | 3               |                 | 1               | 1               | 1               |                 | 0   | 3+1+1+1       | 3+1+1+1       | No  | 1                  |

| 8      |                 | 2               |                 | 2               |                 | 3               |                 | 0   | 2+2+3         | 2+2+3         | No  | Supported          |

| 9      |                 | 2               | 1               | 1               |                 | 3               |                 | 0   | 2+1+1+3       | 2+1+1+3       | No  | MemBW              |

| 10     | 1               | 1               | :               | 2               |                 | 3               |                 | 0   | 1+1+2+3       | 1+1+2+3       | No  | proportional       |

| 11     | 1               | 1               | 1               | 1               |                 | 3               |                 | 0   | 1+1+1+1+3     | 1+1+1+1+3     | No  | to size of the     |

| 12     |                 | 2               | :               | 2               |                 | 2               | 1               | 0   | 2+2+2+2+1     | 2+2+2+2+1     | No  | instance           |

| 13     |                 | 2               | 1               | 1               |                 | 2               | 1               | 0   | 2+1+1+2+1     | 2+1+1+2+1     | No  | 1                  |

| 14     | 1               | 1               | :               | 2               |                 | 2               | 1               | 0   | 1+1+2+2+1     | 1+1+2+2+1     | No  | 1                  |

| 15     |                 | 2               | 1               | 1               | 1               | 1               | 1               | 0   | 2+1+1+1+1+1   | 2+1+1+1+1     | No  | 1                  |

| 16     | 1               | 1               | :               | 2               | 1               | 1               | 1               | 0   | 1+1+2+1+1+1   | 1+1+2+1+1+1   | No  |                    |

| 17     | 1               | 1               | 1               | 1               |                 | 2               | 1               | 0   | 1+1+1+1+2+1   | 1+1+1+1+2+1   | No  |                    |

| 18     | 1               | 1               | 1               | 1               | 1               |                 | 2               | 0   | 1+1+1+1+1+2   | 1+1+1+1+1+2   | No  | 1                  |

| 19     | 1               | 1               | 1               | 1               | 1               | 1               | 1               | 0   | 1+1+1+1+1+1+1 | 1+1+1+1+1+1+1 | No  | ]                  |

The table below shows the supported profiles on the H100 80GB product (PCIe and SXM5).

Table 8. GPU Instance Profiles on H100

| Profile<br>Name       | Fraction of<br>Memory | Fraction of SMs | Hardware<br>Units                  | L2 Cache<br>Size | Copy<br>Engines | Number of<br>Instances<br>Available                        |

|-----------------------|-----------------------|-----------------|------------------------------------|------------------|-----------------|------------------------------------------------------------|

| MIG<br>1g.10gb        | 1/8                   | 1/7             | 1<br>NVDECs / 1<br>JPEG / 0<br>OFA | 1/8              | 1               | 7                                                          |

| MIG<br>1g.10gb<br>+me | 1/8                   | 1/7             | 1<br>NVDEC /1<br>JPEG /1<br>OFA    | 1/8              | 1               | 1 (A single 1g<br>profile can include<br>media extensions) |

| MIG<br>1g.20gb        | 1/4                   | 1/7             | 1<br>NVDECs / 1<br>JPEG / 0<br>OFA | 1/8              | 1               | 4                                                          |

| MIG<br>2g.20gb        | 2/8                   | 2/7             | 2<br>NVDECs /2<br>JPEG /0<br>OFA   | 2/8              | 2               | 3                                                          |

| MIG<br>3g.40gb        | 4/8                   | 3/7             | 3<br>NVDECs /3<br>JPEG /0<br>OFA   | 4/8              | 3               | 2                                                          |

| MIG<br>4g.40gb        | 4/8                   | 4/7             | 4<br>NVDECs /4<br>JPEG /0<br>OFA   | 4/8              | 4               | 1                                                          |

| Profile<br>Name | Fraction of Memory | Fraction of SMs | Hardware<br>Units                | L2 Cache<br>Size | Copy<br>Engines | Number of<br>Instances<br>Available |

|-----------------|--------------------|-----------------|----------------------------------|------------------|-----------------|-------------------------------------|

| MIG<br>7g.80gb  | Full               | 7/7             | 7<br>NVDECs /7<br>JPEG /1<br>OFA | Full             | 8               | 1                                   |

The table below shows the supported profiles on the H100 94GB product (PCIe and SXM5).

| Profile<br>Name       | Fraction of<br>Memory | Fraction of SMs | Hardware<br>Units                | L2 Cache<br>Size | Copy<br>Engines | Number of<br>Instances<br>Available                              |

|-----------------------|-----------------------|-----------------|----------------------------------|------------------|-----------------|------------------------------------------------------------------|

| MIG<br>1g.12gb        | 1/8                   | 1/7             | 1<br>NVDECs /1<br>JPEG /0<br>OFA | 1/8              | 1               | 7                                                                |

| MIG<br>1g.12gb<br>+me | 1/8                   | 1/7             | 1 NVDEC /1<br>JPEG /1<br>OFA     | 1/8              | 1               | 1 (A single<br>1g profile<br>can include<br>media<br>extensions) |

| MIG<br>1g.24gb        | 1/4                   | 1/7             | 1<br>NVDECs /1<br>JPEG /0<br>OFA | 1/8              | 1               | 4                                                                |

| MIG<br>2g.24gb        | 2/8                   | 2/7             | 2<br>NVDECs /2<br>JPEG /0<br>OFA | 2/8              | 2               | 3                                                                |

| MIG<br>3g.47gb        | 4/8                   | 3/7             | 3<br>NVDECs /3<br>JPEG /0<br>OFA | 4/8              | 3               | 2                                                                |

| MIG<br>4g.47gb        | 4/8                   | 4/7             | 4<br>NVDECs /4<br>JPEG /0<br>OFA | 4/8              | 4               | 1                                                                |

| MIG<br>7g.94gb        | Full                  | 7/7             | 7<br>NVDECs /7<br>JPEG /1<br>OFA | Full             | 8               | 1                                                                |

The table below shows the supported profiles on the H100 96GB product (H100 on GH200).

| Profile<br>Name       | Fraction of Memory | Fraction of SMs | Hardware<br>Units                | L2 Cache<br>Size | Copy<br>Engines | Number of<br>Instances<br>Available                              |

|-----------------------|--------------------|-----------------|----------------------------------|------------------|-----------------|------------------------------------------------------------------|

| MIG<br>1g.12gb        | 1/8                | 1/7             | 1<br>NVDECs /1<br>JPEG /0<br>OFA | 1/8              | 1               | 7                                                                |

| MIG<br>1g.12gb<br>+me | 1/8                | 1/7             | 1 NVDEC /1<br>JPEG /1<br>OFA     | 1/8              | 1               | 1 (A single<br>1g profile<br>can include<br>media<br>extensions) |

| MIG<br>1g.24gb        | 1/4                | 1/7             | 1<br>NVDECs /1<br>JPEG /0<br>OFA | 1/8              | 1               | 4                                                                |

| MIG<br>2g.24gb        | 2/8                | 2/7             | 2<br>NVDECs /2<br>JPEG /0<br>OFA | 2/8              | 2               | 3                                                                |

| MIG<br>3g.48gb        | 4/8                | 3/7             | 3<br>NVDECs /3<br>JPEG /0<br>OFA | 4/8              | 3               | 2                                                                |

| MIG<br>4g.48gb        | 4/8                | 4/7             | 4<br>NVDECs /4<br>JPEG /0<br>OFA | 4/8              | 4               | 1                                                                |

| MIG<br>7g.96gb        | Full               | 7/7             | 7<br>NVDECs /7<br>JPEG /1<br>OFA | Full             | 8               | 1                                                                |

### 8.4. H200 MIG Profiles

The following diagram shows the profiles supported on the NVIDIA H200:

Figure 13. Profiles on H200

| Config | GPC      | OFA | NVDEC         | NVJPG         | P2P   | GPU Direct              |

|--------|----------|----------|----------|----------|----------|----------|----------|-----|---------------|---------------|-------|-------------------------|

|        | Slice #0 | Slice #1 | Slice #2 | Slice #3 | Slice #4 | Slice #5 | Slice #6 | OIA | NVDLC         | NVSFG         | F 2 F | RDMA                    |

| 1      |          |          |          | 7        |          |          |          | 1   | 7             | 7             | No    |                         |

| 2      |          |          | 4        |          |          | 3        |          | 0   | 4+3           | 4+3           | No    |                         |

| 3      |          |          | 4        |          |          | 2        | 1        | 0   | 4+2+1         | 4+2+1         | No    |                         |

| 4      |          |          | 4        |          | 1        | 1        | 1        | 0   | 4+1+1+1       | 4+1+1+1       | No    |                         |

| 5      |          | 3        |          |          | 3        |          |          | 0   | 3+3           | 3+3           | No    |                         |

| 6      |          | 3        |          |          | 2        | 1        |          | 0   | 3+2+1         | 3+2+1         | No    |                         |

| 7      |          | 3        |          | 1        | 1        | 1        |          | 0   | 3+1+1+1       | 3+1+1+1       | No    |                         |

| 8      |          | 2        |          | 2        |          | 3        |          | 0   | 2+2+3         | 2+2+3         | No    | Supported               |

| 9      |          | 2        | 1        | 1        |          | 3        |          | 0   | 2+1+1+3       | 2+1+1+3       | No    | MemBW                   |

| 10     | 1        | 1        |          | 2        |          | 3        |          | 0   | 1+1+2+3       | 1+1+2+3       | No    | proportional            |

| 11     | 1        | 1        | 1        | 1        |          | 3        |          | 0   | 1+1+1+1+3     | 1+1+1+1+3     | No    | to size of the instance |

| 12     |          | 2        |          | 2        |          | 2        | 1        | 0   | 2+2+2+2+1     | 2+2+2+2+1     | No    | llistance               |

| 13     |          | 2        | 1        | 1        |          | 2        | 1        | 0   | 2+1+1+2+1     | 2+1+1+2+1     | No    |                         |

| 14     | 1        | 1        |          | 2        |          | 2        | 1        | 0   | 1+1+2+2+1     | 1+1+2+2+1     | No    |                         |

| 15     |          | 2        | 1        | 1        | 1        | 1        | 1        | 0   | 2+1+1+1+1+1   | 2+1+1+1+1     | No    |                         |

| 16     | 1        | 1        |          | 2        | 1        | 1        | 1        | 0   | 1+1+2+1+1+1   | 1+1+2+1+1+1   | No    |                         |

| 17     | 1        | 1        | 1        | 1        |          | 2        | 1        | 0   | 1+1+1+1+2+1   | 1+1+1+1+2+1   | No    |                         |

| 18     | 1        | 1        | 1        | 1        | 1        |          | 2        | 0   | 1+1+1+1+1+2   | 1+1+1+1+1+2   | No    |                         |

| 19     | 1        | 1        | 1        | 1        | 1        | 1        | 1        | 0   | 1+1+1+1+1+1+1 | 1+1+1+1+1+1+1 | No    |                         |

The table below shows the supported profiles on the H200 141GB product.

GPU Instance Profiles on H200 Table 9.

| Profile<br>Name       | Fraction of Memory | Fraction of SMs | Hardware<br>Units                  | L2 Cache<br>Size | Copy<br>Engines | Number of<br>Instances<br>Available                        |

|-----------------------|--------------------|-----------------|------------------------------------|------------------|-----------------|------------------------------------------------------------|

| MIG<br>1g.18gb        | 1/8                | 1/7             | 1<br>NVDECs / 1<br>JPEG / 0<br>OFA | 1/8              | 1               | 7                                                          |

| MIG<br>1g.18gb<br>+me | 1/8                | 1/7             | 1<br>NVDEC /1<br>JPEG /1<br>OFA    | 1/8              | 1               | 1 (A single 1g<br>profile can include<br>media extensions) |

| MIG<br>1g.35gb        | 1/4                | 1/7             | 1<br>NVDECs /1<br>JPEG /0<br>OFA   | 1/8              | 1               | 4                                                          |

| MIG<br>2g.35gb        | 2/8                | 2/7             | 2<br>NVDECs /2<br>JPEG /0<br>OFA   | 2/8              | 2               | 3                                                          |

| MIG<br>3g.71gb        | 4/8                | 3/7             | 3<br>NVDECs /3<br>JPEG /0<br>OFA   | 4/8              | 3               | 2                                                          |

| MIG<br>4g.71gb        | 4/8                | 4/7             | 4<br>NVDECs /4<br>JPEG /0<br>OFA   | 4/8              | 4               | 1                                                          |

| Profile<br>Name | Fraction of Memory | Fraction of SMs | Hardware<br>Units                | L2 Cache<br>Size | Copy<br>Engines | Number of<br>Instances<br>Available |

|-----------------|--------------------|-----------------|----------------------------------|------------------|-----------------|-------------------------------------|

| MIG<br>7g.141gb | Full               | 7/7             | 7<br>NVDECs /7<br>JPEG /1<br>OFA | Full             | 8               | 1                                   |

# Chapter 9. Getting Started with MIG

### 9.1. Prerequisites

The following prerequisites and minimum software versions are recommended when using supported GPUs in MIG mode.

- MIG is supported only on GPUs and systems listed here

- It is recommended to install the latest NVIDIA datacenter driver. The minimum versions are provided below:

- ▶ If using H100, then CUDA 12 and NVIDIA driver R525 ( >= 525.53) or later

- ▶ If using A100/A30, then CUDA 11 and NVIDIA driver R450 ( >= 450.80.02) or later

- Linux operating system distributions supported by CUDA

- If running containers or using Kubernetes, then:

- NVIDIA Container Toolkit (nvidia-docker2): v2.5.0 or later

- NVIDIA K8s Device Plugin: v0.7.0 or later

- NVIDIA gpu-feature-discovery: v0.2.0 or later

MIG can be managed programmatically using NVIDIA Management Library (NVML) APIs or its command-line-interface, nvidia-smi. Note that for brevity, some of the nvidiasmi output in the following examples may be cropped to showcase the relevant sections of interest.

For more information on the MIG commands, see the nvidia-smi man page or nvidiasmi mig --help. For information on the MIG management APIs, see the NVML header (nvml.h) included in the CUDA Toolkit packages (cuda-nvml-dev-\*; installed under /usr/ local/cuda/include/nvml.h) For automated tooling support with configuring MIG, refer to the NVIDIA MIG Partition Editor (or mig-parted) tools.

### 9.2. Enable MIG Mode

By default, MIG mode is not enabled on the GPU. For example, running nvidia-smi shows that MIG mode is disabled:

|                |                 |             |                   |                   |         |                        |                | UDA Versio           | on: 11.0                          |

|----------------|-----------------|-------------|-------------------|-------------------|---------|------------------------|----------------|----------------------|-----------------------------------|

| GPU 1<br>Fan 1 | Name<br>Temp Pe | Pe<br>rf Pv | ersiste<br>wr:Usa | ence-M <br>ge/Cap | Bus-Id  | Di<br>Memory-U         | sp.A  <br>sage | Volatile<br>GPU-Util | Uncorr. ECC<br>Compute M<br>MIG M |

| 0 <i>I</i>     | A100-SXM        | 4-40GE      | 3                 | Off               | 0000000 | 0:36:00.0<br>iB / 4053 | Off            |                      | (                                 |

MIG mode can be enabled on a per-GPU basis with the following command: nvidia-smi -i <GPU IDs> -mig 1. The GPUs can be selected using comma separated GPU indexes, PCI Bus Ids or UUIDs. If no GPU ID is specified, then MIG mode is applied to all the GPUs on the system.

When MIG is enabled on the GPU, depending on the GPU product, the driver will attempt to reset the GPU so that MIG mode can take effect.

```

$ sudo nvidia-smi -i 0 -mig 1

Enabled MIG Mode for GPU 00000000:36:00.0

All done.

$ nvidia-smi -i 0 --query-gpu=pci.bus_id,mig.mode.current --format=csv

pci.bus id, mig.mode.current

00000000:36:00.0, Enabled

```

### **GPU Reset on Hopper+ GPUs**

Starting with the Hopper generation of GPUs, enabling MIG mode no longer requires a GPU reset to take effect (and thus the driver does not attempt to reset the GPU in the background).

Note that MIG mode (Disabled or Enabled states) is only persistent as long as the driver is resident in the system (i.e. the kernel modules are loaded). MIG mode is no longer persistent across system reboots (there is no longer a status bit stored in the GPU InfoROM).

Thus, an unload and reload of the driver kernel modules will disable MIG mode.

### **GPU Reset on Ampere GPUs**

On NVIDIA Ampere GPUs, when MIG mode is enabled, the driver will attempt to reset the GPU so that MIG mode can take effect.

Note that MIG mode (Disabled or Enabled states) is persistent across system reboots (there is a status bit stored in the GPU InfoROM). Thus MIG mode has to be explicitly disabled to return the GPU to its default state.

Note:

If you are using MIG inside a VM with NVIDIA Ampere GPUs (A100 or A30) in passthrough, then you may need to reboot the VM to allow the GPU to be in MIG mode as in some cases, GPU reset is not allowed via the hypervisor for security reasons. This can be seen in the following example:

```

$ sudo nvidia-smi -i 0 -mig 1

Warning: MIG mode is in pending enable state for GPU 00000000:00:03.0:Not

Reboot the system or try nvidia-smi --qpu-reset to make MIG mode effective on

GPU 00000000:00:03.0

All done.

$ sudo nvidia-smi --gpu-reset

Resetting GPU 00000000:00:03.0 is not supported.

```

#### 9.2.3. Driver Clients

In some cases, if you have agents on the system (e.g. monitoring agents) that use the GPU, then you may not be able to initiate a GPU reset. For example, on DGX systems, you may encounter the following message:

```

$ sudo nvidia-smi -i 0 -mig 1

Warning: MIG mode is in pending enable state for GPU 00000000:07:00.0:In use by

another client

00000000:07:00.0 is currently being used by one or more other processes (e.g. CUDA

application or a monitoring application such as another instance of nvidia-smi).

Please first kill all processes using the device and retry the command or reboot

the system to make MIG mode effective.

All done.

```

In this specific DGX example, you would have to stop the nvsm and dcgm services, enable MIG mode on the desired GPU and then restore the monitoring services:

```

$ sudo systemctl stop nvsm

$ sudo systemctl stop dcgm

$ sudo nvidia-smi -i 0 -mig 1

Enabled MIG Mode for GPU 0000000:07:00.0

All done.

```

The examples shown in the document use super-user privileges. As described in the <u>Device Nodes</u> section, granting read access to mig/config capabilities allows nonroot users to manage instances once the GPU has been configured into MIG mode. The default file permissions on the mig/config file is shown below.

```

$ ls -1 /proc/driver/nvidia/capabilities/*

/proc/driver/nvidia/capabilities/mig:

total 0

-r----- 1 root root 0 May 24 16:10 config

-r--r-- 1 root root 0 May 24 16:10 monitor

```

#### List GPU Instance Profiles 9.3.

The NVIDIA driver provides a number of profiles that users can opt-in for when configuring the MIG feature in A100. The profiles are the sizes and capabilities of the GPU instances that can be created by the user. The driver also provides information about the placements, which indicate the type and number of instances that can be created.

| GPU | Nam | nce profiles:<br>ne | ID | Instances<br>Free/Total | Memory<br>GiB | P2P | SM<br>CE | DEC<br>JPEG | ENC<br>OFA |

|-----|-----|---------------------|----|-------------------------|---------------|-----|----------|-------------|------------|

|     |     | 1g.5gb              | 19 | 7/7                     | 4.75          | No  | 14<br>1  | 0<br>0      | 0<br>0     |

| 0   | MIG | 1g.5gb+me           | 20 | 1/1                     | 4.75          | No  | 14<br>1  | 1<br>1      | 0<br>1     |

| 0   | MIG | 1g.10gb             | 15 | 4/4                     | 9.62          | No  | 14<br>1  | 1<br>0      | 0<br>0     |

| 0   | MIG | 2g.10gb             | 14 | 3/3                     | 9.62          | No  | 28<br>2  | 1<br>0      | 0<br>0     |

| 0   | MIG | 3g.20gb             | 9  | 2/2                     | 19.50         | No  | 42<br>3  | 2           | 0          |

| 0   | MIG | 4g.20gb             | 5  | 1/1                     | 19.50         | No  | 56<br>4  | 2<br>0      | 0<br>0     |

| 0   | MIG | 7g.40gb             | 0  | 1/1                     | 39.25         | No  | 98<br>7  | 5<br>1      | 0<br>1     |

List the possible placements available using the following command. The syntax of the placement is {<index>}:<GPU Slice Count> and shows the placement of the instances on the GPU. The placement index shown indicates how the profiles are mapped on the GPU as shown in the supported profiles tables.

```

$ nvidia-smi mig -lgipp

GPU 0 Profile ID 19 Placements: {0,1,2,3,4,5,6}:1

GPU 0 Profile ID 20 Placements: {0,1,2,3,4,5,6}:1

0 Profile ID 15 Placements: {0,2,4,6}:2

GPU 0 Profile ID 14 Placements: {0,2,4}:2

GPU 0 Profile ID 9 Placements: {0,4}:4

GPU 0 Profile ID 5 Placement: {0}:4

GPU 0 Profile ID 0 Placement : {0}:8

```

The command shows that the user can create two instances of type 3g.20gb (profile ID 9) or seven instances of 1q.5qb (profile ID 19).

#### **Creating GPU Instances** 9.4

Before starting to use MIG, the user needs to create GPU instances using the -cgi option. One of three options can be used to specify the instance profiles to be created:

- 1. Profile ID (e.g. 9, 14, 5)

- 2. Short name of the profile (e.g. 3g.20gb

- 3. Full profile name of the instance (e.g. MIG 3g.20gb)

Once the GPU instances are created, one needs to create the corresponding Compute Instances (CI). By using the -c option, nvidia-smi creates these instances.

#### Note:

Without creating GPU instances (and corresponding compute instances), CUDA workloads cannot be run on the GPU. In other words, simply enabling MIG mode on the GPU is not sufficient. Also note that, the created MIG devices are not persistent across system reboots. Thus, the user or system administrator needs to recreate the desired MIG configurations if the GPU or system is reset. For automated tooling support for this purpose, refer to the NVIDIA MIG Partition Editor (or mig-parted) tool, including creating a systemd service that could recreate the MIG geometry at system startup.

The following example shows how the user can create GPU instances (and corresponding compute instances). In this example, the user can create two GPU instances (of type 3g.20gb), with each GPU instance having half of the available compute and memory capacity. In this example, we purposefully use profile ID and short profile name to showcase how either option can be used:

```

$ sudo nvidia-smi mig -cgi 9,3g.20gb -C

Successfully created GPU instance ID 2 on GPU 0 using profile MIG 3g.20gb (ID 9)

Successfully created compute instance ID 0 on GPU 0 GPU instance ID 2 using profile MIG 3g.20gb (ID 2)

Successfully created GPU instance ID 1 on GPU 0 using profile MIG 3g.20gb (ID

Successfully created compute instance ID 0 on GPU 0 GPU instance ID 1 using

profile MIG 3g.20gb (ID 2)

```

Now list the available GPU instances:

```

$ sudo nvidia-smi mig -lgi

| 0 MIG 3g.20gb 9 1 4:4

0 MIG 3g.20gb 9 2 0:4

```

Now verify that the GIs and corresponding CIs are created:

| IG devices:                  | +                |              | 1                   |    |     |              |       |          |

|------------------------------|------------------|--------------|---------------------|----|-----|--------------|-------|----------|

| GPU GI CI MIO                | Memory-Usage     | <br>  SM<br> | Vol <br>Unc <br>ECC | CE | ENC | Share<br>DEC | OFA   | JPG      |

| 0 1 0 0                      | 11MiB / 20224MiB | 42           | 0                   | 3  | 0   | 2            |       | 0        |

| 0 2 0 1                      | 11MiB / 20096MiB | 42           | 0                   | 3  | 0   | 2            |       | 0        |

| Processes:  GPU GI CI  ID ID | PID Type Proce   |              |                     |    |     |              | U Mem | <br>lory |

#### Instance Geometry

As described in the section on Partitioning, the NVIDIA driver APIs provide a number of available GPU Instance profiles that can be chosen by the user.

If a mixed geometry of the profiles is specified by the user, then the NVIDIA driver chooses the placement of the various profiles. This can be seen in the following examples.

Example 1: Creation of a 4-2-1 geometry. After the instances are created, the placement of the profiles can be observed:

```

$ sudo nvidia-smi mig -cgi 19,14,5

Successfully created GPU instance ID 13 on GPU 0 using profile MIG 1g.5gb (ID 19) Successfully created GPU instance ID 5 on GPU 0 using profile MIG 2g.10gb (ID 14) Successfully created GPU instance ID 1 on GPU 0 using profile MIG 4g.20gb (ID 5)

$ sudo nvidia-smi mig -lgi

ID Start:Size |

|-----

0 MIG 1g.5gb 19 13 6:1

| 0 MIG 2g.10gb 14 5 4:2 |

0 MIG 4g.20gb 5 1 0:4

```

Example 2: Creation of a 3-2-1-1 geometry.

Due to a known issue with the APIs, the profile ID 9 or 3q.20qb must be specified first in order. Not doing so, will result in the following error.

```

$ sudo nvidia-smi mig -cgi 19,19,14,9

Successfully created GPU instance ID 13 on GPU 0 using profile MIG 1g.5gb (ID

19)

Successfully created GPU instance ID 11 on GPU 0 using profile MIG 1g.5gb (ID

19)

Successfully created GPU instance ID 3 on GPU 0 using profile MIG 2g.10gb

(ID 14)

Unable to create a GPU instance on GPU 0 using profile 9: Insufficient

Resources

Failed to create GPU instances: Insufficient Resources

```

Specify the correct order for the 3q.20qb profile. The remaining combinations of the profiles do not have this requirement.

```

$ sudo nvidia-smi mig -cgi 9,19,14,19

Successfully created GPU instance ID 2 on GPU 0 using profile MIG 3g.20gb (ID 9) Successfully created GPU instance ID 7 on GPU 0 using profile MIG 1g.5gb (ID 19) Successfully created GPU instance ID 4 on GPU 0 using profile MIG 2g.10gb (ID 14)

Successfully created GPU instance ID 8 on GPU 0 using profile MIG 1g.5gb (ID 19)

$ sudo nvidia-smi mig -lgi

| GPU instances:

Profile Instance Placement

| GPU Name

ID ID Start:Size

0 MIG 1q.5qb 19 7 0:1

| 0 MIG 1g.5gb 19 8

1:1

0 MIG 2g.10gb 14 4 2:2

0 MIG 3g.20gb 9 2 4:4

```

#### Example 3: Creation of a 2-1-1-1-1 geometry:

```

$ sudo nvidia-smi mig -cgi 14,19,19,19,19,19

Successfully created GPU instance ID 5 on GPU 0 using profile MIG 2g.10gb (ID 14)

Successfully created GPU instance ID 13 on GPU 0 using profile MIG 1g.5gb (ID 19) Successfully created GPU instance ID 7 on GPU 0 using profile MIG 1g.5gb (ID 19) Successfully created GPU instance ID 8 on GPU 0 using profile MIG 1g.5gb (ID 19) Successfully created GPU instance ID 9 on GPU 0 using profile MIG 1g.5gb (ID 19)

Successfully created GPU instance ID 10 on GPU 0 using profile MIG 1g.5gb (ID 19)

$ sudo nvidia-smi mig -lgi

| GPU instances:

GPU Name Profile Instance Placement

ID ID Start:Size

|------

0 MIG 1g.5gb 19 7 0:1

```

| 0 | MIG | 1g.5gb  | 19 | 8  | 1:1 |

|---|-----|---------|----|----|-----|

| 0 | MIG | 1g.5gb  | 19 | 9  | 2:1 |

| 0 | MIG | 1g.5gb  | 19 | 10 | 3:1 |

| 0 | MIG | 1g.5gb  | 19 | 13 | 6:1 |

| 0 | MIG | 2g.10gb | 14 | 5  | 4:2 |

| + |     |         |    |    |     |

### 9.5. Running CUDA Applications on Bare-Metal

## 9.5.1. GPU Instances

The following example shows how two CUDA applications can be run in parallel on two different GPU instances. In this example, the BlackScholes CUDA sample is run simultaneously on the two GIs created on the A100.

```

$ nvidia-smi -L

GPU 0: A100-SXM4-40GB (UUID: GPU-e86cb44c-6756-fd30-cd4a-1e6da3caf9b0)

MIG 3g.20gb Device 0: (UUID: MIG-c7384736-a75d-5afc-978f-d2f1294409fd)

MIG 3g.20gb Device 1: (UUID: MIG-a28ad590-3fda-56dd-84fc-0a0b96edc58d)

$ CUDA VISIBLE DEVICES=MIG-c7384736-a75d-5afc-978f-d2f1294409fd ./BlackScholes &

$ CUDA_VISIBLE_DEVICES=MIG-a28ad590-3fda-56dd-84fc-0a0b96edc58d ./BlackScholes &

```

Now verify the two CUDA applications are running on two separate GPU instances:

| nvidi       | .a-sm    | i          |            |                |                  |        |                      |                     |   |   |              |       |                      |

|-------------|----------|------------|------------|----------------|------------------|--------|----------------------|---------------------|---|---|--------------|-------|----------------------|

| MIG         | <br>devi | ces:       | <br>:      |                |                  |        |                      |                     |   |   |              |       | +                    |

| GPU         | GI<br>ID | CI<br>ID   | MIG<br>Dev | <br>           | <br>Memory-      | -Usage | +<br> <br>  SM<br>   | Vol <br>Unc <br>ECC |   |   | Share<br>DEC |       | JPG                  |

| 0           | 1        | 0          | 0          | 268Mi          | =====<br>B / 202 | 224MiB | +=====<br>  42       | 0                   | 3 | 0 | 2            | 0     | 0                    |

| 0           | 2        | 0          | 1          | 268Mi          | в / 200          | 96MiB  | +<br>  42            | 0                   | 3 | 0 | 2            | 0     | 0                    |

| Proc<br>GPU |          | I          | CI<br>ID   | PID            | <br>Type         | Proce  | ss name              |                     |   |   |              | U Mem | +<br> <br> ory  <br> |

| 0           |          | 1<br>2<br> | 0          | 58866<br>58856 |                  |        | ckSchole<br>ckSchole |                     |   |   |              |       | MiB  <br>MiB         |

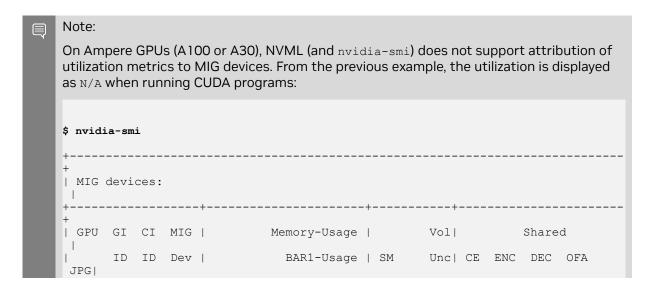

#### **GPU Utilization Metrics**

NVML (and nvidia-smi) does not support attribution of utilization metrics to MIG devices. From the previous example, the utilization is displayed as N/A when running CUDA programs:

| nvidia           | a-smi          | Ĺ                  |            |              |                   |                  |                     |             |    |     |     |                  |                |

|------------------|----------------|--------------------|------------|--------------|-------------------|------------------|---------------------|-------------|----|-----|-----|------------------|----------------|

| MIG d            | evi            | ces:               |            |              |                   |                  |                     |             |    |     |     |                  | +              |

|                  |                |                    | MIG<br>Dev |              | BAR1-             | -Usage<br>-Usage | SM                  | Unc <br>ECC | CE | ENC | DEC | OFA              |                |

| 0                | 1              | 0                  | 0          |              | B / 200<br>B / 32 | )96MiB           | +======<br>  42<br> | •           | 3  |     | 2   |                  | 0              |

| 0                | 2              | 0                  | 1          |              | B / 200<br>B / 32 | )96МіВ<br>767МіВ |                     | 0  <br>     |    | 0   | 2   | 0                | 0              |

| <br>Proce<br>GPU | <br>sse:<br>GI | Ι                  | CI<br>ID   | PID          | <br>Туре          | Proces           | ss name             |             |    |     |     | <br>U Mem<br>age | +<br> <br> ory |

| 0<br>0           | -              | ====<br>1<br>2<br> | 0<br>0<br> | 6217<br>6223 |                   | inu              |                     |             |    |     |     | 253<br>253<br>   |                |

For monitoring MIG devices on MIG capable GPUs such as the A100, including attribution of GPU metrics (including utilization and other profiling metrics), it is recommended to use NVIDIA DCGM v2.0.13 or later. See the Profiling Metrics section in the DCGM User Guide for more details on getting started.

## 9.5.2. Compute Instances

As explained earlier in this document, a further level of concurrency can be achieved by using Compute Instances (CIs). The following example shows how 3 CUDA processes (BlackScholes CUDA sample) can be run on the same GI.

First, list the available CI profiles available using our prior configuration of creating 2 GIs on the A100.

| sudo nvi | dia-smi miç                      | g -lcip -gi 1     |               |                         |                 |           |                       |     |

|----------|----------------------------------|-------------------|---------------|-------------------------|-----------------|-----------|-----------------------|-----|

| GPU      | instance<br>GPU<br>nstance<br>ID | profiles:<br>Name | Profile<br>ID | Instances<br>Free/Total | Exclusive<br>SM | DEC<br>CE | Shared<br>ENC<br>JPEG | OFA |

| 0        | 1                                | MIG 1c.3g.20gb    | 0             | 0/3                     | 14              | 2<br>3    | 0<br>0                | 0   |

| 0        | 1                                | MIG 2c.3g.20gb    | 1             | 0/1                     | 28              | 2<br>3    | 0<br>0                | 0   |

Create 3 Cls, each of type 1c compute capacity (profile ID 0) on the first Gl.

```

$ sudo nvidia-smi mig -cci 0,0,0 -gi 1

Successfully created compute instance on GPU 0 GPU instance ID 1 using profile MIG

1c.3g.20gb (ID 0)

Successfully created compute instance on GPU 0 GPU instance ID 1 using profile MIG

1c.3g.20gb (ID 0)

Successfully created compute instance on GPU 0 GPU instance ID 1 using profile MIG

1c.3g.20gb (ID 0)

```

Using nvidia-smi, the following CIs are now created on GI 1.

```

$ sudo nvidia-smi mig -lci -gi 1

| Compute instances:

| GPU GPU Name Profile Instance | ID TD

0 1 MIG 1c.3g.20gb 0 0

1

MIG 1c.3g.20gb

0 1

```

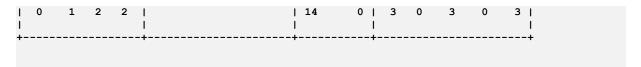

And the GIs and CIs created on the A100 are now enumerated by the driver:

```

$ nvidia-smi

| MIG devices:

| GPU GI CI MIG | Memory-Usage | Vol | Shared | ID ID Dev | SM Unc | CE ENC DEC OFA JPG | FCC | FA JPG | FCC | FCC

ECC |

0 | 3 0 2 0 0 |

| 0 1 1 1 |

0 1 2 2 |

| Processes:

CI

PID Type Process name

GPU Memory |

GPU GI

ID ID

Usage

| No running processes found

```

Now, three BlackScholes applications can be created and run in parallel:

```

$ CUDA VISIBLE DEVICES=MIG-c7384736-a75d-5afc-978f-d2f1294409fd ./BlackScholes &

$ CUDA VISIBLE DEVICES=MIG-c376546e-7559-5610-9721-124e8dbb1bc8 ./BlackScholes &

$ CUDA VISIBLE DEVICES=MIG-928edfb0-898f-53bd-bf24-c7e5d08a6852 ./BlackScholes &

```

And seen using nvidia-smi as running processes on the three CIs:

| MIG d        | evice             | es:      |             |                         |         |                  |                                  |                     |   |   |              |                |                   |

|--------------|-------------------|----------|-------------|-------------------------|---------|------------------|----------------------------------|---------------------|---|---|--------------|----------------|-------------------|

|              |                   | CI<br>ID | MIG<br>Dev  | <br> <br> <br>          | Memory  | -Usage           | SM                               | Vol <br>Unc <br>ECC |   |   | Share<br>DEC |                | JPG               |

| 0            | 1                 | 0        | 0           | +=======<br>  476Mi     | B / 202 | ======<br>224MiB | +=====<br>  14                   | 0                   | 3 | 0 | 2            | 0              | 0                 |

| 0            | 1                 | 1        | 1           | <del>-</del><br>        |         | -                | 14                               | 0                   | 3 | 0 | 2            | 0              | 0                 |

| 0            | 1                 | 2        | 2           | <del>-</del><br>        |         | -                | 14                               | 0                   | 3 | 0 | 2            | 0              | 0                 |

| Proce<br>GPU | sses:<br>GI<br>ID |          | CI<br>ID    | PID                     | Туре    | Proces           | ss name                          |                     |   |   |              | PU Mem<br>sage | ory               |

| 0 0          | 1<br>1<br>1       |          | 0<br>1<br>2 | 59785<br>59796<br>59885 | С       | ./Blad           | ckSchole<br>ckSchole<br>ckSchole | s                   |   |   |              | 153            | MiB<br>MiB<br>MiB |

### 9.6. **Destroying GPU Instances**

Once the GPU is in MIG mode, GIs and CIs can be configured dynamically. The following example shows how the CIs and GIs created in the previous examples can be destroyed.

```

Note:

If the intention is to destroy all the CIs and GIs, then this can be accomplished with the

following commands:

$ sudo nvidia-smi mig -dci && sudo nvidia-smi mig -dgi

Successfully destroyed compute instance ID 0 from GPU 0 GPU instance ID 1

Successfully destroyed compute instance ID 1 from GPU 0 GPU instance ID 1

Successfully destroyed compute instance ID \, 2 from GPU \, 0 GPU instance ID \, 1

Successfully destroyed GPU instance ID 1 from GPU 0 Successfully destroyed GPU instance ID 2 from GPU 0

```

In this example, we delete the specific CIs created under GI 1.

```

$ sudo nvidia-smi mig -dci -ci 0,1,2 -gi 1

Successfully destroyed compute instance ID 0 from GPU 0 GPU instance ID 1

Successfully destroyed compute instance ID 1 from GPU 0 GPU instance ID 1

Successfully destroyed compute instance ID 2 from GPU 0 GPU instance ID 1

```

It can be verified that the CI devices have now been torn down on the GPU:

```

$ nvidia-smi

| MIG devices:

| GPU GI CI MIG | Memory-Usage | Vol | Shared | ID ID Dev | | SM Unc | CE ENC DEC OFA JPG | ECC | |

| No MIG devices found

| Processes:

PID Type Process name

GPU Memory |

Usage |

| GPU GI CI

ID

|------

| No running processes found

```

Now the GIs have to be deleted:

```

$ sudo nvidia-smi mig -dgi

Successfully destroyed GPU instance ID 1 from GPU 0 Successfully destroyed GPU instance ID 2 from GPU 0

```

# Monitoring MIG Devices

For monitoring MIG devices on including attribution of GPU metrics (including utilization and other profiling metrics), it is recommended to use NVIDIA DCGM v3 or later. See the <u>Profiling Metrics</u> section in the DCGM User Guide for more details on getting started.

| <br>   <br>    = |       |       |     | <br>==+==: |              |          | -===+====   | ECC      |      |       |    |       |    |

|------------------|-------|-------|-----|------------|--------------|----------|-------------|----------|------|-------|----|-------|----|

| +=               | 0     | 1     | 0 0 |            | == <br>268M: | iB / 200 | )96MiB   42 | 0        | 3    | 0     | 2  | 0     |    |

|                  |       |       |     | 1          | 4M           | , -      | 767MiB      |          |      |       |    |       |    |

| +                | 0     | 2     | 0 1 |            | 268M:        |          | )96MiB   42 | ·        |      |       | 2  | 0     |    |

|                  | ı     |       |     | 1          |              | , -      | 767MiB      | I        |      |       |    |       |    |

| +-               |       |       |     | +          |              |          |             | +        |      |       |    |       |    |

| +-               | Proce | sses: |     |            |              |          |             |          |      |       |    |       |    |

| H',              | GPU   | GI    | CI  |            | PID          | Type     | Process nam | ne       |      |       | GP | U Mem | or |

|                  |       | ID    | ID  |            |              |          |             |          |      |       | Us | age   |    |

| ==               | 0     | 1     | 0   | =====      | 6217         |          | inux/rel    |          |      |       |    | 253   |    |

| l . '            | 0     | 2     | 0   |            | 6223         | С        | inux/rel    | Lease/Bl | ackS | chole | s  | 253   | Μi |

| l ' ,            |       |       |     |            |              |          |             |          |      |       |    |       |    |

# 9.8. MIG with CUDA MPS