# **NVIDIA DOCA PCC Application Guide**

## Table of contents

| Introduction                                  |

|-----------------------------------------------|

| System Design                                 |

| Application Architecture                      |

| DOCA Libraries                                |

| Dependencies                                  |

| Running the Application                       |

| Installation                                  |

| Prerequisites                                 |

| Application Execution                         |

| Command Line Flags                            |

| Troubleshooting                               |

| Recompiling the Application                   |

| Recompiling All Applications                  |

| Recompiling PCC Application Only              |

| Troubleshooting                               |

| Application Code Flow                         |

| Port Programmable Congestion Control Register |

| Usage                                         |

| Internal Default Algorithm                    |

| Counters                                      |

| References                                    |

This document provides a DOCA PCC implementation on top of NVIDIA® BlueField® DPU.

### Introduction

Programmable Congestion Control (PCC) allows users to design and implement their own congestion control (CC) algorithm, giving them the flexibility to work out an optimal solution to handle congestion in their clusters. On BlueField-3, PCC is provided as a component of DOCA.

The application leverages the <u>DOCA PCC</u> API to provide users the flexibility to manage allocation of DPA resources according to their requirements.

Typical DOCA application includes App running on host/Arm and App running on DPA. Developers are advised to use the host/Arm application with minimal changes and focus on developing their algorithm and integrating it into the DPA application.

### **System Design**

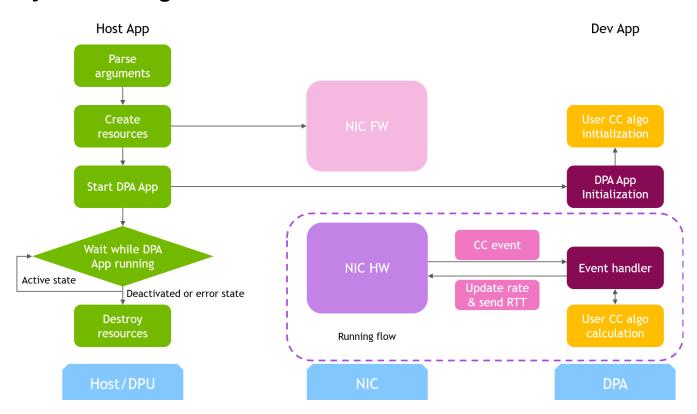

DOCA PCC application consists of two parts:

• Host/Arm app is the control plane. It is responsible for allocating all resources and handover to the DPA app initially, then destroying everything when the DPA app

finishes its operation. The host app must always be alive to stay in control while the device app is working.

Device/DPA app is the data plane. It is mainly for CC event handler. When the first

thread is activated, DPA App initialization is done in the DOCA PCC library by calling

the algorithm initialization function implemented by the user in the app. Moreover,

the user algorithm execution function is called when a CC event arrives. The user

algorithm takes event data as input and performs a calculation using per-flow

context and replies with updated rate value and a flag to sent RTT request.

The host/Arm application sends command to NIC firmware when allocating or destroying resources. CC events are generated by NIC hardware automatically when sending data or receiving ACK/NACK/CNP/RTT packets, then the device application handles these events by calling the user algorithm. After the DPA application replies to hardware, handling of current event is done and the next event can arrive.

### **Application Architecture**

```

/opt/mellanox/doca/applications/pcc/src

host

pcc.c

pcc_core.c

pcc_core.h

device

algo

rtt_template.h

rtt_template_algo_params.h

rtt_template_ctxt.h

rtt_template.c

pcc_dev_main.c

```

The main content of the reference DOCA PCC application files are the following:

- host/pcc.c entry point to entire application

- host/pcc\_core.c host functions to initialize and destroy the PCC application resources, parsers for PCC command line parameters

- device/pcc\_dev\_main.c callbacks for user CC algorithm initialization, user CC algorithm calculation, algorithm parameter change notification

- device/algo/\* user CC algorithm reference template. Put user algorithm code here.

### **DOCA Libraries**

This application leverages the following DOCA library:

DOCA PCC

Refer to its respective programming guide for more information.

### **Dependencies**

- NVIDIA BlueField-3 DPU is required

- Firmware 32.38.1000 and higher

- MFT 4.25 and higher

### **Running the Application**

### Installation

Refer to the <u>NVIDIA DOCA Installation Guide for Linux</u> for details on how to install BlueField-related software.

### **Prerequisites**

Enable USER\_PROGRAMMABLE\_CC in mlxconfig:

mlxconfig -y -d /dev/mst/mt41692\_pciconf0 set USER\_PROGRAMMABLE\_CC=1 R eset firmware or power cycle the host to apply the configuration change.

### Note

Make sure to perform graceful shutdown before power cycling the host.

### **Application Execution**

The PCC application is provided in both source and binary forms. The binary is located under /opt/mellanox/doca/applications/pcc/bin/doca\_pcc.

1. Application usage instructions:

```

Usage: doca_pcc [DOCA Flags] [Program Flags]

DOCA Flags:

-h, --help

Print a help synopsis

-v, --version

Print program version

information

-1, --log-level

Set the (numeric) log level for

the program <10=DISABLE, 20=CRITICAL, 30=ERROR, 40=WARNING,

50=INFO, 60=DEBUG, 70=TRACE>

--sdk-log-level

Set the SDK (numeric) log level

for the program <10=DISABLE, 20=CRITICAL, 30=ERROR, 40=WARNING,

50=INFO, 60=DEBUG, 70=TRACE>

Parse all command flags from an

-j, --json <path>

input json file

Program Flags:

-d, --device <IB device names> IB device name that

supports PCC (mandatory).

```

-w, --wait-time <PCC wait time> The duration of the DOCA PCC wait (optional), can provide negative values which means infinity. If not provided then -1 will be chosen.

-p, --pcc-threads <pcc-threads-list> A list of the PCC threads numbers to be chosen for the DOCA PCC context to run on (optional). Must be provided as a string, such that the number are separated by a space.

### (i) Info

This usage printout can be printed to the command line using the -h (or --help) options:

/opt/mellanox/doca/applications/pcc/bin/doca\_pcc

-h

### (i) Info

For additional information, refer to section "Command Line Flags".

2. CLI example for running the application on the BlueField or the host:

/opt/mellanox/doca/applications/pcc/bin/doca\_pcc -d mlx5 $\_$ 0

### (i) Note

The IB device identifier ( $m1 \times 5_0$ ) should match the identifier of the desired IB device.

3. The application also supports a JSON-based deployment mode, in which all command-line arguments are provided through a JSON file:

```

doca_pcc --json [json_file]

```

For example:

```

cd /opt/mellanox/doca/applications/pcc/bin

./doca_pcc --json ./pcc_params.json

```

### (i) Note

Before execution, ensure that the used JSON file contains the correct configuration parameters, and especially the PCIe addresses necessary for the deployment.

## **Command Line Flags**

| Flag<br>Typ<br>e    | Sh<br>ort<br>Fla<br>g | Long<br>Flag/J<br>SON<br>Key | Description            | JSON Content |

|---------------------|-----------------------|------------------------------|------------------------|--------------|

| Gen<br>eral<br>flag | h                     | hel                          | Prints a help synopsis | N/A          |

NVIDIA DOCA PCC Application Guide

S

| Flag<br>Typ<br>e | Sh<br>ort<br>Fla<br>g                                                                                   | Long<br>Flag/J<br>SON<br>Key      | Description                                                                                       | JSON Content |

|------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------|--------------|

|                  | V                                                                                                       | ver<br>sio<br>n                   | Prints program version information                                                                | N/A          |

|                  | Sets the log level for the progra  DISABLE=10 CRITICAL=20 ERROR=30 WARNING=40 INFO=50 DEBUG=60 TRACE=70 |                                   |                                                                                                   |              |

|                  |                                                                                                         | log - lev el                      | The applicati on uses a unique logging impleme ntation that makes use of DOCA's logging levels.   | N/A          |

|                  | N/<br>A                                                                                                 | sdk<br>-<br>log<br>-<br>lev<br>el | Sets the log level for the program:  • DISABLE=10 • CRITICAL=20 • ERROR=30 • WARNING=40 • INFO=50 | N/A          |

| Flag<br>Typ<br>e             | Sh<br>ort<br>Fla<br>g | Long<br>Flag/J<br>SON<br>Key | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | JSON Content                                                                                                                                                                                                               |

|------------------------------|-----------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              |                       |                              | <ul><li>DEBUG=60</li><li>TRACE=70</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                            |

|                              | j                     | jso<br>n                     | Parse all command flags from an input JSON file                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | N/A                                                                                                                                                                                                                        |

|                              | d                     |                              | IB device name that supports PCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | "device": ""                                                                                                                                                                                                               |

|                              | W                     | wai<br>t-<br>tim<br>e        | (Optional) In seconds, the duration of the DOCA PCC wait. Negative values mean infinity.                                                                                                                                                                                                                                                                                                                                                                                                                                       | "wait-time": -1                                                                                                                                                                                                            |

| Pro<br>gra<br>m<br>flag<br>s | р                     | pcc<br>-<br>thr<br>ead<br>s  | (Optional) A list of the PCC EU indexes to be chosen for the DOCA PCC event handler threads to run on. Must be provided as a string, such that the numbers are separated by a space.  The placement of the PCC threads per core can be controlled using the EU indexes. Utilizing a large number of EUs, while limiting the number of threads per core, gives the best event handling rate and lowest event latency.  The last EU is used for communication with the NIC while all others are for data path CC event handling. | "pcc-threads":  "176 177 178 179 180 181 1 82 183  184 185 186 187 192 193 19 4 195 196 197 198 199 200 201 202 203 208 209 21 0 211 212 213 214 215 216 217 218 219 224 225 22 6 227 228 229 230 231 232 233 234 235 240" |

Refer to <u>DOCA Arg Parser</u> for more information regarding the supported flags and execution modes.

### **Troubleshooting**

Refer to the <u>NVIDIA DOCA Troubleshooting Guide</u> for any issue encountered with the installation or execution of the DOCA applications.

## **Recompiling the Application**

In addition to providing the application in binary form, the installation also includes all of the application sources and compilation instructions so as to allow modifying the sources and recompiling the application. For more information about the applications, as well as development and compilation tips, refer to the <u>DOCA Applications</u> page.

The sources of the application can be found under the //opt/mellanox/doca/applications/pcc/src directory.

## **Recompiling All Applications**

The applications are all defined under a single meson project, so the default compilation recompiles all the DOCA applications.

To build all the applications together, run:

cd /opt/mellanox/doca/applications/

meson /tmp/build

ninja -C /tmp/build

Info

```

doca_pcc is created under /tmp/build/pcc/src/.

```

### **Recompiling PCC Application Only**

To directly build only the PCC application:

```

cd /opt/mellanox/doca/applications/

meson /tmp/build -Denable_all_applications=false -Denable_pcc=true

ninja -C /tmp/build

```

## (i) Info

doca\_pcc is created under /tmp/build/pcc/src/.

Alternatively, one can set the desired flags in the meson\_options.txt file instead of providing them in the compilation command line:

1. Edit the following flags in

/opt/mellanox/doca/applications/meson\_options.txt:

- Set enable\_all\_applications to false

- Set enable\_pcc to true

- 2. Run the following compilation commands:

cd /opt/mellanox/doca/applications/

meson /tmp/build

ninja -C /tmp/build

### (i) Info

doca\_pcc is created under /tmp/build/pcc/src/.

## **Troubleshooting**

Refer to the NVIDIA DOCA Troubleshooting Guide for any issue encountered with the compilation of the application.

### **Application Code Flow**

This section lists the application's configuration flow, explaining the different DOCA function calls and wrappers.

- 1. Parse application argument.

- 1. Initialize arg parser resources and register DOCA general parameters.

```

doca_argp_init();

```

2. Register PCC application parameters.

```

register_pcc_params();

```

3. Parse the arguments.

```

doca_argp_start();

```

- 1. Parse DOCA flags.

- 2. Parse DOCA PCC parameters.

- 2. PCC initialization.

```

pcc_init();

```

- 1. Open DOCA device that supports PCC.

- 2. Create DOCA PCC context.

- 3. Configure affinity of threads handling CC events.

- 3. Start DOCA PCC.

```

doca_pcc_start();

```

- 1. Create PCC process and other resources.

- 2. Trigger initialization of PCC on device.

- 3. Register the PCC in the NIC hardware so CC events can be generated and an event handler can be triggered.

- 4. Process state monitor loop.

```

doca_pcc_get_process_state();

doca_pcc_wait();

```

1. Get the state of the process:

| State                           | Description                                                                |

|---------------------------------|----------------------------------------------------------------------------|

| DOCA_PCC_PS_ACTIVE = 0          | The process handles CC events (only one process is active at a given time) |

| DOCA_PCC_PS_STANDB<br>Y = 1     | The process is in standby mode (another process is already ACTIVE)         |

| DOCA_PCC_PS_DEACTI<br>VATED = 2 | The process has been deactivated by NIC firmware and should be destroyed   |

| DOCA_PCC_PS_ERROR<br>= 3        | The process is in error state and should be destroyed                      |

- 2. Wait on process events from the device.

- 5. PCC destroy.

```

doca_pcc_destroy();

```

- 1. Destroy PCC resources. The process stops handling PCC events.

- 2. Close DOCA device.

- 6. Arg parser destroy.

```

doca_argp_destroy()

```

## Port Programmable Congestion Control Register

The Port Programmable Congestion Control (PPCC) register allows the user to configure and read PCC algorithms and their parameters/counters.

It supports the following functionalities:

- Enabling different algorithms on different ports

- Querying information of both algorithms and tunable parameters/counters

- Changing algorithm parameters without compiling and reburning user image

- Querying or clearing programmable counters

### **Usage**

The PPCC register can be accessed using a string similar to the following:

```

sudo mlxreg -d /dev/mst/mt41692_pciconf0 -y --get --op

"cmd_type=0" --reg_name PPCC --indexes

"local_port=1,pnat=0,lp_msb=0,algo_slot=0,algo_param_index=0"

sudo mlxreg -d /dev/mst/mt41692_pciconf0 -y --set "cmd_type=1" --

reg_name PPCC --indexes

"local_port=1,pnat=0,lp_msb=0,algo_slot=0,algo_param_index=0"

```

### Where you must:

- Set the cmd\_type and the indexes

- Give values for algo\_slot, algo\_param\_index

- Keep [local\_port=1], [pnat=0], [lp\_msb=0]

- Keep doca\_pcc application running

| cmd<br>_typ<br>e | Descriptio<br>n          | Me<br>tho<br>d | Index         | Input (in<br>set) | Output                                                                                                                                                                                                            |

|------------------|--------------------------|----------------|---------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x<br>0          | Get<br>algorithm<br>info | Get            | algo_<br>slot | N/A               | <ul> <li>Value – 32-bit algo_num or 0 if no algo is available at this index</li> <li>Text – algorithm description</li> <li>sl_bitmask_support – indicates whether the device supports sl_bitmask logic</li> </ul> |

| 0x<br>1          | Enable<br>algorithm      | Set            |               | sl_bitmas<br>k    | N/A                                                                                                                                                                                                               |

| cmd<br>_typ<br>e | Descriptio<br>n                        | Me<br>tho<br>d | Index                                         | Input (in<br>set)  | Output                                                                                                                                                                                                                                                                                                     |

|------------------|----------------------------------------|----------------|-----------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                                        |                |                                               | trace_en counter_e |                                                                                                                                                                                                                                                                                                            |

| 0x<br>2          | Disable<br>algorithm                   | Set            |                                               | N/A                | N/A                                                                                                                                                                                                                                                                                                        |

| 0x<br>3          | Get<br>algorithm<br>enabling<br>status | Get            |                                               | N/A                | <ul> <li>Value:         <ul> <li>0 - disabled</li> <li>1 - enabled</li> </ul> </li> <li>sl_bitmask - this field allows to apply to specific SLs based on the bitmask</li> <li>sl_bitmask_support - indicates whether the device supports sl_bitmask logic</li> </ul>                                       |

| 0x<br>4          | Get<br>number of<br>parameter<br>s     | Get            |                                               | N/A                | Value – num of params of algo                                                                                                                                                                                                                                                                              |

| 0x<br>5          | Get<br>parameter<br>informatio<br>n    | Get            | algo_<br>slot<br>algo_<br>param<br>_inde<br>x | N/A                | <ul> <li>param_value1 - default value of param</li> <li>param_value2 - min value of param</li> <li>param_value3 - max value of param</li> <li>prm -         <ul> <li>0: read-only</li> <li>1: read-write</li> <li>2: read-only but may be cleared using the "get and clear" command</li> </ul> </li> </ul> |

| 0x<br>6          | Get<br>parameter<br>value              | Get            |                                               | N/A                | Value – param value                                                                                                                                                                                                                                                                                        |

| cmd<br>_typ<br>e | Descriptio<br>n                   | Me<br>tho<br>d | Index | Input (in<br>set)                                            | Output                                                                                                             |

|------------------|-----------------------------------|----------------|-------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| 0x 7             | Get and clear parameter           | Get            |       | N/A                                                          | Value – param value                                                                                                |

| 0x<br>8          | Set<br>parameter<br>value         | Set            |       | Parameter value                                              | N/A                                                                                                                |

| 0x<br>A          | Bulk get<br>parameter<br>s        | Get            |       | N/A                                                          | <ul><li>text_length - param num x 4 bytes</li><li>text[0]text[n] - param values</li></ul>                          |

| 0x<br>B          | Bulk set<br>parameter<br>s        | Set            | algo_ | text_leng th - param num x 4  text[0] text[n] - param values | N/A                                                                                                                |

| 0x<br>C          | Bulk get<br>counters              | Get            | slot  | N/A                                                          | <ul> <li>text_length - counter num x 4 bytes</li> <li>text[0]text[n] - counter values</li> </ul>                   |

| 0x<br>D          | Bulk get<br>and clear<br>counters | Get            |       | N/A                                                          | <ul> <li>text_length - counter num x</li> <li>4 bytes</li> <li>text[0]text[n] - counter</li> <li>values</li> </ul> |

| 0x<br>E          | Get<br>number of<br>counters      | Get            |       | N/A                                                          | Value – num of counters of algo                                                                                    |

| cmd<br>_typ<br>e | Descriptio<br>n                   | Me<br>tho<br>d | Index                                         | Input (in<br>set) | Output                                                                                                                                                                                                   |

|------------------|-----------------------------------|----------------|-----------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x<br>F          | Get<br>counter<br>informatio<br>n | Get            | algo_<br>slot<br>algo_<br>param<br>_inde<br>x | N/A               | <ul> <li>param_value3 - max value of parameter</li> <li>prm - <ul> <li>0: read-only</li> <li>1: read-write</li> <li>2: read-only but may be cleared via "get &amp; clear" command</li> </ul> </li> </ul> |

| 0x<br>10         | Get<br>algorithm<br>info array    | Get            | N/A                                           | N/A               | <ul> <li>text_length - algo slot initialized x 4 bytes</li> <li>text[0]text[n] - 32-bit algo_num or 0 if no algorithm is available at this slot index</li> </ul>                                         |

### **Internal Default Algorithm**

The internal default algorithm is used when enhanced connection establishment (ECE) negotiation fails. It is mainly used for backward compatibility and can be disabled using "force mode". Otherwise, users may change doca\_pcc\_dev\_user\_algo() in the device app to run a specific algorithm without considering the algorithm negotiation.

The force mode command is per port:

```

sudo mlxreg -d /dev/mst/mt41692_pciconf0 -y --get --op "cmd_type=2"

--reg_name PPCC --indexes

"local_port=1,pnat=0,lp_msb=0,algo_slot=15,algo_param_index=0"

sudo mlxreg -d /dev/mst/mt41692_pciconf0.1 -y --get --op "cmd_type=2"

--reg_name PPCC --indexes

"local_port=1,pnat=0,lp_msb=0,algo_slot=15,algo_param_index=0"

```

### **Counters**

Counters are shared on the port and are only enabled on one algo\_slot per port. The following command enables the counters while enabling the algorithm according to the algo\_slot:

```

sudo mlxreg -d /dev/mst/mt41692_pciconf0 -y --set

"cmd_type=1,counter_en=1" --reg_name PPCC --indexes

"local_port=1,pnat=0,lp_msb=0,algo_slot=0,algo_param_index=0"

```

After counters are enabled on the algo\_slot, they can be queried using cmd\_type 0xC or 0xD.

```

sudo mlxreg -d /dev/mst/mt41692_pciconf0 -y --get --op "cmd_type=12" --reg_name PPCC --indexes "local_port=1,pnat=0,lp_msb=0,algo_slot=0,algo_param_index=0" sudo mlxreg -d /dev/mst/mt41692_pciconf0 -y --get --op "cmd_type=13" --reg_name PPCC --indexes "local_port=1,pnat=0,lp_msb=0,algo_slot=0,algo_param_index=0"

```

### References

- /opt/mellanox/doca/applications/pcc/src

- /opt/mellanox/doca/applications/pcc/bin/pcc\_params.json

<b>Notice</b><br/>This document is provided for information purposes only and shall not be regarded as a warranty of a certain functionality, condition, or quality of a product. NVIDIA Corporation ("NVIDIA") makes no representations or warranties, expressed or implied, as to the accuracy or completeness of the information contained in this document and assumes no responsibility for any errors contained herein. NVIDIA shall have no liability for the consequences or use of such information or for any infringement of patents or other rights of third parties that may result from its use. This document is not a commitment to develop, release, or deliver any Material (defined below), code, or functionality.<br/>br/>kpr/>kpr/>NVIDIA reserves the right to make corrections, modifications, enhancements, improvements, and any other changes to this document, at any time without notice.<br/>br/>kpr/>Customer should obtain the latest relevant information before placing orders and should verify that such information is current and complete.<br/>kpr/>kpr/>NVIDIA products are sold subject to the NVIDIA standard terms and conditions of sale supplied at the time of order acknowledgement, unless otherwise agreed in an individual sales agreement signed by authorized representatives of NVIDIA and customer ("Terms of Sale"). NVIDIA hereby expressly objects to applying any customer general terms and conditions with regards to the purchase of the NVIDIA product referenced in this document. No contractual obligations are formed either directly or indirectly by this document.

warranted to be suitable for use in medical, military, aircraft, space, or life support equipment, nor in applications where failure or malfunction of the NVIDIA product can reasonably be expected to result in personal injury, death, or property or environmental damage. NVIDIA accepts no liability for inclusion and/or use of NVIDIA products in such equipment or applications and therefore such inclusion and/or use is at customer's own risk.<br/>br/><br/>NVIDIA makes no representation or warranty that products based on this document will be suitable for any specified use. Testing of all parameters of each product is not necessarily performed by NVIDIA. It is customer's sole responsibility to evaluate and determine the applicability of any information contained in this document, ensure the product is suitable and fit for the application planned by customer, and perform the necessary testing for the application in order to avoid a default of the application or the product. Weaknesses in customer's product designs may affect the quality and reliability of the NVIDIA product and may result in additional or different conditions and/or requirements beyond those contained in this document. NVIDIA accepts no liability related to any default, damage, costs, or problem which may be based on or attributable to: (i) the use of the NVIDIA product in any manner that is contrary to this document or (ii) customer product designs.<br/>

No license, either expressed or implied, is granted under any NVIDIA patent right, copyright, or other NVIDIA intellectual property right under this document. Information published by NVIDIA regarding third-party products or services does not constitute a license from NVIDIA to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property rights of the third party, or a license from NVIDIA under the patents or other intellectual property rights of NVIDIA.<br/><br/><br/><br/><br/>>cbr/><br/>>rights of NVIDIA.<br/><br/>in this document is permissible only if approved in advance by NVIDIA in writing, reproduced without alteration and in full compliance with all applicable export laws and regulations, and accompanied by all associated conditions, limitations, and notices.<br/><br/><br/><br/><br/><br/><br/> DOCUMENT AND ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS, AND OTHER DOCUMENTS (TOGETHER AND SEPARATELY, "MATERIALS") ARE BEING PROVIDED "AS IS." NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY, OR OTHERWISE WITH RESPECT TO THE MATERIALS, AND EXPRESSLY DISCLAIMS ALL IMPLIED WARRANTIES OF NONINFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE. TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL NVIDIA BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF NVIDIA HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Notwithstanding any damages that customer might incur for any reason whatsoever, NVIDIA's aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms of trademarks and/or registered trademarks of NVIDIA Corporation in the U.S. and other countries. Other company and product names may be trademarks of the respective companies with which they are associated.<br/>

product names may be trademarks of the respective companies

© Copyright 2024, NVIDIA. PDF Generated on 01/15/2025