# **NVIDIA Grace Performance Tuning Guide**

# **Document History**

#### DA-11438-001\_04

| Version | Date             | Description of Change                                                                                                                                                                 |

|---------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01      | April 18. 2023   | Initial Release                                                                                                                                                                       |

| 02      | November 9, 2023 | Version 1.0 Release                                                                                                                                                                   |

| 03      | February 6, 2024 | Added information about the CPU code locality tool (refer to <u>Using Code Locality to Improve Performance</u> for more information).                                                 |

| 04      | March 8, 2024    | Updated the following sections:  • CPU Performance and Frequency Management  • Power and Thermal Management  • Performance Governor  • Init on Alloc  • Grace CPU Performance Metrics |

## **Table of Contents**

| 1. Introduction                                                         | 6  |

|-------------------------------------------------------------------------|----|

| 1.1. NVIDIA Grace CPU Superchip and NVIDIA GH200 Grace Hopper Superchip |    |

| Overview                                                                | 6  |

| 1.1.1. High Performance Architecture                                    | 9  |

| 1.1.2. Alleviate Bottlenecks with NVLink-C2C Interconnect               | 9  |

| 1.1.3. Scale Cores and Bandwidth with NVIDIA Scalable Coherency Fabric  | 10 |

| 1.1.4. LPDDR5X Memory Subsystem                                         | 11 |

| 1.1.5. CPU I/O                                                          | 12 |

| 1.1.6. Grace CPU Core Architecture                                      | 12 |

| 1.1.7. SIMD Vectorization                                               | 13 |

| 1.1.8. Atomic Operations                                                | 13 |

| 1.1.9. Additional Armv9 Features                                        | 14 |

| 2. Understanding Your Grace Machine                                     | 15 |

| 2.1. Checking the CPUs                                                  | 16 |

| 2.2. Checking the Non-Uniform Memory Access Settings                    | 18 |

| 2.3. Checking the GPU                                                   | 20 |

| 2.4. Checking the Memory                                                | 21 |

| 3. Basic System Health Checks                                           | 23 |

| 3.1. STREAM                                                             | 23 |

| 3.2. Fused Multiply Add                                                 | 25 |

| 3.3. C2C CPU-GPU Bandwidth                                              | 26 |

| 4. Power and Thermals                                                   | 29 |

| 4.1. C-States                                                           | 29 |

| 4.2. P-States                                                           | 29 |

| 4.3. CPU Performance and Frequency Management                           | 30 |

| 4.3.1. Setting a Fixed Frequency                                        | 31 |

| 4.3.2. Setting a Scaling Max Frequency                                  | 31 |

| 4.4. GPU and Module Power Management                                    | 32 |

| 4.5. Power and Thermal Management                                       | 34 |

| 4.6. Power Telemetry                                                    | 34 |

| 4.6.1. Grace Power Telemetry                                            | 34 |

| 4.6.2. Comparing Grace and Intel® Power Telemetry                       | 38 |

| 4.6.3. Comparing Grace and AMD Power Telemetry                          | 40 |

| 4.7. Power Capping                                                      | 42 |

| 4.8. CPU Temperature Management                                         | 42 |

| 4.9. GPU Temperatures                                                | 43 |

|----------------------------------------------------------------------|----|

| 5. Operating System Settings                                         | 44 |

| 5.1. Page Size                                                       | 44 |

| 5.2. Huge Pages                                                      | 44 |

| 5.2.1. Transparent Huge Pages                                        | 45 |

| 5.2.2. Proactive Compaction                                          | 45 |

| 5.2.3. Hugetlbfs                                                     | 46 |

| 5.3. Configuring Linux Perf                                          | 46 |

| 5.4. Performance Governor                                            | 46 |

| 5.5. Init on Alloc                                                   | 46 |

| 5.6. Input-Output Memory Management Unit Passthrough                 | 47 |

| 5.7. Automatic NUMA Scheduling and Balancing                         | 48 |

| 5.8. Swap File Size                                                  | 49 |

| 6. Optimizing IO Performance                                         | 50 |

| 6.1. Networking                                                      | 50 |

| 6.1.1. NUMA Node                                                     | 50 |

| 6.1.2. IRQ Balance                                                   | 50 |

| 6.1.3. Configuring Interrupt Handling                                | 50 |

| 6.1.4. TX/RX Queue Size                                              | 51 |

| 6.1.5. Large Receive Offload                                         | 51 |

| 6.1.6. MTU                                                           | 52 |

| 6.1.7. MAX_ACC_OUT_READ                                              | 52 |

| 6.1.8. PCIe Max Read Request                                         | 52 |

| 6.1.9. Relaxed Ordering                                              | 53 |

| 6.1.10. 10b PCle tags                                                | 53 |

| 6.2. Storage/Filesystem                                              | 53 |

| 6.2.1. Drop Page Cache                                               | 53 |

| 7. Measuring Workload Performance with Hardware Performance Counters | 55 |

| 7.1. Introduction to Linux perf                                      | 55 |

| 7.2. Configuring Perf                                                | 56 |

| 7.3. Gathering Hardware Performance Data with Perf                   | 57 |

| 7.4. Grace CPU Performance Metrics                                   | 57 |

| 7.4.1. Cycle and Instruction Accounting                              | 58 |

| 7.4.2. Computational Intensity                                       | 58 |

| 7.4.3. Operation Mix                                                 | 59 |

| 7.4.4. SVE Predication                                               | 60 |

| 7.4.5. Cache Effectiveness                                           | 60 |

| 7.4.6. TLB Effectiveness                                             | 61 |

| 7.4.7. Branching                                           | 62 |  |

|------------------------------------------------------------|----|--|

| 7.4.8. Grace Uncore PMU Units                              | 62 |  |

| 7.4.9. Scalable Coherency Fabric PMU Accounting            | 64 |  |

| 7.4.10. PCle PMU Accounting                                | 67 |  |

| 7.4.11. NVLink C2C Accounting                              | 68 |  |

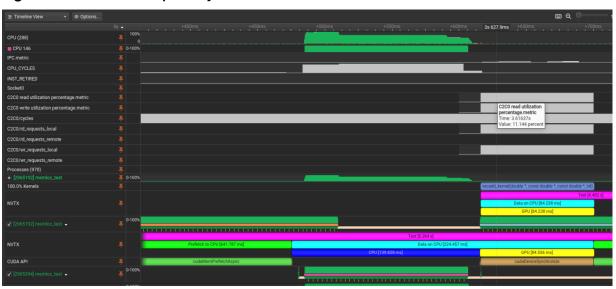

| 7.4.12. Profiling CPU Behavior with Nsight Systems         | 69 |  |

| 8. Compilers                                               | 71 |  |

| 8.1. NVIDIA HPC Compilers                                  | 71 |  |

| 8.2. GNU Toolchain                                         | 72 |  |

| 8.3. LLVM Clang and Flang Compilers                        | 73 |  |

| 8.4. Arm Compiler for Linux and Other Commercial Compilers | 73 |  |

| 8.5. Arm Architecture Feature Support                      | 74 |  |

| 8.6. Using Code Locality to Improve Performance            | 76 |  |

| 9. Performance Tuning for Grace Hopper-Based Applications  |    |  |

| Appendix A: References                                     | 79 |  |

|                                                            |    |  |

### 1. Introduction

# NVIDIA Grace CPU Superchip and NVIDIA GH200 Grace Hopper Superchip Overview

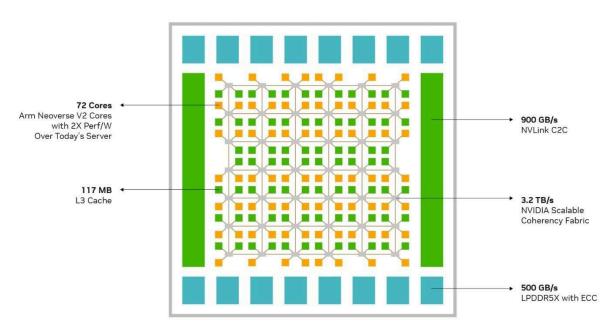

The Grace CPU is the first data center CPU designed by NVIDIA. The Grace CPU has 72 high-performance and power efficient Arm Neoverse V2 Cores, connected by a high-performance NVIDIA Scalable Coherency Fabric and server-class LPDDR5X memory.

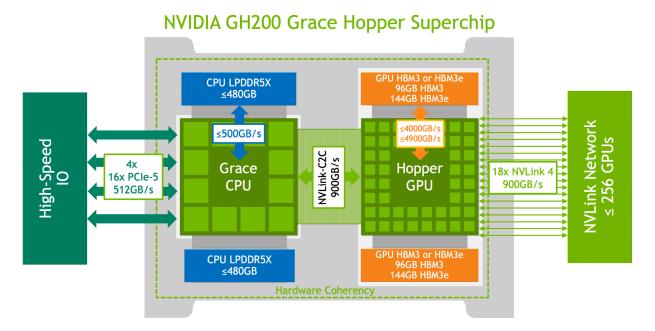

The Grace CPU is found in two data center NVIDIA superchip products. The first is the NVIDIA GH200 Grace Hopper™ Superchip that pairs the power efficient, high-bandwidth NVIDIA Grace CPU with an NVIDIA H100 Tensor Core GPU to maximize the capabilities for accelerated computing and generative AI workloads. The heart of the GH200 Grace Hopper Superchip, is the NVLink-C2C that delivers up to 900 gigabytes per second (GB/s) of total bandwidth, which is 7X higher than PCIe Gen5 lanes commonly used in accelerated systems. NVLink-C2C enables the GPU to have direct access to over 600GB of memory, GH200 runs the full NVIDIA software stack and can be easily deployed in standard servers to run a variety of inference, data analytics, and other compute and memory-intensive workloads.

The second is the NVIDIA Grace CPU Superchip, with 144 cores in a no-compromise CPU for HPC, demanding cloud, and enterprise computing workloads. The Grace CPU Superchip delivers up to 1 TB/s of memory bandwidth, best-in-class data center throughput and up to 2X the performance per watt of today's leading servers.

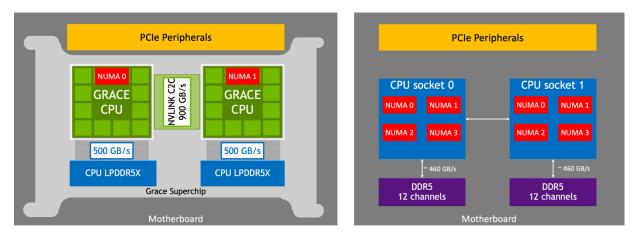

Figure 1-1. NVIDIA Grace CPU Superchip

**NVIDIA Grace CPU Superchip Specifications** Table 1-1.

|                   | Grace CPU Superchip                                        |  |  |

|-------------------|------------------------------------------------------------|--|--|

| Core Architecture | Armv9-A Neoverse V2 Cores with 4x128b SVE2                 |  |  |

| Core Count        | 144                                                        |  |  |

| Cache             | L1: 64KB I-cache + 64KB D-cache per core                   |  |  |

|                   | L2: 1MB per core                                           |  |  |

|                   | L3: 234MB per superchip                                    |  |  |

| Memory Technology | LPDDR5X with ECC in the same package.                      |  |  |

| Raw Memory BW     | Up to 1 TB/s                                               |  |  |

| Memory Size       | Up to 960GB                                                |  |  |

| FP64 Peak         | 7.1 TFLOPS                                                 |  |  |

| PCI Express       | 8x PCle Gen 5 x16 interfaces; with an option to bifurcate. |  |  |

|                   | Total 1 TB/s PCIe Bandwidth.                               |  |  |

|                   | Additional low-speed PCIe connectivity for management.     |  |  |

| Power             | 500W TDP with Memory, 12V Supply                           |  |  |

Table 1-2. NVIDIA GH200 Grace Hopper Superchip Specifications

|                                     | GH200 Grace Hopper Superchip                                              |  |

|-------------------------------------|---------------------------------------------------------------------------|--|

| CPU Core Architecture               | Armv9-A Neoverse V2 Cores with 4x128b SVE2                                |  |

| CPU Core Count                      | 72                                                                        |  |

| CPU Cache                           | L1: 64KB I-cache + 64KB D-cache per core<br>L2: 1MB per core<br>L3: 117MB |  |

| CPU Memory<br>Technology            | LPDDR5X with ECC in the same package.                                     |  |

| CPU Raw Memory BW                   | Up to 500 GB/s                                                            |  |

| CPU Memory Size                     | Up to 480GB                                                               |  |

| GPU Multi-Processor<br>Architecture | Hopper SM compute capability 9.0                                          |  |

| GPU Multi-Processor<br>Count        | 132                                                                       |  |

| GPU Memory<br>Technology            | High-Bandwidth Memory HBM3<br>High-Bandwidth Memory HMB3e                 |  |

| GPU Memory Size                     | 96GB HBM3<br>144GB HBM3e                                                  |  |

|       | GH200 Grace Hopper Superchip          |  |

|-------|---------------------------------------|--|

| Power | 550-1000W TDP with Memory, 12V Supply |  |

#### 1.1.1. High Performance Architecture

The Grace CPU delivers high, single-threaded performance, high memory bandwidth, and outstanding data movement capabilities with leadership performance per watt. To enable the Grace CPU Superchip, these design goals required the development of several innovations.

The Grace Hopper CPU+GPU Superchip combines high performance of the Grace CPU with world-class GPU performance of the NVIDIA H100 GPU.

#### Alleviate Bottlenecks with NVLink-C2C 112 Interconnect

To create the Grace CPU Superchip with up to 144 Arm Neoverse V2 cores and avoid bottlenecks when moving data between the chips, the NVLink Chip-2-Chip (C2C) interconnect provides a high-speed, direct connection between chips. A typical server architecture has two sockets, each composed of multiple dies and each die can represent multiple non-uniform memory (NUMA) domains. The Grace CPU Superchip uses a clean and simple memory topology. With only two NUMA nodes and the high-bandwidth NVLink-C2C, the Grace CPU Superchip helps alleviate NUMA bottlenecks for application developers and users.

Similarly, the memory of the Grace Hopper Superchip is set up as two NUMA nodes connected through the high-bandwidth NVLink-C2C, making access to both CPU and GPU memory seamless for applications developers and users.

Figure 1-2. Comparing the Grace CPU Superchip with NVLink-C2C to the Traditional Server Architecture-Based on X86-64

Figure 1-3. Overview of the Grace + Hopper Superchip System

#### 1.1.3. Scale Cores and Bandwidth with NVIDIA Scalable Coherency Fabric

NVIDIA Scalable Coherency Fabric (SCF), shown in Figure 1-4, is a mesh fabric and distributed cache architecture that is designed by NVIDIA to scale cores and bandwidth. To keep data flowing between the CPU cores, NVLink-C2C, memory, and system IO, SCF provides over 3.2 TB/s of total bisection bandwidth.

The CPU cores and SCF cache partitions are distributed throughout the mesh, and the Cache Switch Nodes route data through the fabric and serve as interfaces between the CPU, cache memory, and system IOs. A Grace CPU Superchip has 234 MB of distributed L3 cache across the two chips.

Figure 1-4. NVIDIA Grace CPU and the NVIDIA Scalable Coherency Fabric

Figure 1-4 shows the NVIDIA Grace CPU and the NVIDIA Scalable Coherency Fabric, which join the Neoverse V2 cores and distributed cache and system IO in a high-bandwidth mesh interconnect.

The Grace CPU supports Memory Partitioning and Monitoring (MPAM), which is the Arm® standard to partition the system cache and memory resources to provide performance isolation between jobs. By using MPAM, the NVIDIA-designed SCF Cache supports the partitioning of cache capacity, I/O, and memory bandwidth. MPAM also supports the use of MPAM performance monitor groups (PMGs) to monitor resources, such as cache storage usage and memory bandwidth usage.

#### 1.1.4. LPDDR5X Memory Subsystem

The Grace CPU Superchip uses up to 960 GB of server-class LPDDR5X memory with Error Correction Code (ECC). This design strikes the optimal balance of bandwidth, energy efficiency, capacity, and cost for large-scale AI and HPC workloads.

Compared to an eight-channel DDR5 design, the Grace CPU LPDDR5X memory subsystem provides up to 53% more bandwidth at 1/8th the power per gigabyte per second while being close in cost. An HBM2e memory subsystem provides substantial memory bandwidth and energy efficiency but at more than three times the cost-per-gigabyte and only one-eighth the maximum capacity with LPDDR5X.

The Grace CPU LPDDR5X architecture is the first data center class, resilient implementation of LPDDR technology. LPDDR5 channel sparing also restores the memory subsystem health upon reboot, which results in a low service rate due to failed memory. This allows the Grace CPU to be deployed in scenarios where serviceability is difficult and expensive.

The co-packaged memory employs a novel provisioning and error detection technique which eliminates the need to service or replace failed memory in the field, allowing the Grace CPU to be deployed in scenarios where serviceability is difficult or costly.

The lower power consumption of LPDDR5X reduces the overall system power requirements and enables more resources to be used in the CPU cores. The compact form factor enables twice the density of a typical DIMM-based design.

### 1.1.5. CPU I/O

The Grace CPU Superchip supports up to 128 lanes of PCIe Gen 5 for I/O connectivity, and each PCle Gen 5 x16 link supports up to 128 GB/s of bi-directional bandwidth and, for additional connectivity, can be bifurcated into 2x8s. Additional PCIe interfaces are provided for system management purposes. Server makers can use the standard expansion options for a variety of PCIe slot form factors with out-of-box support for NVIDIA GPUs, NVIDIA DPUs, NVIDIA ConnectX SmartNICs, E1.S, and M.2 NVMe devices, modular BMC options, and so on.

#### 1.1.6. Grace CPU Core Architecture

The Grace CPU Neoverse V2 core implements the Armv9.0-A architecture, which extends the architecture that was defined in the Armv8-A architectures up to Armv8.5-A. Application binaries that are built for an Armv8 architecture up to Armv8.5-A will execute on NVIDIA Grace, and this includes binaries that target CPUs like the Ampere Altra, the AWS Graviton2, and the AWS Graviton3.

Important: The NVIDIA HPC Compilers compile for fixed-length which are not binary compatible between, for example, Graviton and Grace.

#### 1.1.7. SIMD Vectorization

The Neoverse V2 implements the following single instruction multiple data (SIMD) vector instruction sets in a 4x128-bit configuration:

- The Scalable Vector Extension version 2 (SVE2)

- Advanced SIMD (NEON)

Each of the four 128-bit functional units can retire SVE2 or NEON instructions, and this design allows more codes to take advantage of the SIMD performance.

Many applications and libraries are already taking advantage of Advanced SIMD (also known as NEON). SVE is a length-agnostic next generation SIMD instruction set architecture (orthogonal to Advanced SIMD) and provides features such as prediction, first faulting loads, gather, scatter, the ability to scale to large vector lengths without requiring recompilation, or porting to new vector lengths by hand. SVE2 provides vector length flexibility, which allows software efforts to focus on application specific optimizations.

SVE is implemented in many flagship Arm implementations, and by using length agnostic instructions for Grace CPU accrue toward portable binaries, ensures compatibility with SVE optimizations. SVE2 also extends the SVE ISA with advanced instructions that can accelerate key HPC applications like machine learning, genomics, and cryptography.

Refer to **Compilers** for the command-line options with popular compilers.

#### 1.1.8. **Atomic Operations**

NVIDIA Grace CPU supports the Large System Extension (LSE), which was introduced in Armv8.1. LSE provides the following low-cost atomic operations, which can improve system throughput for CPU-to-CPU communication, locks, and mutexes:

- The Compare and Swap instructions, CAS, and CASP.

- Atomic memory operation instructions, LD<0P> and ST<0P>, where <0P> is ADD, CLR, EOR, SET, SMAX, SMIN, UMAX, or UMIN.

- The Swap procedure, SWP.

These instructions can operate on integer data. All compilers that support the Grace CPU automatically use these instructions in synchronization functions like GCC's \_\_atomic built-ins. When using LSE atomics instead of load/store exclusives, there is a huge improvement. For instance, a shared integer value can be incremented with one atomic ADD instead of the following sequence:

- 1. Load exclusive.

- 2. Add.

- 3. Attempt store exclusive.

- 4. If the operation fails, repeat the sequence.

### 1.1.9. Additional Armv9 Features

The Grace CPU implements multiple key features of the Armv9 portfolio that provide utilities in general purpose data center CPUs, including cryptographic acceleration, scalable profiling extension, virtualization extensions, and secure boot. In addition to standard Armv9 features, Grace also supports full-memory encryption.

# 2. Understanding Your Grace Machine

After you boot up your Grace machine, run sudo ipmitool fru print command and check the information about the NVIDIA Grace module.

Here is the sample output from a Grace CPU Superchip machine. The **FRU Device Description** is PG535, and the **Product Name** is C2.

```

FRU Device Description : PG535 (ID 192)

Board Mfg Date : [REDACTED]

Board Mfg : NVIDIA

Board Product : PG535

Board Serial : [REDACTED]

Board Part Number : 699-2G535-0200-DV2

Product Manufacturer : NVIDIA

Product Name : C2

Product Part Number : 900-2G535-0000-000

Product Version : B-R00

Product Serial : [REDACTED]

```

Here is the sample output from a Grace Hopper Superchip machine. The **FRU Device Description** is PG530, and the **Product Name** is GH200.

```

FRU Device Description : PG530 (ID 133)

Board Mfg Date : [REDACTED]

Board Mfg : NVIDIA

Board Product : PG530

Board Serial : [REDACTED]

Board Part Number : 699-2G530-0206-QS1

Product Manufacturer : NVIDIA

Product Name : GH200 480GB

Product Part Number : 900-2G530-0000-000

Product Version : A-R00

Product Serial : [REDACTED]

```

### 2.1. Checking the CPUs

The 1scpu command-line utility in Linux gets CPU information about the system, fetches the CPU architecture information from the sysfs and /proc/cpuinfo files, and displays the information in a terminal.

After you boot your Grace machine, run the 1scpu command and check the CPUs.

Here is the sample output from a Grace CPU Superchip machine:

```

Architecture:

aarch64

CPU op-mode(s):

64-bit

Little Endian

Byte Order:

CPU(s):

144

On-line CPU(s) list: 0-143

Vendor ID:

ARM

Model:

Thread(s) per core: 1

Core(s) per socket: 72

Socket(s):

Stepping:

r0p0

Frequency boost:

disabled

CPU max MHz:

3582.0000

CPU min MHz:

81.0000

BogoMIPS:

2000.00

fp asimd evtstrm aes pmull sha1 sha2 crc32 atomics fphp a

Flags:

simdhp cpuid asimdrdm jscvt fcma lrcpc dcpop sha3 sm3 sm4

asimddp sha512 sve asimdfhm dit uscat ilrcpc flagm ssbs

sb paca pacg dcpodp sve2 sveaes svepmull svebitperm svesh

a3 svesm4 flagm2 frint svei8mm svebf16 i8mm bf16 dgh bti

Caches (sum of all):

L1d:

9 MiB (144 instances)

L1i:

9 MiB (144 instances)

L2:

144 MiB (144 instances)

13:

228 MiB (2 instances)

NUMA:

NUMA node(s):

NUMA node0 CPU(s):

0-71

NUMA node1 CPU(s):

72-143

Vulnerabilities:

Not affected

Itlb multihit:

L1tf:

Not affected

Mds:

Not affected

Not affected

Meltdown:

Mmio stale data:

Not affected

Not affected

Retbleed:

Spec store bypass:

Mitigation; Speculative Store Bypass disabled via prctl

Spectre v1:

Mitigation; __user pointer sanitization

Not affected

Spectre v2:

```

```

Srbds: Not affected

Tsx async abort: Not affected

```

From this output, you can see information such as the number of CPU sockets, how many cores per socket, how many hardware threads per core, and the max/min CPU frequency. You can also find the size of the L1, the L2, and the L3 caches.

Here is the sample output of a Grace Hopper Superchip system:

```

Architecture:

aarch64

CPU op-mode(s):

64-bit

Byte Order:

Little Endian

CPU(s):

72

On-line CPU(s) list: 0-71

Vendor ID:

Model:

Thread(s) per core: 1

Core(s) per socket: 72

Socket(s):

1

Stepping:

r0p0

Frequency boost:

disabled

CPU max MHz:

3591.0000

CPU min MHz:

81.0000

BogoMIPS:

2000.00

Flags:

fp asimd evtstrm aes pmull sha1 sha2 crc32 atomics fphp

asimdhp

cpuid asimdrdm jscvt fcma lrcpc dcpop sha3 sm3 sm4

asimddp sha

512 sve asimdfhm dit uscat ilrcpc flagm ssbs sb paca pacg

dcpod

p sve2 sveaes svepmull svebitperm svesha3 svesm4 flagm2

frint s

vei8mm svebf16 i8mm bf16 dgh bti

Caches (sum of all):

L1d:

4.5 MiB (72 instances)

4.5 MiB (72 instances)

L1i:

L2:

72 MiB (72 instances)

114 MiB (1 instance)

L3:

NUMA:

NUMA node(s):

NUMA node0 CPU(s):

0-71

NUMA node1 CPU(s):

NUMA node2 CPU(s):

NUMA node3 CPU(s):

NUMA node4 CPU(s):

NUMA node5 CPU(s):

NUMA node6 CPU(s):

NUMA node7 CPU(s):

NUMA node8 CPU(s):

Vulnerabilities:

Itlb multihit:

Not affected

```

L1tf: Not affected Not affected Mds: Meltdown: Not affected Mmio stale data: Not affected Retbleed: Not affected

Spec store bypass: Mitigation; Speculative Store Bypass disabled via prctl

Spectre v1: Mitigation; \_\_user pointer sanitization

Spectre v2: Not affected Srbds: Not affected Tsx async abort: Not affected

Note: This output shows nine NUMA nodes. The first node corresponds to the Grace CPU, the second to the Hopper GPU, and the remaining seven nodes correspond to NVIDIA Multi-Instance GPU (MIG) instances.

The seven MIG instances can be ignored if MIG mode is not being used.

# 2.2. Checking the Non-Uniform Memory **Access Settings**

The 1scpu output includes basic information about the Non-Uniform Memory Access (NUMA) settings on your Grace machine.

To understand more about the NUMA settings, run the numact1 -H command, and here is the sample output from a Grace Superchip machine:

```

available: 2 nodes (0-1)

node 0 cpus: 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30

31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62

63 64 65 66 67 68 69 70 71

node 0 size: 245090 MB

node 0 free: 99633 MB

node 1 cpus: 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99

100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123

124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 141 142 143 144

node 1 size: 245317 MB

node 1 free: 126895 MB

node distances:

node 0 1

0: 10 40

1: 40 10

```

The output shows that there are two NUMA nodes on this machine, the number of cores on each NUMA node, and how much memory is available for each node. The output also shows the node distances between NUMA nodes, which helps the Kernel scheduler execute application threads on CPU cores that are closest to the memory resident data.

Here is the sample output from a Grace + Hopper Superchip system:

```

available: 9 nodes (0-8)

node 0 cpus: 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26

27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54

55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71

node 0 size: 490310 MB

node 0 free: 166560 MB

node 1 cpus:

node 1 size: 95232 MB

node 1 free: 92094 MB

node 2 cpus:

node 2 size: 0 MB

node 2 free: 0 MB

node 3 cpus:

node 3 size: 0 MB

node 3 free: 0 MB

node 4 cpus:

node 4 size: 0 MB

node 4 free: 0 MB

node 5 cpus:

node 5 size: 0 MB

node 5 free: 0 MB

node 6 cpus:

node 6 size: 0 MB

node 6 free: 0 MB

node 7 cpus:

node 7 size: 0 MB

node 7 free: 0 MB

node 8 cpus:

node 8 size: 0 MB

node 8 free: 0 MB

node distances:

node 0 1 2 3

4 5 6 7 8

0: 10 80 80 80 80 80 80 80 80

1: 80 10 255 255 255 255 255 255 255

```

```

2: 80 255 10 255 255 255 255 255 255 255

3: 80 255 255 10 255 255 255 255 255

4: 80 255 255 255 255 255 255 255 255

5: 80 255 255 255 255 255 255 255 255

6: 80 255 255 255 255 255 255 255 255

7: 80 255 255 255 255 255 255 255 255 10 255

8: 80 255 255 255 255 255 255 255 255 10 255

```

As noted in <u>Checking the CPUs</u>, the last seven NUMA nodes can be ignored if MIG is not used.

### 2.3. Checking the GPU

Running the nvidia-smi command displays the status of the GPU in the system.

Here is sample output from a Grace Hopper Superchip system:

```

+-----+

|-----+

Persistence-M | Bus-Id Disp.A | Volatile Uncorr. ECC |

| Fan Temp Perf Pwr:Usage/Cap | Memory-Usage | GPU-Util Compute M. |

MIG M. |

|------

Off | 00000009:01:00.0 Off |

0 GH200 480GB

0 |

Processes:

GPU GI CI PID Type Process name

GPU Memory |

ID ID

Usage

|-----|

No running processes found

```

### 2.4. Checking the Memory

One of the common ways of checking the memories on your Grace system is to run the sudo dmidecode -t memory command. Here is the sample output from a Grace-Grace machine:

```

# dmidecode 3.3

Getting SMBIOS data from sysfs.

SMBIOS 3.6.0 present.

# SMBIOS implementations newer than version 3.5.0 are not

# fully supported by this version of dmidecode.

Handle 0x000B, DMI type 16, 23 bytes

Physical Memory Array

Location: System Board Or Motherboard

Use: System Memory

Error Correction Type: Single-bit ECC

Maximum Capacity: 480 GB

Error Information Handle: No Error

Number Of Devices: 2

Handle 0x000C, DMI type 17, 92 bytes

Memory Device

Array Handle: 0x000B

Error Information Handle: 0x0000

Total Width: 540 bits

Data Width: 480 bits

Size: 240 GB

Form Factor: Die

Set: None

Locator: Not Specified

Bank Locator: Not Specified

Type: LPDDR5

Type Detail: None

Speed: Unknown

Manufacturer: Not Specified

Serial Number: 9223381974177924187

Asset Tag: Not Specified

Part Number: Not Specified

Rank: 1

Configured Memory Speed: Unknown

Minimum Voltage: Unknown

Maximum Voltage: Unknown

Configured Voltage: Unknown

Memory Technology: DRAM

Memory Operating Mode Capability: None

Firmware Version: Not Specified

Module Manufacturer ID: Unknown

Module Product ID: Unknown

Memory Subsystem Controller Manufacturer ID: Unknown

```

Memory Subsystem Controller Product ID: Unknown

Non-Volatile Size: None Volatile Size: None Cache Size: None Logical Size: None

Handle 0x000D, DMI type 17, 92 bytes

Memory Device

Array Handle: 0x000B

Error Information Handle: 0x0000

Total Width: 540 bits Data Width: 480 bits

Size: 240 GB Form Factor: Die

Set: None

Locator: Not Specified Bank Locator: Not Specified

Type: LPDDR5

Type Detail: None

Speed: Unknown

Manufacturer: Not Specified

Serial Number: 9223382071351559259

Asset Tag: Not Specified Part Number: Not Specified

Rank: 1

Configured Memory Speed: Unknown

Minimum Voltage: Unknown Maximum Voltage: Unknown Configured Voltage: Unknown Memory Technology: DRAM

Memory Operating Mode Capability: None

Firmware Version: Not Specified Module Manufacturer ID: Unknown Module Product ID: Unknown

Memory Subsystem Controller Manufacturer ID: Unknown Memory Subsystem Controller Product ID: Unknown

Non-Volatile Size: None Volatile Size: None Cache Size: None Logical Size: None

You can see from the output that there are two zones of LPDDR5 memories, each with 240GB, and each zone is from one Grace chip.

# 3. Basic System Health Checks

To confirm that your system is healthy and is correctly configured, check the compute performance and memory bandwidth with some simple benchmarks.

### 3.1. STREAM

Use the STREAM benchmark to check LPDDR5X memory bandwidth. The following commands download and compile STREAM with a total memory footprint of approximately 2.7GB, which is sufficient to exceed the L3 cache without excessive runtime.

Note: We recommend GCC version 12.3 or later.

```

$ wget https://www.cs.virginia.edu/stream/FTP/Code/stream.c

$ gcc -Ofast -mcpu=neoverse-v2 -fopenmp \

-DSTREAM_ARRAY_SIZE=120000000 -DNTIMES=200 \

-o stream_openmp.exe stream.c

```

To run STREAM, set the number of OpenMP threads (OMP\_NUM\_THREADS) according to the example below. Use OMP\_PROC\_BIND=spread to distribute the threads evenly over all available cores and maximize bandwidth.

```

$ OMP_NUM_THREADS={THREADS} OMP_PROC_BIND=spread ./stream_openmp.exe

```

System bandwidth is proportional to the memory capacity. Find your system's memory capacity in the table below and use the given parameters to generate the expected score for STREAM TRIAD. For example, when running on a Grace-Hopper superchip with a memory capacity of 120GB, this command will score at least 450GB/s in STREAM TRIAD:

```

$ OMP_NUM_THREADS=72 OMP_PROC_BIND=spread ./stream_openmp.exe

```

Similarly, this command will score at least 900GB/s in STREAM TRIAD on a Grace CPU Superchip with a memory capacity of 240GB:

\$ OMP\_NUM\_THREADS=144 OMP\_PROC\_BIND=spread numactl -m0,1 ./stream\_openmp.exe

Table 3-1. Expected STREAM TRIAD Scores

| Superchip    | Capacity (GB) | OMP_NUM_THREADS | Expected TRIAD<br>Bandwidth |

|--------------|---------------|-----------------|-----------------------------|

| Grace-Hopper | 120           | 72              | 450+                        |

| Grace-Hopper | 480           | 72              | 340+                        |

| Grace CPU    | 240           | 144             | 900+                        |

| Grace CPU    | 480           | 144             | 900+                        |

| Grace CPU    | 960           | 144             | 680+                        |

```

$ OMP_NUM_THREADS=72 OMP_PROC_BIND=spread numactl -m0,1 ./stream_openmp.exe

______

STREAM version $Revision: 5.10 $

_____

This system uses 8 bytes per array element.

Array size = 120000000 (elements), Offset = 0 (elements)

Memory per array = 915.5 MiB (= 0.9 GiB).

Total memory required = 2746.6 MiB (= 2.7 GiB).

Each kernel will be executed 200 times.

The *best* time for each kernel (excluding the first iteration)

will be used to compute the reported bandwidth.

_____

Number of Threads requested = 72

Number of Threads counted = 72

Your clock granularity/precision appears to be 1 microseconds.

Each test below will take on the order of 2927 microseconds.

(= 2927 clock ticks)

Increase the size of the arrays if this shows that

you are not getting at least 20 clock ticks per test.

______

WARNING -- The above is only a rough guideline.

For best results, please be sure you know the

precision of your system timer.

Function Best Rate MB/s Avg time Min time

```

```

Copy:

919194.6

0.002149

0.002089

0.002228

Scale:

913460.0

0.002137

0.002102

0.002192

Add:

916926.9

0.003183

0.003141

0.003343

0.003223

Triad:

903687.9

0.003187

0.003308

Solution Validates: avg error less than 1.000000e-13 on all three arrays

```

### 3.2. Fused Multiply Add

NVIDIA provides an open source suite of benchmarking microkernels for Arm CPUs. To allow precise counts of instructions and exercise specific functional units, these kernels are written in assembly language. To measure the peak floating point capability of a core and check the CPU clock speed, use a Fused Multiply Add (FMA) kernel.

To measure achievable peak performance of a core, the fp64\_sve\_pred\_fmla kernel executes a known number of SVE predicated fused multiply-add operations (FMLA). When combined with the perf tool, you can measure the performance and the core clock speed.

```

$ git clone https://github.com/NVIDIA/arm-kernels.git

$ cd arm-kernels

$ make

$ perf stat ./arithmetic/fp64_sve_pred_fmla.x

```

The benchmark score is reported in giga-operations per second (Gop/sec) near the top of the benchmark output. Grace can perform 16 FP64 FMA operations per cycle, so a Grace CPU with a nominal CPU frequency of 3.3GHz should report between 52 and 53 Gop/sec. The CPU frequency is reported in the perf output on the cycles line and after the # symbol.

Here is an example of the fp64\_sve\_pred\_fmla.x execution output:

```

$ perf stat ./arithmetic/fp64_sve_pred_fmla.x

4( 16(SVE_FMLA_64b) );

Iterations; 100000000

Total Inst;6400000000

Total Ops;25600000000

Inst/Iter:64

Ops/Iter;256

Seconds; 0.481267

GOps/sec;53.1929

Performance counter stats for './arithmetic/fp64_sve_pred_fmla.x':

482.25 msec task-clock

0.996 CPUs utilized

0

context-switches

0.000 /sec

0.000 /sec

cpu-migrations

```

```

65

page-faults

# 134.786 /sec

1,607,949,685

cycles

#

3.334 GHz

6,704,065,953

instructions

4.17 insn per cycle

<not supported>

branches

18,383

branch-misses

0.00% of all branches

0.484136320 seconds time elapsed

0.482678000 seconds user

0.000000000 seconds sys

```

### 3.3. C2C CPU-GPU Bandwidth

NVIDIA provides an open-source benchmark, similar to STREAM, that is designed to test the bandwidth between various memory units on the system. This can be used to test the bandwidth provided by NVLink C2C between the CPU and GPU of a Grace Hopper Superchip.

Download, build, and run nvbandwidth:

```

git clone https://github.com/NVIDIA/nvbandwidth.git

cd nvbandwidth

# may need to update version of CUDA

docker run -it --rm --gpus all -v $(pwd):/nvbandwidth nvidia/cuda:12.2.0-devel-ubuntu22.04

# within docker

cd /nvbandwidth

apt update

apt install libboost-program-options-dev

./debian_install.sh

./nvbandwidth -t 0

# next test

./nvbandwidth -t 1

# all tests can be listed with ./nvbandwidth -l

```

Here is the output from the previous two commands on a sample system:

Note: Bandwidth numbers depend on specific Grace Hopper SKUs and are also influenced by factors such as IOMMU settings, GPU clock settings, and other system-specific parameters. These factors should be carefully considered during any bandwidth benchmarking activity.

```

# ./nvbandwidth -t 0

nvbandwidth Version: v0.2

Built from Git version:

NOTE: This tool reports current measured bandwidth on your system.

Additional system-specific tuning may be required to achieve maximal peak

bandwidth.

CUDA Runtime Version: 12020

CUDA Driver Version: 12020

Driver Version: 535.82

Device 0: GH200 120GB

Running host_to_device_memcpy_ce.

memcpy CE CPU(row) -> GPU(column) bandwidth (GB/s)

416.34

SUM host_to_device_memcpy_ce 416.34

# ./nvbandwidth -t 1

nvbandwidth Version: v0.2

Built from Git version:

NOTE: This tool reports current measured bandwidth on your system.

Additional system-specific tuning may be required to achieve maximal peak

bandwidth.

```

```

CUDA Runtime Version: 12020

CUDA Driver Version: 12020

Driver Version: 535.82

Device 0: GH200 120GB

Running device_to_host_memcpy_ce.

memcpy CE CPU(row) <- GPU(column) bandwidth (GB/s)</pre>

295.47

SUM device_to_host_memcpy_ce 295.47

```

For memory copies that use CUDA copy engines (CEs), you should expect similar numbers as shown in the output for systems with 120GB or 240GB of LPDDR5 memory.

Systems with 480GB LPDDR5 memory might have a lower bandwidth for host-to-device copies (compared to the first test output shown above). On a healthy system, this bandwidth should be approximately 350-360 GB/s.

Systems with 480GB LPDDR5 should have similar device-to-host bandwidth as shown above in the second test, except Grace-Hopper x4 systems, where this bandwidth should be approximately 170 GB/s due to more CEs being reserved for saturating NVLink bandwidth between GPUs.

To run bandwidth tests using the GPU's streaming micro-processors (SMs), run the ./nvbandwidth -1 command for the exact test numbers. The achieved bandwidth should be at least as large as the outputs shown by CE-based tests.

### 4. Power and Thermals

This chapter provides information about CPU power and thermal management settings.

### 4.1. C-States

C-States refer to idle CPU power states, and Grace includes the following C-states:

C0: active/run state.

This is the state of the CPU core while active.

C1: clock gated state.

This state is entered when WFI/WFE instructions are executed by the CPU core. The latency to enter/exit this state is negligible.

The LPI table in Advanced Configuration and Power Interface (ACPI) provides information about the C-states to any CPU idle governors such as the cpuilde framework in Linux.

For systems that have the cpuidle governors enabled, the number of times the C1 state is entered through the idle framework can be read by running the following command:

\$ cat /sys/devices/system/cpu/cpu<n>/cpuidle/state1/usage

For systems that do not use cpuidle governors, the cpu cores can still enter clock gated state when WFI/WFE instructions are executed, but no stats will be available.

### 4.2. P-States

P-States refers to performance states, and Grace does not offer explicit P-states. Instead, Grace exposes the maximum and minimum performance capabilities through ACPI's CPPC mechanism. CPPC offers users and operating systems the ability to request any performance in the allowed bounds rather than discrete P-State. Refer to CPU Performance and Frequency Management for more information.

# 4.3. CPU Performance and Frequency Management

Each CPU core can operate at its own independent frequency, and the frequency is determined by the frequency policy governors that were used. Linux provides the following frequency governors:

- **Performance governor**: Geared towards getting the maximum performance and sets the performance/frequency request of the CPU cores to the maximum possible value.

- The request is not based on activity and kept fixed at highest value.

- Userspace governor: Bypasses a kernel governor and provides control to the userspace application for frequency control.

- To set the frequency of the cores, a hypervisor, or a higher level software entity, can take input from an application. The kernel does not modify the frequency based on other information but will honor frequency caps based on thermals.

- Schedutil governor: Incorporates information from the scheduler, which are the threads that are currently scheduled on cores, the activity on the core, load estimation, and so on, to determine the optimal frequency for the core.

- The goal of this governor is to provide best performance while saving power by matching the frequency based on scheduler visible workloads.

- Ondemand governor: Adjusts the frequency based on the trailing load of the CPU core.

This governor predicts the future load and ramps frequency accordingly.

Refer to <a href="https://www.kernel.org/doc/Documentation/cpu-freg/governors.txt">https://www.kernel.org/doc/Documentation/cpu-freg/governors.txt</a> for more information.

The default frequency governor in Grace is the performance governor, which sets the frequency to the maximum value for that core. The maximum frequency usually corresponds to the maximum possible performance and is higher than the frequency at which nominal (sustained) performance can be achieved. When running at the maximum frequency violates thermals, the thermal management solution throttles frequency. Refer to **Power and Thermal Management** for more information.

Managing CPU frequency on a Linux server can be achieved by using the cpufreq commands or directly by using the sysfs interface. The next section provides a concise guide that combines the methods for setting a fixed frequency and a scaling max frequency.

#### 4.3.1. Setting a Fixed Frequency

This section provides information about setting a fixed frequency.

#### The cpufreq cCommand

This command allows you do complete the following tasks::

• Switch to userspace governor to manually set the frequency:

```

$ sudo cpufreq-set -g userspace

```

• Set the desired frequency (e.g., 3.2 GHz = 3200000 kHz):

```

$ sudo cpufreq-set -f 3200000

```

#### The sysfs mMethod:

This command allows you do complete the following tasks:

• Switch to userspace governor (if supported):

```

$ echo userspace | sudo tee

/sys/devices/system/cpu/cpu*/cpufreq/scaling_governor

```

• Set the desired frequency directly (replace [FREQUENCY] with your value in kHz):

```

$ echo [FREQUENCY] | sudo tee

/sys/devices/system/cpu/cpu*/cpufreq/scaling_setspeed

```

#### Setting a Scaling Max Frequency 432

This section provides information about setting a scaling max frequency.

#### • The cpufreg command

• Switch to performance governor to limit the max scaling frequency:

```

$ sudo cpufreq-set -g performance

```

• Set the scaling max frequency (e.g., 3.2 GHz = 3200000 kHz):

```

$ sudo cpufreq-set -u 3200000

```

#### The sysfs method

Switch to performance governor (if supported):

```

$ echo performance | sudo tee

/sys/devices/system/cpu/cpu*/cpufreq/scaling_governor

```

Limit the maximum scaling frequency (by replacing [MAX\_FREQUENCY] with your value in kHz):

```

$ echo [MAX_FREQUENCY] | sudo tee

/sys/devices/system/cpu/cpu*/cpufreq/scaling_max_frequency

```

Here are general CPU frequency commands that you can use to read the currently requested and measured settings:

- Software frequency request (kHz) for the CPU core <n>. \$ cat /sys/devices/system/cpu/cpu<n>/cpufreq/scaling\_cur\_freq

- Measured frequency (kHz).

- \$ cat /sys/devices/system/cpu/cpu<n>/cpufreq/cpuinfo\_cur\_freq

Note: This makes use of AMU (actmon), which is provided by ARM, where the source and reference clocks are measured, and where the ratio is used to compute the actual frequency. With the default measuring window used in Linux, there might be up to a 3% error in the frequency read. To increase accuracy, the measurement window should be increased in upstream Linux code.

### **GPU** and Module Power Management

GPU provides power capping at the following scopes:

- Limit power consumption of the Grace + Hopper superchip (Module) and keep it within the provided power limit.

- Limit power consumption of the GPU and keep it within the provided power limit.

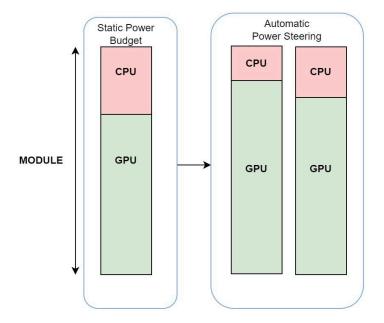

Figure 4-1: GPU and Module Power Management

This is done by Automatic power steering in the GPU because the GPU monitors power telemetry for Grace, Module, and the GPU. Power capping at the Module scope works on monitoring the consumed Grace power, removing that from the Module power limit, and giving the rest to the GPU.

The GPU can work within the new power limit or can stick to the limit that was explicitly set for the GPU, where the lower of the two limits is respected. This leads to efficiently balancing power between Grace and GPU to improve overall app perf by opportunistically boosting the GoPU power budget. The GPU achieves power capping by using DVFS.

Table 4-1. **Power Management**

| System | Knobs                                                  | Description                                                                                                                          |

|--------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| GPU    | nvidia-smi -q -d POWER                                 | Dumps Module and GPU power temetry                                                                                                   |

| GPU    | nvidia-smi -pl <limit in="" watt=""> -sc<br/>0</limit> | Sets limit for the GPU. This will apply to the GPU if the limit is lower than the limit evaluated through "Automatic Power Steering" |

| GPU    | nvidia-smi -pl <limit in="" watt=""> -sc<br/>1</limit> | Sets limit for the Module                                                                                                            |

#### Here is the output from the NVSMI log:

```

nvidia@localhost:~$ nvidia-smi -q -d POWER

========NVSMI LOG=========

: Fri Oct 6 22:46:55 2023

Timestamp

Driver Version

: 535.122

CUDA Version

: 12.2

Attached GPUs

: 1

GPU 00000009:01:00.0

GPU Power Readings

Power Draw

: 77.61 W

Current Power Limit

: 900.00 W

Requested Power Limit

Default Power Limit

: 900.00 W

: 900.00 W

Min Power Limit

: 100.00 W

: 900.00 W

Max Power Limit

Power Samples

Duration

: 2.36 sec

Number of Samples

: 119

Max

: 78.26 W

Min

: 76.65 W

: 77.48 W

Module Power Readings

Power Draw

: 147.49 W

Current Power Limit

: 1000.00 W

```

```

Requested Power Limit

: 1000.00 W

Default Power Limit

: 1000.00 W

Min Power Limit

: 200.00 W

Max Power Limit

: 1000.00 W

```

### 4.5. Power and Thermal Management

Grace provides the following types of thermal management types:

- Limit power consumption and keep it within the provided power limit.

- Thermal sensor (Tj)-based management.

### 4.6. Power Telemetry

This section provides information about power telemetries for Grace, and guidance for comparing Grace power telemetry to Intel and AMD power telemetry. This can be useful when making comparisons in power efficiency to other CPU architectures.

#### **Grace Power Telemetry** 4.6.1.

Grace exposes power telemetry through hwmon, which uses the ACPI power meter interface. You can read the power telemetry information in one of the following ways:

- To display the name of the power meter.

- This gives information about which power is being reported on humon node X.

- cat /sys/class/hwmon/hwmonX/device/power1\_oem\_info

- To display power consumption, which is average power over past 50ms interval by default, on hymon node x:

- cat /sys/class/hwmon/hwmonX/device/power1\_average

- To display the power stats interval in milliseconds, on hwmon node X: cat /sys/class/hwmon/hwmonX/device/power1\_average\_interval

- To change the power stats interval in milliseconds, on hwmon node X (default is 50): echo <value> | sudo tee /sys/class/hwmon/hwmonX/device/power1\_average\_interval

Table 4-2 provides information about the available power telemetry.

Note: To see hwmon sysfs nodes, you need CONFIG\_SENSORS\_ACPI\_POWER=m in kconfig.

Refer to the NVIDIA Grace Platform Support Software Patches and Configurations guide for more information about the patches.

Table 4-2. Available Power Telemetries

| System                    | Telemetry             | Details                                                                                                           |

|---------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------|

| Grace Superchip           | Grace Power Socket 0  | Total power of the socket 0, including DRAM power and regulator loss.                                             |

|                           | CPU Power Socket 0    | CPU rail power for socket 0.                                                                                      |

|                           | SysIO Power Socket 0  | SOC rail power.                                                                                                   |

|                           | Grace Power Socket 1  | Total power of the socket 1, including DRAM power and regulator loss.                                             |

|                           | CPU Power Socket 1    | CPU rail power for socket 1.                                                                                      |

|                           | SysIO Power Socket 1  | SOC rail power.                                                                                                   |

| Grace Hopper<br>Superchip | Module Power Socket 0 | Total power of the CG1 module, including DRAM power and regulator loss. This also includes GPU and GPU HBM Power. |

|                           | Grace Power Socket 0  | Power of Grace socket.                                                                                            |

|                           | CPU Power Socket 0    | CPU rail power.                                                                                                   |

|                           | SysIO Power Socket 0  | SOC rail power.                                                                                                   |

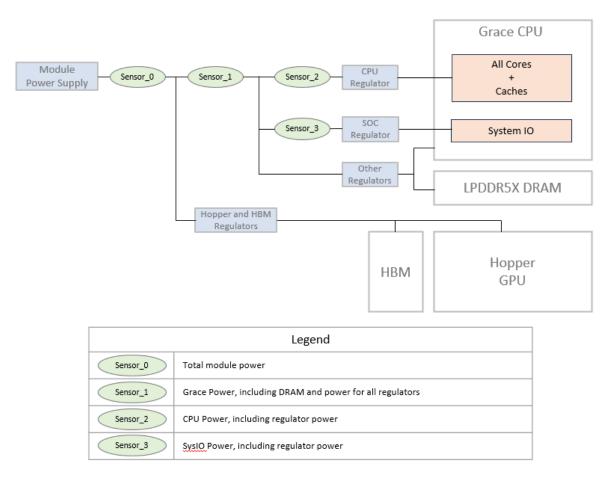

Figure 4-2. **Grace Power Telemetry Sensors**

### **Grace Hopper Superchip Telemetry**

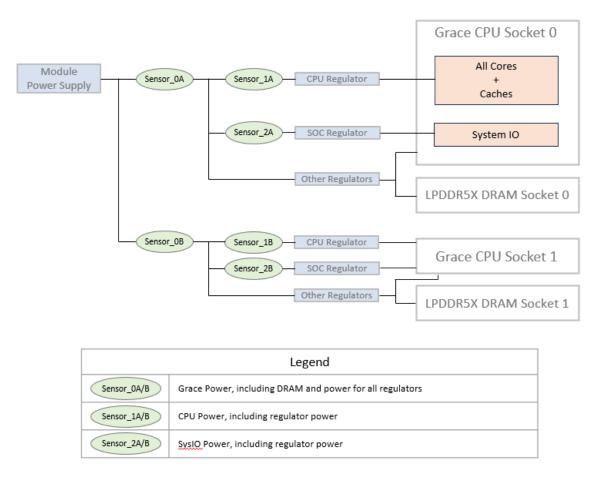

Figure 4-3. **Grace SuperChip Telemetry Sensors**

### **Grace Superchip Telemetry**

As noted in <u>Table 4-2</u>, the total power reported for the socket includes CPU power, DRAM power, and regulator loss. Similarly, power is reported for the CPU cores and includes regulator losses.

Regulator loss accounts for 15% of the TDP power limit.

DRAM power can be estimated based on total traffic using the formula in <u>Table 4-3</u>.

Table 4-3. **Estimating DRAM Power**

| Config         | а           | b     | С     |

|----------------|-------------|-------|-------|

| 128GB, 4266MHz | `00.0000136 | `28.9 | `2334 |

| 128GB, 3200MHz | `00.0000175 | `28.3 | `2043 |

| Config                                                                            | a | b     | С     |  |

|-----------------------------------------------------------------------------------|---|-------|-------|--|

| 512GB, 3200MHz \`00.0000603                                                       |   | `56.2 | `3396 |  |

| DRAM Power (mW, without regulator losses):  a*DRAM_BW_GBps^2 + b*DRAM_BW_GBps + c |   |       |       |  |

The DRAM bandwidth can be determined using the PMU metrics described in Grace CPU Performance Metrics.

#### 4.6.2. Comparing Grace and Intel® Power Telemetry

Intel® CPUs expose power telemetry through the Intel® Performance Counter Monitor (Intel® PCM) APIs. When the power consumption of Grace CPUs is compared to Intel® CPUs, these APIs can be used to gather comparable metrics.

The PCM APIs are available on GitHub at <a href="https://github.com/intel/pcm">https://github.com/intel/pcm</a>.

Refer to the following documentation for more information:

- Building from the source (<a href="https://github.com/intel/pcm#building-pcm-tools">https://github.com/intel/pcm#building-pcm-tools</a>,

- Installing precompiled binaries (https://github.com/intel/pcm#downloading-pre-compiled-pcm-tools)

PCM's pcm-power utility can be run to collect performance metrics for a number of intervals and the duration per interval. For example, to capture one minute of samples at one-second intervals, run the following command:

```

sudo pcm-power 1.00 -i=60 -silent

```

For each interval, pcm-power prints the power consumption for each socket (S0, S1) including CPU power consumption and DRAM power consumption:

```

$ sudo pcm-power -silent 1.0 -i=60 | grep '^S.; Consumed'

S0; Consumed energy units: 3563683; Consumed Joules: 217.51; Watts: 217.51

S0; Consumed DRAM energy units: 533250; Consumed DRAM Joules: 32.55; DRAM Watts: 32.55

S1; Consumed energy units: 3350361; Consumed Joules: 204.49; Watts: 204.49

S1; Consumed DRAM energy units: 597938; Consumed DRAM Joules: 36.50; DRAM Watts: 36.50

```

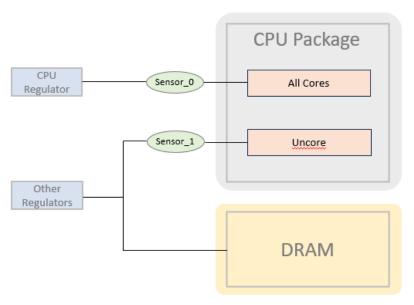

Figure 4-4. **Intel Power Telemetry Sensors**

### Intel Power Telemetry

(Based on Sapphire Rapid)

| Legend      |                                                                                                               |  |

|-------------|---------------------------------------------------------------------------------------------------------------|--|

| Grey area   | Package power as reported by PCM tool (excluding regulator power, except for internal LDOs/FIVR)              |  |

| Yellow area | DRAM Power as reported by PCM tool (excluding regulator power)                                                |  |

| Sensor_0    | Power for all cores, as reported by intel-rapl:0:0 (excluding regulator power, except for internal LDOs/FIVR) |  |

| Sensor_1    | Uncore power, as reported by intel-rapl:0:1 (excluding regulator power)                                       |  |

As illustrated in Figure 4-4, the power consumption per socket does not include regulator losses, and so is not directly comparable to the CPU Power Socket O and CPU Power Socket 1 telemetry as described in <u>Table 4-2</u>. To compare Intel CPU power consumption to Grace CPU power, remove the Grace regulator losses.

For more information about Power consumption metrics that are available through the Linux powercap kernel interface in sysfs, go to Power Capping Framework.

To measure power consumption for cores only, excluding regulator losses or DRAM power consumption, the metrics per CPU are available at:

#### For CPU 0:

cat /sys/class/powercap/intel-rapl/intel-rapl:0/intel-rapl:0:0/energy\_uj

#### For CPU 1:

cat /sys/class/powercap/intel-rapl/intel-rapl:1/intel-rapl:1:0/energy\_uj

These counters provide a running total of the microjoules consumed for each CPU.

Measurements from this interface are comparable to the CPU Power Socket 0 and CPU Power Socket 1 telemetry as described in Table 4-2.

#### Comparing Grace and AMD Power Telemetry 4.6.3.

AMD's AMD µProf package includes utilities that provide power telemetry. When you compare the power consumption of Grace CPUs to AMD CPUs, these APIs can be used to gather comparable metrics.

To download and install the AMD µProf, go to https://www.amd.com/en/developer/uprof.html.

Refer to the AMD µProf User Guide for platform-specific information about the available metrics.

To capture measurements of power consumption per socket for 60 seconds with measurements at one-second intervals, run the following command:

```

AMDuProfCLI-bin timechart --event socket=0-1, power --interval 1000 --duration 60 -o

powerOutput

```

The resulting output file, in a CSV format, will be reported in the command output, for example:

```

Live Profile Output file :

/home/nvex/powerOutput/AMDuProf-SWP-Timechart_Aug-05-2023_00-03-29/timechart.csv

```

It contains CSV-formatted power measurements per interval, with one column per socket, for example:

```

RecordId, Timestamp, socket0-package-power, socket1-package-power

1,0:3:30:462, 95.56, 91.05

2,0:3:31:462, 95.09,

90.63

3,0:3:32:462, 95.17, 90.23

4,0:3:33:462, 95.70, 90.70

```

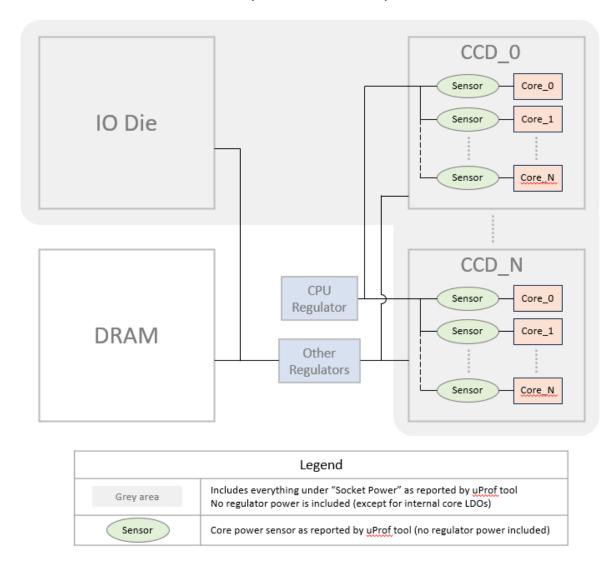

Figure 4-5. AMD Power Telemetry Sensors

# **AMD Power Telemetry**

(Based on Genoa)

Guidance for measuring power usage for the DRAM with AMD processors depends on platform implementation details. Contact your platform vendor for guidance about measuring power usage for comparison to the measurements LPDDR5x power readings with Grace.

AMD µProf also allows per-core power utilization measurements to be captured. For example, on a 64 core AMD processor:

AMDuProfCLI-bin timechart --event core=0-63, power --interval 1000 --duration 60 -o powerOutput

The resulting file contains CSV-formatted power measurements per interval, with one column per core. These cores are summed to get the total power output across all cores to determine total power consumption by the CPU. As illustrated in <u>Figure 4-5</u>, this measurement does not include regulator losses. When regulator losses are removed from the Grace CPU measurement the total is comparable to the Grace CPU rail power CPU Power Socket 0 or CPU Power Socket 1 telemetries as described in <u>Table 4-2</u>,.

# 4.7. Power Capping

Power capping limits average power consumption and is usually set based on the thermal power dissipation capability of the system. Grace throttles power when average power exceeds this limit. Users can reduce the power limit lower than the default value that was set in the BIOS. This setting is exposed through the Hwmon nodes and can be applied to total socket power. Power capping can be applied **only** at the socket level and not at the vdd\_cpu or vdd\_soc power levels.

To set power limit, run the following command:

```

echo <power value in micro Watts> > /sys/class/hwmon/hwmonX/device/power1_cap

```

For a Grace Hopper Superchip system, the capping power of the Grace CPU allows the Hopper GPU to draw more power, which can improve performance of GPU-heavy applications.

Power capping of the GPU can be applied according to <u>GPU and Module Power Management</u>.

# 4.8. CPU Temperature Management

ACPI thermal management (Tj) uses telemetry from temperature sensors to ensure that no local hotspots exceed the operating temperature. Power capping ensures that the average power of the socket/module is at or below the thermal capacity of the system. However, this does not account for asymmetric power distribution based on workload distribution across the cores.

ACPI tables provide passive and critical temperature limits, and the thermal governor tries to throttle CPUs to maintain temperature at or below the passive temperature limits. If the temperature exceeds the critical temperature limit, a shutdown is initiated.

To read the critical and passive trip points used for ACPI software throttling:

```

cat /sys/class/thermal/thermal_zone*/trip_point_0_type

cat /sys/class/thermal/thermal_zone*/trip_point_0_temp

cat /sys/class/thermal/thermal_zone*/trip_point_1_type

cat /sys/class/thermal/thermal_zone*/trip_point_1_temp

```

To modify these values, update the ACPI table.

Caution: We recommend that you do not change the default values. If the passive trip point is lowered, throttling might occur more often, which affects the performance.

If the passive trip point is increased, the software might not always settle at the temperature, which leads to more aggressive hardware throttling, and can reduce performance.

#### **GPU Temperatures** 4.9.

For GPU temperature using nvidia-smi, to get the temperature output, run the nvidia-smi -q -d TEMPERATURE command.

This step gets the current temperature and the temperature-related limits.

# 5. Operating System Settings

This chapter provides information about the operating system settings.

# 5.1. Page Size

Grace supports 64K and 4K Linux kernel page sizes. To configure your Linux kernel with the page size that suits your business needs, change the following kconfig settings during the kernel compilation:

4K page size: CONFIG\_ARM64\_4K\_PAGES=y 64K page size: CONFIG\_ARM64\_64K\_PAGES=y

The 64K page size can benefit the applications that allocate a large amount of memory because there will be fewer page faults, better TLB hits, and efficiency.

Note: The recommended default value for the page size is 64K.

# 5.2. Huge Pages

Huge pages might be beneficial to applications that allocate large chunks of memories, and the main benefit is fewer TLB misses.

You can use huge pages on Grace systems in the following ways:

- Transparent Huge Pages (THP)

- o Transparent to the application.

- Mostly automatic with a few available kernel tuning parameters.

- When using the recommended 64 KB page size, THP pages are currently too large for practical use in most applications (refer to Transparent Huge Pages for more information).

#### Hugetlbfs

- Does not suffer from fragmentation concerns or from allocation latency because the huge pages are pre-allocated and indivisible.

- Requires application modification.

- Requires sysadmin setup.

#### Transparent Huge Pages 5.2.1.

THP is completely transparent to applications, and applications can get the benefit of huge pages without changing their source code (refer to Transparent Hugepage Support for more information). As of kernel version 6.5, only 512MB THP pages are supported when a 64KB system page size is configured. If 512MB THP is too large for your application, consider using hugetlbfs as described in Hugetlbfs.

Refer to <u>Transparent Hugepage Support</u> for more information about THP.

Note: The default huge page size is related to the kernel page size (refer to <u>HugeTLBpage</u> on ARM64 for more information).

### 5.2.2. Proactive Compaction

Proactive Compaction reduces allocation latency of huge pages by preemptively performing the work in the background. Proactive compaction does not change the probability of obtaining a huge page, but it changes how fast you can get one.

Without compaction, the kernel will return huge pages until it runs out of them. The application will then experience a perf cliff because the kernel is going to defragment the memory, and Proactive compaction smooths this out this process.

With compaction, when the applications start hitting a threshold of memory fragmentation, the kernel begins to defragment the memory pages in the background with anticipation of avoiding running out of huge pages and hitting a performance cliff.

The proactive compaction exposes a tunable, /proc/sys/vm/compaction\_proactiveness, which accepts values in the [0, 100] range, and a default value of 20. This tunable determines how aggressively the kernel should compact memory in the background and setting an aggressive value can lead to increased address translation latency. The default value of 20 is reasonable and should only be changed based on perf data.

To limit the overhead of proactive compaction, you can use the on-demand compaction method, which is available only after CONFIG\_COMPACTION is set. When 1 is written to the /proc/sys/vm/compact\_memory file, all zones are compacted, and free memory is available in contiguous blocks where possible. This can be important, for example, when allocating

huge pages, because it will also directly compact memory as required. Refer to Documentation for /proc/sys/ym/ for more information.

#### Hugetlbfs 5.2.3.

By using hugetlbfs, pools of hugetlb pages can be preallocated, and applications can use the huge pages in these pools. However, this requires changes in applications.

You can specify the minimum number of huge pages that are reserved by the system and how big the pool can grow. You can configure malloc to use hugetlbfs for an app. We strongly recommend that you test your app with hugetlbfs, and if it works with your app, use it.

The benefit of reserving a pool of huge pages at boot time is that at boot time, the memory is not fragmented, so there is a greater chance that the requested number of huge pages can be assembled...

Refer to <u>HugeTLB Pages</u> for more information.

# 5.3. Configuring Linux Perf

Refer to Configuring Perf for more information.

# 5.4. Performance Governor

You can set the CPU governor using the cpupower command. For example, to set the CPU governor to Performance, run the following command:

sudo cpupower frequency-set -g performance

Note: On certain distributions, like Ubuntu, the cpufrequtils package provides a cpufregutils service that might change the CPU governor to ondemand when the system boots. To avoid this behavior, users can disable this service by running the sudo systemctl disable cpufrequtils command.

### 5.5 Init on Alloc

The CONFIG\_INIT\_ON\_ALLOC\_DEFAULT\_ON kernel configuration option controls whether the kernel will fill newly allocated pages and heap objects with zeroes by default. You can overwrite this setting with the init\_on\_alloc=[0|1] kernel parameter.

On coherent systems, such as Grace Hopper, where GPU memory is exposed as system memory, this can cause heavy performance impacts to cudaMalloc() operations.

Note: The recommended default value on GH is the init\_on\_alloc=0 parameter.

Not all distros will set the CONFIG\_INIT\_ON\_ALLOC\_DEFAULT\_ON config on their kernels. For example, the SUSE and RHEL kernels do not currently set this option, but the Ubuntu -generic kernel does set this option.

The current value of the init\_on\_alloc kernel configuration option on a system might be printed as follows:

grep init\_on\_alloc /proc/cmdline

which should provide output like the following:

BOOT IMAGE=/boot/vmlinuz-6.2.0-1010-nvidia-64k root=UUID=7123054d-9b18-4c3d-8844-c538c751b59a ro rd.driver.blacklist=nouveau nouveau.modeset=0 earlycon module\_blacklist=nouveau acpi\_power\_meter.force\_cap\_on=y numa\_balancing=disable init\_on\_alloc=0 preempt=none

## 5.6. Input-Output Memory Management Unit Passthrough

The Input-Output Memory Management Unit (IOMMU) is a hardware component that performs address translation from I/O device virtual addresses (also called I/O virtual address (IOVA)) to physical addresses. Different platforms have different IOMMUs, such as the Intel IOMMU graphics address remapping table (GART) that is used by PCI Express graphics cards, and System Memory Management Unit (SMMU) that is used by the ARM platform.

Linux provides the iommu.passthrough mode, and you can configure the DMA to use (or not use) the IOMMU to access the memory for addressing. This release requires that SMMU passthrough NOT be enabled. Future kernel releases will change that guidance, but for now we cannot run CUDA programs with SMMU in passthrough mode.

Setting iommu.passthrough to 1 on the kernel command line bypasses the IOMMU translation for DMA and setting it to 0 uses IOMMU translation for DMA. This value needs to be set at deployment (in the kernel configuration) or by editing the appropriate grub configuration files. For the changes to take effect, you need to reboot the system.

To add kernel parameters, complete the steps for your distro:

#### Ubuntu

1. Create the /etc/default/grub.d/iommu\_passthrough.cfg file with the following contents:

```

GRUB_CMDLINE_LINUX="$GRUB_CMDLINE_LINUX iommu.passthrough=0"

```

2. Run the following commands:

```

sudo update-grub

sudo reboot

```

#### RedHat

1. Run the following commands:

```

sudo grubby --update-kernel=ALL --args="iommu.passthrough=0"

sudo reboot

```

#### **SUSE**

- 1. Edit the /etc/default/grub file.

- 2. On the line that contains the GRUB\_CMDLINE\_LINUX string, append the iommu.passthrough=0 parameter, and run the following commands:

```

sudo update-bootloader --refresh

sudo reboot

```

# 5.7. Automatic NUMA Scheduling and Balancing

When using a Grace Hopper system, we recommend that you **do not** use Automatic NUMA Scheduling and Balancing (AutoNUMA) features of the Linux kernel.

This is because of the additional page-faults that are introduced by AutoNUMA, which can significantly hurt GPU-heavy application performance.

- To see the status of AutoNUMA, use cat /proc/sys/kernel/numa\_balancing.

- If the output is 1, AutoNUMA is enabled, if it is 0, it is disabled.

- To disable AutoNUMA in a session, use echo 0 > /proc/sys/kernel/numa\_balancing.

- To disable AutoNUMA permanently, use echo "kernel.numa\_balancing = 0" >> /etc/sysctl.conf.

# 5.8. Swap File Size

This section applies **only** to Grace Hopper systems.

If an application allocates a large enough fraction of CPU memory, the kernel might decide to migrate some pages, possibly from third-party applications, from CPU memory to GPU memory. Currently, this memory can only be reclaimed through a swap file. We recommend that you have a large enough swap file for these scenarios.

Note: On a Grace Hopper system, we recommend using a swap file of at least 1/4-1/2 the aggregate GPU memory size in the system.

# 6. Optimizing IO Performance

# 6.1. Networking

We recommend that you download the latest driver and firmware for your network adapter. Before making any changes, contact your network adapter's vendor for information about whether the tuning options in this guide are applicable.

#### 6.1.1. NUMA Node

Always ensure that you use local CPU and memory that are in the same NUMA domain as your network adapter.

To check your network adapter's NUMA domain, run following commands:

cat /sys/class/net/<ethernet interface>/device/numa\_node cat /sys/class/net/<ethernet interface>/device/local\_cpulist

#### 6.1.2. **IRQ** Balance

The operating system typically distributes the interrupts among all CPU cores in a multi-processor system, but this can cause delayed interrupt processing.

To disable this on Linux, run the following command:

sudo systemctl disable irgbalance

#### 6.1.3. Configuring Interrupt Handling

A channel in a network adapter is an IRQ and a set of queues that can trigger that IRQ.. Typically, you do not want more interrupt queues than the number of cores in the system, so control the number of interrupt queues in a NUMA domain.

To set the number of channels:

**Before you begin**, stop the irgbalance service.

- 1. Check the current settings with the following command: ethtool -1 <adapter>

- 2. It tells you the current setting of various queue types.

3. Set the number of channels, for example:

```

sudo ethtool -L <adapter> combined 16 tx 0 rx 0

```

- 4. To receive and to transmit (combined), set the receive queue (rx), the transmit queue (tx), or a combined queue of both types.

- 5. Contact your vendor for information.

For NVIDIA Mellanox network adapters, to set the appropriate interrupt handling masks, invoke the following script:

```

sudo set_irq_affinity.sh <adpater>

```

This script comes with a MOFED installation.

## 6.1.4. TX/RX Queue Size

The NIC's queue size dictates how many ring buffers are allocated for DMA transfer. To help prevent package drops, we recommend that you set the size to the maximum allowed value. You can also set it to a value that works best for your use case.

To query the current setting of the queue size:

```

ethtool -g enp1s0

Ring parameters for ibp1s0:

Pre-set maximums:

8192

RX.

RX Mini:

n/a

RX Jumbo:

n/a

TX:

8192

Current hardware settings:

RX:

512

RX Mini:

n/a

RX Jumbo:

n/a

TX:

1024

```

To set the queue size of a NIC:

sudo ethtool -G <adapter> rx <value> tx <value>

# 6.1.5. Large Receive Offload

Depending on your use case, you can optimize for max throughput or best latency, but rarely both. Enabling Large Receive Offload (LRO) is a typical setting to optimize for maximum network throughput, but it might negatively affect the network latency. Contact your network adapter vendors for more information about whether LRO is supported and the best practices for usage.

To enable/disable LRO:

```

sudo ethtool lro <on|off>

```

### 6.1.6. MTU

We recommend that you set the network adapter's MTU to jumbo frame (9000) when you bring up the network interface:

```

sudo ifconfig <adapter> <IP_address> netmask <network_mask> mtu 9000 up

```