# NVIDIA BlueField-3 DPU Controller User Manual

# **Table of Contents**

| 1      | Introduction                                         | 7  |

|--------|------------------------------------------------------|----|

| 1.1    | System Requirements                                  | 7  |

| 1.2    | Package Contents                                     | 8  |

| 1.2.1  | Card Package                                         | 8  |

| 1.2.2  | Accessories Kit                                      | 8  |

| 1.2.3  | PCIe Auxiliary Card Package                          | 8  |

| 1.3    | Features and Benefits                                | 8  |

| 2      | BlueField-3 Administrator Quick Start Guide          | 13 |

| 2.1    | Prerequisites for Initial BlueField-3 Deployment     | 13 |

| 2.2    | First-time Installation Procedure                    | 13 |

| 3      | Supported Interfaces                                 | 14 |

| 3.1    | FHHL DPU Controller Layout and Interface Information | 14 |

| 3.2    | Interfaces Detailed Description                      | 15 |

| 3.2.1  | System-on-Chip (SoC)                                 | 15 |

| 3.2.2  | Networking Interface                                 | 16 |

| 3.2.3  | Networking Ports LEDs Interface                      | 16 |

| 3.2.4  | PCI Express Interface                                | 17 |

| 3.2.5  | DDR5 SDRAM On-Board Memory                           | 17 |

| 3.2.6  | NC-SI Management Interface                           | 17 |

| 3.2.7  | UART Interface Connectivity                          | 17 |

| 3.2.8  | USB 4-pin RA Connector                               | 18 |

| 3.2.9  | 1GbE 00B Management Interface                        | 18 |

| 3.2.10 | PPS IN/OUT Interface                                 | 19 |

| 3.2.11 | External PCIe Power Supply Connector                 | 19 |

| 3.2.12 | Cabline CA-II Plus Connectors                        | 20 |

| 3.2.13 | Integrated BMC Interface                             | 21 |

| 3.2.14 | NVMe SSD Interface                                   | 21 |

| 3.2.15 | RTC Battery                                          | 21 |

| 3.2.16 | eMMC Interface                                       | 21 |

| 4      | Pinouts Description                                  | 22 |

| 4.1    | PCI Express Interface                                | 22 |

| 4.2    | External Power Supply Connector                      | 24 |

| 4.3    | NC-SI Management Interface                                                   | 25   |

|--------|------------------------------------------------------------------------------|------|

| 4.4    | Cabline CA-II Plus Connectors Pinouts                                        | 27   |

| 4.4.1  | Component Side                                                               | . 27 |

| 4.4.2  | Print Side                                                                   | . 29 |

| 5      | Hardware Installation and PCIe Bifurcation                                   | . 32 |

| 5.1    | Safety Warnings                                                              | 32   |

| 5.2    | Installation Procedure Overview                                              | 33   |

| 5.3    | System Requirements                                                          | 33   |

| 5.3.1  | Hardware Requirements                                                        | . 33 |

| 5.3.2  | Airflow Requirements                                                         | . 33 |

| 5.3.3  | Software Requirements                                                        | . 34 |

| 5.4    | Safety Precautions                                                           | 34   |

| 5.5    | Unpacking                                                                    | 34   |

| 5.6    | Pre-Installation Checklist                                                   | 34   |

| 5.7    | Installation Instructions                                                    | 34   |

| 5.8    | Cables and Modules                                                           | 35   |

| 5.8.1  | Networking Cable Installation                                                | . 35 |

| 5.8.2  | 8-pin ATX Power Supply Cable                                                 | . 35 |

| 5.8.3  | Cable Installation Instructions                                              | . 36 |

| 5.9    | DPU Controller Power-Up and Power-Down Sequences                             | 37   |

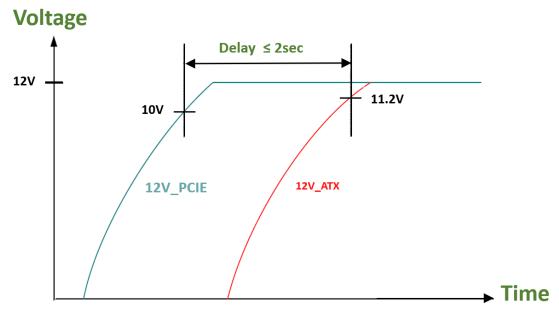

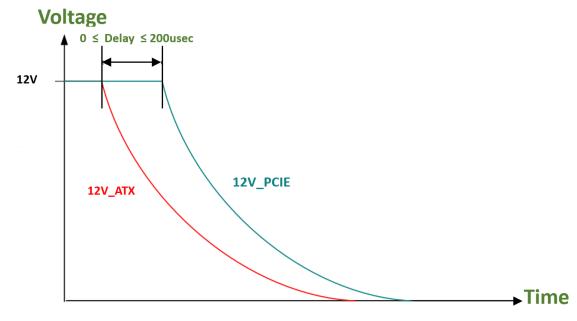

| 5.9.1  | Power-Up Sequence                                                            | . 37 |

| 5.9.2  | Power-Down Sequence                                                          | . 38 |

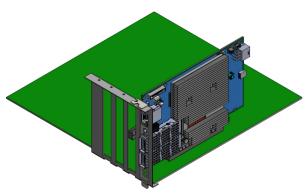

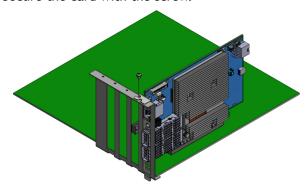

| 5.10   | PCIe x16 DPU Controller Installation Instructions                            | 39   |

| 5.10.1 | Installation Instructions                                                    | . 39 |

| 5.10.2 | Uninstalling the BlueField-3 Card                                            | . 40 |

| 5.11   | [Optional] PCIe Extension Connection (2x PCIe x16) Installation Instructions | 41   |

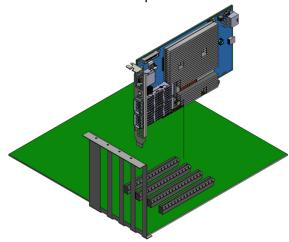

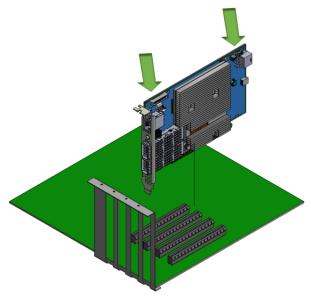

| 5.11.1 | Installing the DPU                                                           | . 42 |

| 5.11.2 | Uninstalling the Cards                                                       | . 46 |

| 5.12   | PCIe Bifurcation Configuration Options                                       | 47   |

| 5.12.1 | Bifurcated to Eight x4 PCle                                                  | . 48 |

| 5.12.2 | Bifurcated to One x16 PCle and Eight x2 PCle                                 | . 49 |

| 6      | Setting High-Speed-Port Link Type                                            | . 51 |

| 6.1    | mlxconfig                                                                    | 51   |

| 6.2    | UEFI                                                                         | 51   |

| 7      | Troubleshooting                                                   | 52 |

|--------|-------------------------------------------------------------------|----|

| 7.1    | General Troubleshooting                                           | 52 |

| 8      | Specifications                                                    | 53 |

| 8.1    | 900-9D3C6-00CV-GA0 / 900-9D3C6-00CV-DA0 Specifications            | 53 |

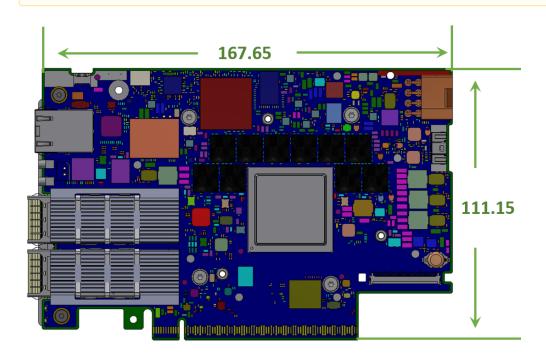

| 8.1.1  | DPU Controller Mechanical Drawing and Dimensions                  | 54 |

| 9      | Monitoring                                                        | 55 |

| 9.1    | Thermal Sensors                                                   | 55 |

| 9.2    | Heatsink                                                          | 55 |

| 10     | Finding the GUID/MAC and Serial Number on the Card                | 56 |

| 10.1   | DPU Controller Board Label Example                                | 56 |

| 11     | PCIe Auxiliary Card Kit                                           | 58 |

| 11.1   | PCIe Auxiliary Card Package Contents                              | 58 |

| 11.2   | Channel Insertion Loss                                            | 59 |

| 11.3   | Cabline CA-II Plus Harness Pinouts                                | 59 |

| 11.3.1 | Cabline CA-II Plus Harness - Component Side                       | 59 |

| 11.3.2 | Cabline CA-II Plus Harness - Print Side                           | 66 |

| 11.4   | Technical Specifications                                          | 75 |

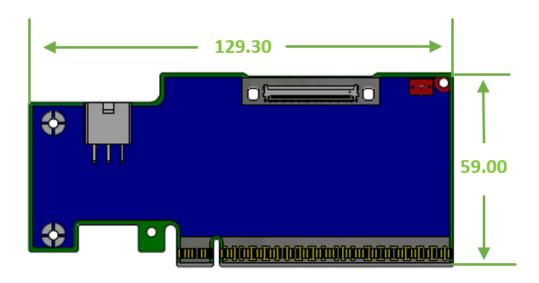

| 11.4.1 | PCIe Auxiliary Card Mechanical Drawings and Dimensions            | 76 |

| 11.4.2 | Bracket Mechanical Drawings and Dimensions                        | 76 |

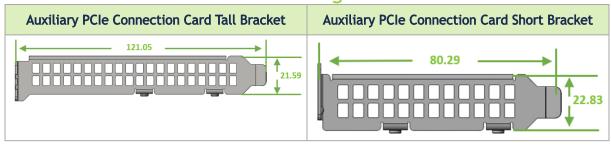

| 11.4.3 | Cabline CA-II Plus Harnesses Mechanical Drawing                   | 77 |

| 12     | Cables and Cabling Configurations                                 | 78 |

| 12.1   | RJ45 Cable for the 1GbE OOB Management Interface                  | 78 |

| 12.2   | USB Interface Cabling                                             | 78 |

| 13     | General Cooling Recommendations for Heatsink-less DPU Controllers | 79 |

| 13.1   | General Notes                                                     | 79 |

| 13.2   | Components that Require Cooling                                   | 80 |

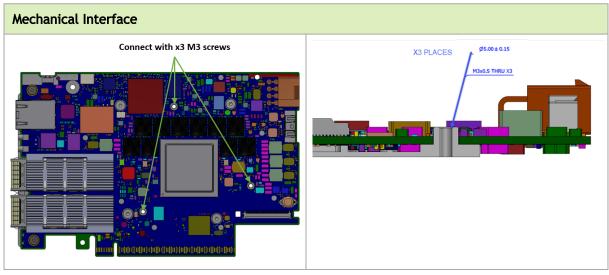

| 13.2.1 | Mechanical Interfaces                                             | 81 |

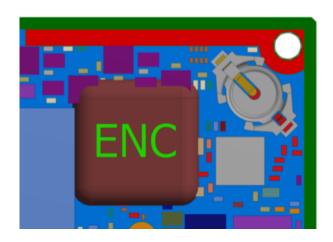

| 13.2.2 | Encapsulation and Battery on SFG                                  | 81 |

| 14     | Document Revision History                                         | 83 |

#### **About This Manual**

This User Manual describes NVIDIA® BlueField®-3 BF3220SH DPU Controller cards. It provides details as to the interfaces of the board, specifications, required software and firmware for operating the card, hardware installation, driver installation and bring-up instructions.

#### **Ordering Part Numbers**

The below table provides the ordering part numbers (OPN) for the available BlueField BF3220SH DPU Controllers.

| Model   | NVIDIA SKU             |                                                                                                                                                                                                                                                                    | Heatsink    | Lifecycle |

|---------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------|

| B3220SH | 900-9D3C6-00CV-<br>GA0 | NVIDIA BlueField-3 B3220SH E-Series No heatsink FHHL Storage Controller, 200GbE (default mode) / NDR200 IB, Dual-port QSFP112, PCIe Gen5.0 x16 with x16 PCIe extension option, 16 Arm cores, 48GB on-board DDR, integrated BMC, Crypto Enabled, Secure Boot        | No Heatsink | Prototype |

|         | 900-9D3C6-00CV-<br>DA0 | NVIDIA BlueField-3 B3220SH E-Series<br>FHHL Storage Controller, 200GbE<br>(default mode) / NDR200 IB, Dual-<br>port QSFP112, PCIe Gen5.0 x16 with<br>x16 PCIe extension option, 16 Arm<br>cores, 48GB on-board DDR, integrated<br>BMC, Crypto Enabled, Secure Boot | ~           | Prototype |

#### Intended Audience

This manual is intended for the installer and user of these cards. The manual assumes basic familiarity with InfiniBand/Ethernet network and architecture specifications.

#### Technical Support

Customers who purchased NVIDIA products directly from NVIDIA are invited to contact us through the following methods:

URL: <u>www.nvidia.com</u> → Support

E-mail: <u>enterprisesupport@nvidia.com</u>

Customers who purchased NVIDIA M-1 Global Support Services, please see your contract for details regarding Technical Support.

Customers who purchased NVIDIA products through an NVIDIA-approved reseller should first seek assistance through their reseller.

#### **Related Documentation**

#### **Related Documentation**

| InfiniBand<br>Architecture<br>Specification | InfiniBand Trade Association (IBTA) InfiniBand® specification Release 1.3.1, November 2, 2016 and Vol. 2, Release 1.4, and Vol 2 - Release 1.5. |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| IEEE Std 802.3<br>Specification             | IEEE Ethernet specification.                                                                                                                    |

| InfiniBand<br>Architecture<br>Specification | InfiniBand Trade Association (IBTA) InfiniBand® specification Release 1.3.1, November 2, 2016 and Vol. 2, Release 1.4, and Vol 2 - Release 1.5.                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCI Express<br>Specifications               | Industry Standard PCI Express Base and Card Electromechanical Specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| NVIDIA LinkX<br>Interconnect<br>Solutions   | The NVIDIA® LinkX® product family of cables and transceivers provide the industry's broadest portfolio of QDR/FDR10 (40Gb/s), FDR (56Gb/s), EDR/HDR100 (100Gb/s), HDR (200Gb/s) and NDR (400Gb/s) cables, including Direct Attach Copper cables (DACs), copper splitter cables, Active Optical Cables (AOCs) and transceivers in a wide range of lengths from 0.5m to 10km. In addition to meeting IBTA standards, NVIDIA tests every product in an end-to-end environment ensuring a Bit Error Rate of less than 1E-15. |

| BlueField DPU Platform BSP Documentation    | This guide provides product release notes as well as information on the BSP and how to develop and/or customize applications, system software, and file system images for the BlueField platform.                                                                                                                                                                                                                                                                                                                        |

| DOCA SDK Software Documentation             | NVIDIA DOCA SDK software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### **Document Conventions**

When discussing memory sizes, GB and GBytes are used in this document to mean size in giga Bytes. The use of Gb or Gbits (small b) indicates size in giga bits. In this document PCIe is used to mean PCI Express.

#### **Revision History**

A list of the changes made to this document are provided in <u>Document Revision History</u>.

# 1 Introduction

The NVIDIA® BlueField®-3 data processing unit (DPU) Controller is the 3rd-generation data center infrastructure-on-a-chip that enables organizations to build software-defined, hardware-accelerated IT infrastructures from cloud to core data center to edge. With 200Gb/s Ethernet or NDR200 200Gb/ s InfiniBand network connectivity, BlueField-3 DPU Controller offloads, accelerates, and isolates software-defined networking, storage, security, and management functions in ways that profoundly improve data center performance, efficiency, and security. Providing powerful computing, and a broad range of programmable acceleration engines in the I/O path, BlueField-3 is perfectly positioned to address the infrastructure needs of the most demanding applications, while delivering full software backward compatibility through the NVIDIA DOCA™ software framework. BlueField-3 DPU Controllers are highly optimized for NVMe storage systems, Network Functions Virtualization (NFV), Cloud and Machine Learning workloads. BlueField-3 integrates all the discrete components of a storage system appliance into a single chip making it the premier solution for building Just-a-Bunch-Of-Flash (JBOF) systems, All-Flash-Array and storage appliances for NVMe over Fabrics. With an integrated NVMe-oF and NVMe/TCP offload accelerator, the BlueField-3 DPU Controller has a superior performance advantage over existing JBOF systems, significantly reducing storage transaction latency, while increasing IOPs (I/O operations per second).

# 1.1 System Requirements

| 1.1 System Requirements |                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Motherboard             | In PCIe x16 Configuration PCIe Gen 5.0 (32GT/s) through x16 edge connector. In PCIe x16 Extension Option - Switch DSP (Data Stream Port) PCIe Gen 5.0 SERDES @32GT/s through edge connector PCIe Gen 5.0 SERDES @32GT/s through PCIe Auxiliary Connection Card                                                                           |  |  |  |

| System Power Supply     | The maximum power consumption is up to <b>150W</b> and is split between the two power sources as follows:  • Up to 66W from the PCIe golden fingers (12V)  • The rest of the consumed power is drawn from a supplementary 8-pin ATX power supply connector                                                                               |  |  |  |

|                         | NOTE: The power cable is not included in the package. It should be part of the system wiring or ordered separately as an accessory.                                                                                                                                                                                                      |  |  |  |

| Operating System        | The BlueField-3 DPU Controller is shipped with Ubuntu - a Linux commercial operating system - which includes the NVIDIA OFED stack (MLNX_OFED), and is capable of running all customer-based Linux applications seamlessly. For more information, please refer to the DOCA SDK documentation or NVIDIA BlueField-3 Software User Manual. |  |  |  |

| Connectivity            | <ul> <li>Interoperable with 1/10/25/40/50/100/200 Gb/s Ethernet switches and SDR/DDR/EDR/HDR100/HDR/NDR200 InfiniBand switches</li> <li>Passive copper cable with ESD protection</li> <li>Powered connectors for optical and active cable support</li> </ul>                                                                             |  |  |  |

# 1.2 Package Contents

Prior to unpacking your DPU Controller, it is important to make sure your server meets all the system requirements listed above for a smooth installation. Be sure to inspect each piece of equipment shipped in the packing box. If anything is missing or damaged, contact your reseller.

# 1.2.1 Card Package

| Cards       | 1x BlueField-3 DPU Controller                   |  |

|-------------|-------------------------------------------------|--|

| Accessories | 1x tall bracket (shipped assembled on the card) |  |

#### 1.2.2 Accessories Kit

This is an optional accessories kit used for debugging purposes and can be ordered separately.

| Kit OPN    | Contents                                      |

|------------|-----------------------------------------------|

| MBF35-DKIT | 4-pin USB to female USB Type-A cable          |

|            | 20-pin shrouded connector to USB Type-A cable |

# 1.2.3 PCIe Auxiliary Card Package

This is an optional kit.

The PCIe auxiliary kit can be purchased separately to operate selected DPU Controllers in a dual-socket server. For package contents, refer to PCIe Auxiliary Card Kit.

For more detailed information, refer to Specifications.

# 1.3 Features and Benefits

This section describes hardware features and capabilities. Please refer to the relevant driver and/or firmware release notes for feature availability.

| Feature                                              |                                                                                                                                                                                                                                                                                                                             |                    | Description          |                       |                                                     |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------|-----------------------|-----------------------------------------------------|

| InfiniBand Architecture Specification v1.5 compliant | The DPU Controller delivers low latency, high bandwidth, and computing efficiency for high-performance computing (HPC), artificial intelligence (AI), and hyperscale cloud data centers applications.  The DPU Controller is InfiniBand Architecture Specification v1.5 compliant.  InfiniBand Network Protocols and Rates: |                    |                      | HPC),<br>nters        |                                                     |

|                                                      | Protocol                                                                                                                                                                                                                                                                                                                    | Standard           | Rate                 | (Gb/s)                | Comm                                                |

|                                                      |                                                                                                                                                                                                                                                                                                                             |                    | 4x Port<br>(4 Lanes) | 2x Ports<br>(2 Lanes) | Cita                                                |

|                                                      | NDR/<br>NDR200                                                                                                                                                                                                                                                                                                              | IBTA Vol2<br>1.5   | 425                  | 212.5                 | PAM4<br>256b/<br>257b<br>encodin<br>g and<br>RS-FEC |

|                                                      | HDR/<br>HDR100                                                                                                                                                                                                                                                                                                              | IBTA Vol2<br>1.4   | 212.5                | 106.25                | PAM4<br>256b/<br>257b<br>encodin<br>g and<br>RS-FEC |

|                                                      | EDR                                                                                                                                                                                                                                                                                                                         | IBTA Vol2<br>1.3.1 | 103.125              | 51.5625               | NRZ<br>64b/66b<br>encodin<br>g                      |

|                                                      | FDR                                                                                                                                                                                                                                                                                                                         | IBTA Vol2<br>1.2   | 56.25                | N/A                   | NRZ<br>64b/66b<br>encodin<br>g                      |

|                                                      |                                                                                                                                                                                                                                                                                                                             |                    |                      |                       |                                                     |

| Feature                    | Desc                                                                                                                                                           | ription                                                              |  |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|

| Up to 200 Gigabit Ethernet | The DPU Controller complies with the following IEEE 802.3 standards: 200GbE / 100GbE / 50GbE / 40GbE / 25GbE / 10GbE                                           |                                                                      |  |  |

|                            | Protocol                                                                                                                                                       | MAC Rate                                                             |  |  |

|                            | IEEE802.3ck                                                                                                                                                    | 200/100 Gigabit Ethernet<br>(Include ETC enhancement)                |  |  |

|                            | IEEE802.3cd<br>IEEE802.3bs<br>IEEE802.3cm<br>IEEE802.3cn<br>IEEE802.3cu                                                                                        | 200/100 Gigabit Ethernet<br>(Include ETC enhancement)                |  |  |

|                            | IEEE 802.3bj<br>IEEE 802.3bm                                                                                                                                   | 100 Gigabit Ethernet                                                 |  |  |

|                            | IEEE 802.3by<br>Ethernet Technology<br>Consortium                                                                                                              | 25/50 Gigabit Ethernet                                               |  |  |

|                            | IEEE 802.3ba                                                                                                                                                   | 40 Gigabit Ethernet                                                  |  |  |

|                            | IEEE 802.3ae                                                                                                                                                   | 10 Gigabit Ethernet                                                  |  |  |

|                            | IEEE 802.3cb                                                                                                                                                   | 2.5/5 Gigabit Ethernet<br>(For 2.5: support only 2.5<br>x1000BASE-X) |  |  |

|                            | IEEE 802.3ap                                                                                                                                                   | Based on auto-negotiation and KR startup                             |  |  |

|                            | IEEE 802.3ad<br>IEEE 802.1AX                                                                                                                                   | Link Aggregation                                                     |  |  |

|                            | IEEE 802.1Q<br>IEEE 802.1P VLAN tags and<br>priority                                                                                                           |                                                                      |  |  |

|                            | IEEE 802.1Qau (QCN) Congestion Notification IEEE 802.1Qaz (ETS) EEE 802.1Qbb (PFC) IEEE 802.1Qbg IEEE 1588v2 IEEE 802.1AE (MACSec) Jumbo frame support (9.6KB) |                                                                      |  |  |

| Feature                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| On-board Memory                                            | <ul> <li>Quad SPI NOR FLASH - includes 256Mbit for Firmware image.</li> <li>UVPS EEPROM - includes 2Mbit.</li> <li>FRU EEPROM - Stores the parameters and personality of the card. The EEPROM capacity is 128Kbit. FRU I2C address is (0x50) and is accessible through the PCIe SMBus.</li> <li>DPU_BMC Flashes:         <ul> <li>2x 64MByte for BMC Image</li> <li>512MByte for Config Data</li> </ul> </li> <li>eMMC pSLC 40GB with 30K Write Cycles eMMC for SoC BIOS and OS.</li> <li>SSD (onboard BGA) 128GByte for user SoC OS, logs and application SW.</li> <li>DDR5 SDRAM - 48GB @5200MT/s dual-channel DDR5 SDRAM memory. Solder down on-board 128bit + 16bit ECC.</li> </ul>                                                                                                 |

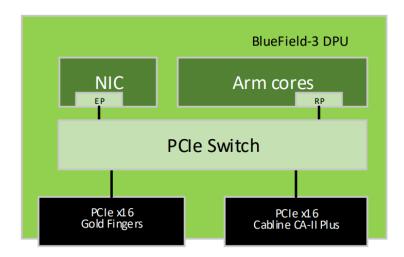

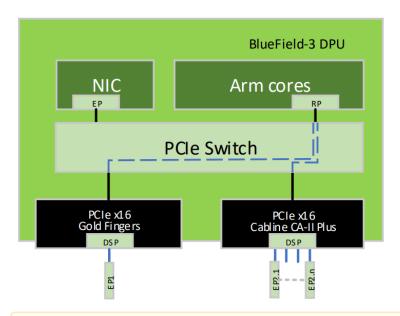

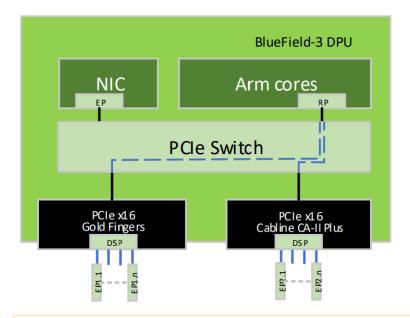

| BlueField-3 SoC                                            | The DPU Controller integrates x16 Armv8.2+ A78 Hercules cores (64-bit) is interconnected by a coherent mesh network, one DRAM controller, an RDMA intelligent network adapter supporting up to 400Gb/s, an embedded PCIe switch with endpoint and root complex functionality, and up to 32 lanes of PCIe Gen 5.0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RDMA and RDMA over Converged<br>InfiniBand/Ethernet (RoCE) | The DPU Controller, utilizing IBTA RDMA (Remote Data Memory Access) and RoCE (RDMA over Converged InfiniBand/Ethernet) technology, delivers low-latency and high-performance over InfiniBand/Ethernet networks. Leveraging data center bridging (DCB) capabilities as well as advanced congestion control hardware mechanisms, RoCE provides efficient low-latency RDMA services over Layer 2 and Layer 3 networks.                                                                                                                                                                                                                                                                                                                                                                     |

| Storage Acceleration                                       | <ul> <li>A consolidated compute and storage network achieves significant cost-performance advantages over multi-fabric networks. Standard block and file access protocols can leverage RDMA for high-performance storage access: NVMe over Fabric offloads for the target machine</li> <li>The DPU Controller may operate as a co-processor offloading specific storage tasks from the host, isolating part of the storage media from the host, or enabling abstraction of software-defined storage logic using the NVIDIA BlueField-3 Arm cores. On the storage initiator side, the DPU Controller can prove an efficient solution for hyper-converged systems to enable the host CPU to focus on compute while all the storage interface is handled through the Arm cores.</li> </ul> |

| NVMe-oF and NVMe/TCP Accelerations                         | Non-volatile Memory Express (NVMe) over Fabrics or over TCP are protocols for communicating block storage IO requests over RDMA or TCP to transfer data between a host computer and a target solid-state storage device or system over a network. The DPU Controller may operate as a co-processor offloading specific storage tasks from the host using its powerful NVMe Offload accelerator.                                                                                                                                                                                                                                                                                                                                                                                         |

| SR-IOV                                                     | The DPU Controller SR-IOV technology provides dedicated adapter resources and guaranteed isolation and protection for virtual machines (VM) within the server.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Feature                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPU Direct                 | GPUDirect RDMA is a technology that provides a direct P2P (Peerto-Peer) data path between the GPU Memory directly to/from the NVIDIA HCA devices. This provides a significant decrease in GPU-GPU communication latency and completely offloads the CPU, removing it from all GPU-GPU communications across the network. The DPU Controller uses high-speed DMA transfers to copy data between P2P devices resulting in more efficient system applications                                                                                                                                  |

| Cryptography Accelerations | From IPsec and TLS data-in-motion inline encryption to AES-XTS block-level data-at-rest encryption and public key acceleration, the DPU Controller hardware-based accelerations offload the crypto operations and free up the CPU, reducing latency and enabling scalable crypto solutions. BlueField-3 "host-unaware" solutions may transmit and receive data, while BlueField-3 acts as a bump-in-the-wire for crypto.                                                                                                                                                                    |

| Security Accelerators      | A consolidated compute and network solution based on the DPU Controller achieves significant advantages over a centralized security server solution. Standard encryption protocols and security applications can leverage NVIDIA BlueField-3 compute capabilities and network offloads for security application solutions such as Layer4 Statefull Firewall.                                                                                                                                                                                                                                |

| Out-of-Band Management     | The DPU Controller incorporates a 1GbE RJ45 out-of-band port that allows the network operator to establish trust boundaries in accessing the management function to apply it to network resources. It can also be used to ensure management connectivity (including the ability to determine the status of any network component) independent of the status of other in-band network components.                                                                                                                                                                                            |

| ВМС                        | The DPU Controller incorporate local NIC BMC (Baseboard Management Controller) hardware on the board. The BMC SoC (system on a chip) can utilize either shared or dedicated NICs for remote access. The BMC node enables remote power cycling, board environment monitoring, BlueField-3 chip temperature monitoring, board power and consumption monitoring, and individual interface resets. The BMC also supports the ability to push a bootstream to BlueField-3. Having a trusted on-board BMC that is fully isolated for the host server ensures highest security for the DPU boards. |

# 2 BlueField-3 Administrator Quick Start Guide

This page is tailored for system administrators wishing to install BlueField and perform sample administrative actions on it. For a quick start guide aimed at software developers wishing to develop applications on the BlueField card using the DOCA framework, please refer to the <u>NVIDIA DOCA Developer Quick Start Guide</u>.

Not sure which guide to follow? For more details on the different BlueField user types, please refer to the NVIDIA BlueField and DOCA User Types document.

# 2.1 Prerequisites for Initial BlueField-3 Deployment

Unable to render include or excerpt-include. Could not retrieve page.

## 2.2 First-time Installation Procedure

Unable to render include or excerpt-include. Could not retrieve page.

# 3 Supported Interfaces

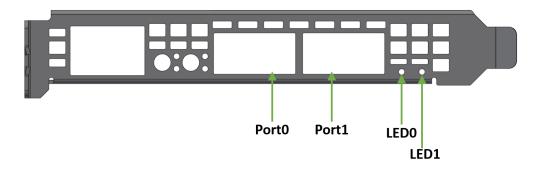

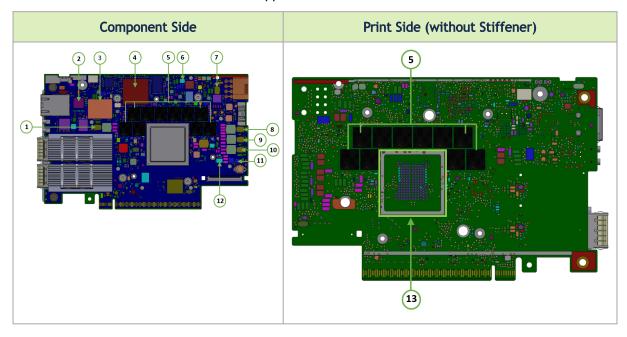

This section describes the DPU Controller supported interfaces. Each numbered interface referenced in the figures is described in the following table with a link to detailed information.

The below figures are for illustration purposes only and might not reflect the current revision of the DPU Controller.

# 3.1 FHHL DPU Controller Layout and Interface Information

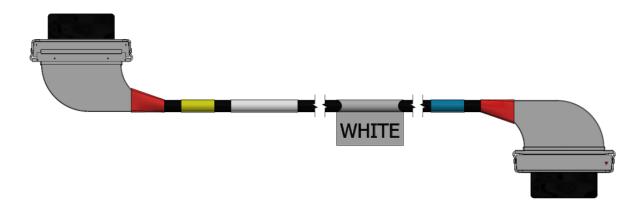

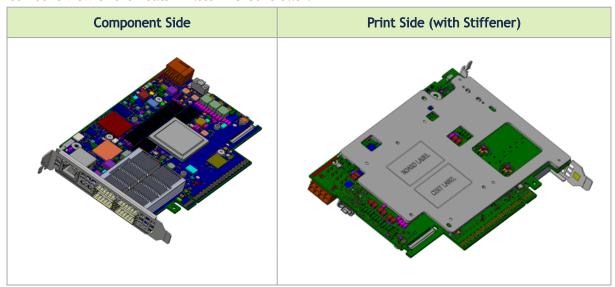

| OPN                                      | DPU Controller Component Side | DPU Controller Print Side |

|------------------------------------------|-------------------------------|---------------------------|

| 900-9D3C6-00CV-GA0<br>900-9D3C6-00CV-DA0 |                               |                           |

| Ite<br>m | Interface                             | Description                                                                                                                                                                            |

|----------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | System-on-<br>Chip (SoC)              | 16 Arm-Cores SoC                                                                                                                                                                       |

| 2        | Networking<br>Interface               | The network traffic is transmitted through the DPU Controller QSFP112 connectors. The QSFP112 connectors allow the use of modules and optical and passive cable interconnect solutions |

| 3        | Networking<br>Ports LEDs<br>Interface | One bi-color I/O LEDs <b>per port</b> to indicate link and physical status                                                                                                             |

| 4        | PCI Express<br>Interface              | PCIe Gen 5.0 through an x16 edge connector                                                                                                                                             |

| 5        | DDR5 SDRAM<br>On-Board<br>Memory      | 20 units of DDR5 SDRAM for a total of 48GB @ 5200MT/s. 128bit + 16bit ECC, solder-down memory                                                                                          |

| 6        | NC-SI<br>Management<br>Interface      | NC-SI 20 pins BMC connectivity for remote management                                                                                                                                   |

| 7        | USB 4-pin RA<br>Connector             | Used for OS image loading                                                                                                                                                              |

| 8        | 1GbE OOB<br>Management<br>Interface   | 1GbE BASE-T OOB management interface                                                                                                                                                   |

| Ite<br>m | Interface                                  | Description                                                                                                    |

|----------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 9        | MMCX RA PPS<br>IN/OUT                      | Allows PPS IN/OUT                                                                                              |

| 10       | External PCIe<br>Power Supply<br>Connector | An external 12V power connection through an 8-pin ATX connector                                                |

| 11       | Cabline CA-II Plus Connectors              | Two Cabline CA-II plus connectors are populated to allow connectivity to an additional PCIe x16 Auxiliary card |

| 12       | Integrated<br>BMC                          | DPU BMC                                                                                                        |

| 13       | SSD Interface                              | 128GB                                                                                                          |

| 14       | RTC Battery                                | Battery holder for RTC                                                                                         |

| 15       | <u>eMMC</u>                                | x8 NAND flash                                                                                                  |

# 3.2 Interfaces Detailed Description

# 3.2.1 System-on-Chip (SoC)

NVIDIA BlueField-3 DPU Controller is a family of advanced DPU Controller IC solutions that integrate a coherent mesh of 64-bit Armv8.2+ A78 Hercules cores, an NVIDIA® ConnectX®-7 network adapter front-end, and a PCI Express switch into a single chip. The powerful DPU Controller IC architecture includes an Armv multicore processor array, enabling customers to develop sophisticated applications and highly differentiated feature sets. Leverages the rich Arm software ecosystem and introduces the ability to offload the x86 software stack.

At the heart of BlueField-3, the ConnectX-7 network offload controller with RDMA and RDMA over Converged Ethernet (RoCE) technology delivers cutting-edge performance for networking and storage applications such as NVMe over Fabrics. Advanced features include an embedded virtual switch with programmable access lists (ACLs), transport offloads, and stateless encaps/decaps of NVGRE, VXLAN, and MPLS overlay protocols.

# 3.2.1.1 Encryption

DPU Controller addresses the concerns of modern data centers by combining hardware encryption accelerators with embedded software and fully integrated advanced network capabilities, making it an ideal platform for developing proprietary security applications. It enables a distributed security architecture by isolating and protecting each workload and providing flexible control and visibility at the server and workload level; controlling risk at the server access layer builds security into the DNA of the data center and enables prevention, detection, and response to potential threats in real-time. DPU Controller can deliver powerful functionality, including encryption of data-in-motion, bare-metal provisioning, stateful L4 firewall, and more.

# 3.2.2 Networking Interface

The DPU Controller includes special circuits to protect the card/server from ESD shocks when plugging copper cables.

The network ports are compliant with the InfiniBand Architecture Specification, Release 1.5. InfiniBand traffic is transmitted through the cards' QSFP112 connectors.

# 3.2.3 Networking Ports LEDs Interface

One bicolor (Yellow and Green) I/O LED per port indicates speed and link status.

#### Link Indications

| State                                        | Bi-              | Color LED (Yellow                                     | /Green)                        |   |

|----------------------------------------------|------------------|-------------------------------------------------------|--------------------------------|---|

| Beacon command for locating the adapter card | 1Hz blinking     | 1Hz blinking Yellow                                   |                                |   |

| Error                                        |                  | Yellow Indicates ar                                   |                                | 渫 |

|                                              | Error<br>Type    | Description                                           | LED<br>Behavior                |   |

|                                              | I <sup>2</sup> C | I <sup>2</sup> C access to the networking ports fails | Blinks until<br>error is fixed |   |

|                                              | Over-<br>current | Over-current condition of the networking ports        | Blinks until<br>error is fixed |   |

| Physical Activity                            | Blinking Gre     | Blinking Green                                        |                                |   |

| Link Up                                      | Solid Green      | Solid Green                                           |                                |   |

| Physical Up (InfiniBand Mode Only)           | Solid Yellow     | Solid Yellow                                          |                                |   |

# 3.2.4 PCI Express Interface

The DPU Controller supports PCI Express Gen 5.0/4.0 through x16 edge connectors. Some cards allow connectivity to an additional PCIe x16 Auxiliary card through the Cabline CA-II Plus connectors.

The following lists PCIe interface features:

- PCle Gen 5.0, 4.0, 3.0, 2.0 and 1.1 compatible

- 2.5, 5.0, or 8.0, 16.0 or 32.0 GT/s link rate x16 lanes

- Auto-negotiates to x16, x8, x4, x2, or x1

## 3.2.5 DDR5 SDRAM On-Board Memory

The DPU Controllers incorporate 20 units of DDR5 SDRAM for a total of 48GB @ 5200MT/s single or dual channels. 64/128bit + 8bit ECC per channel, solder-down memory.

# 3.2.6 NC-SI Management Interface

The DPU Controller enables the connection of a Baseboard Management Controller (BMC) to a set of Network Interface Controller (NICs) to enable out-of-band remote manageability. The NC-SI management is supported over RMII and has a connector on the DPU Controller. Please refer to NC-SI Management Interface for pins.

The maximum trace length on the board is 5.7inch.

The USB to UART cable is not used for NC-SI management purposes.

# 3.2.7 UART Interface Connectivity

The UART debug interface on BlueField-3 boards can be accessed through a 20-pin NC-SI connector, which is associated with the NIC BMC device. The connectivity is shown in the following table:

| NC-SI Conne | ctor Pin # | Signal on Board |

|-------------|------------|-----------------|

| 12          |            | GND             |

| 14          |            | UART_TX         |

| 16          |            | UART_RX         |

It is prohibited to connect any RS-232 cable directly! Only TTL 3.3V voltage level cables are supported.

Do not use the USB-to-UART cable for NC-SI management purposes.

# 3.2.8 USB 4-pin RA Connector

The USB 4-pin RA USB connector is used to load operating system images. Use a 4-pin male connector to a male Type-A cable to connect to the board.

It is prohibited to connect male-to-male to host, it is only used for a disk on key.

The male connector to the male Type-A cable is not included in the shipped DPU Controller card box and should be ordered separately as part of the accessories kit (P/N: MBF35-DKIT).

# 3.2.9 1GbE OOB Management Interface

The DPU Controller incorporates a 1GbE RJ45 out-of-band port that allows the network operator to establish trust boundaries in accessing the management function to apply it to network resources. It can also be used to ensure management connectivity (including the ability to determine the status of any network component) independent of other in-band network components' status.

For DPU Controllers with integrated BMC: 1GbE OOB Management can be performed via the integrated BMC.

# 3.2.9.1 1GbE OOB Management LEDs Interface

Two OOB management LEDs, one Green and one Yellow, behave as described in the table below.

| Green LED | Yellow LED | Link/Activity                  |

|-----------|------------|--------------------------------|

| OFF       | OFF        | Link off                       |

| ON        | OFF        | 1 Gb/s link / No activity      |

| Blinking  | OFF        | 1 Gb/s link / Activity (RX,TX) |

| OFF       | ON         | Not supported                  |

| OFF       | Blinking   |                                |

| ON        | ON         |                                |

| Blinking  | Blinking   |                                |

#### 3.2.10 PPS IN/OUT Interface

The DPU Controller incorporates an integrated Hardware Clock (PHC) that allows the DPU Controller to achieve sub-20u Sec accuracy and also offers many timing-related functions such as time-triggered scheduling or time-based SND accelerations (time-based ASAP<sup>2</sup>). Furthermore, 5T technology enables the software application to transmit fronthaul (ORAN) at high bandwidth. The PTP part supports the subordinate clock, master clock, and boundary clock.

The DPU Controller PTP solution allows you to run any PTP stack on your host.

With respect to testing and measurements, selected NVIDIA DPU Controllers allow you to use the PPS-out signal from the onboard MMCX RA connecter. The DPU Controller also allows measuring PTP in scale with the PPS-In signal. The PTP HW clock on the Network adapter is sampled on each PPS-In signal, and the timestamp is sent to the SW.

# 3.2.11 External PCIe Power Supply Connector

The external ATX power cable is not supplied with the DPU Controller package; however, this is a standard cable usually available in servers.

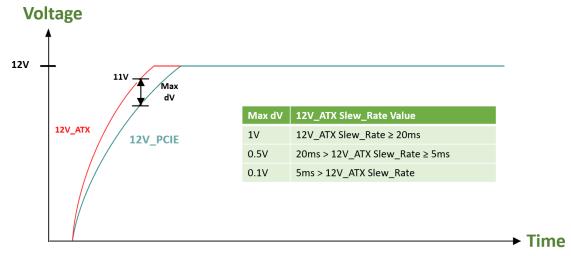

To power up the above-mentioned DPUs, it is necessary to use a supplementary 8-pin ATX power cable. Since the power provided by the PCIe golden fingers is limited to 66W, a total maximum of up to 150W is enabled through the ATX 8-pin connector and the PCIe x16 golden fingers.

The maximum power consumption which does not exceed 150W, is in accordance with the mode of operation of the DPU, and is split between the two power sources as follows:

- Up to 66W from the PCIe golden fingers (12V)

- The rest of the consumed power is drawn from the external PCIe power supply connector

Important Notes and Warnings

- The BlueField-3 DPU requires a standard PCIe ATX power connection. However, certain servers may require a custom setup to enable ATX power compatibility.

- · Consult the manufacturer's manuals and specifications to ensure proper connectivity.

- Before connecting the ATX power cable, make sure you are using a PCIe-compliant 8-pin ATX cable from the server power supply kit.

- Do not link the CPU power cable to the BlueField-3 DPU PCIe ATX power connector, as their

pin configurations differ. Using the CPU power cable in this manner is strictly prohibited and

can potentially damage the BlueField-3 DPU. Please refer to <a href="External PCIe Power Supply Connector Pins">External PCIe Power Supply Connector Pins</a> for the external PCIe power supply pins.

- Avoid using non-standard cables that do not comply with the DPU, unnecessary adapter cables, or storing the cables near heat sources.

- It is preferable that the x16 PCIe golden fingers and the PCI ATX power supply draw from the same power source. For more information on how to power up the card, refer to <u>DPU Power-Up Instructions</u>.

- The PCIe ATX 8-pin connector is not compatible with an EPS12V power cable source. Ensure that the appropriate PCIe auxiliary power source is available, not an EPS12V power source.

- If you are uncertain about your server's compatibility with the PCI ATX connection, please contact your NVIDIA representative for assistance.

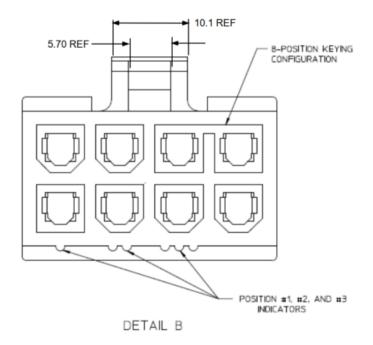

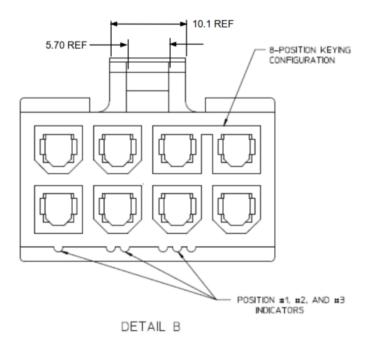

Mechanical Keys of the 8-pin ATX Power Cable (PCIe CEM Specification Rev 5.0)

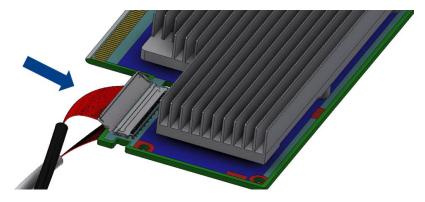

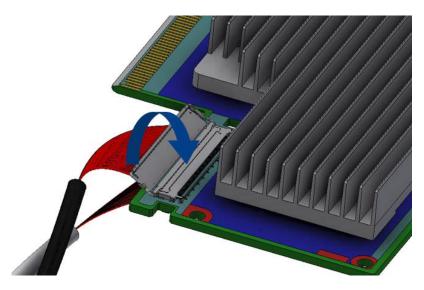

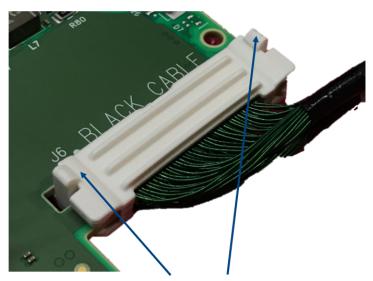

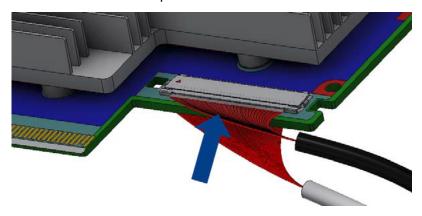

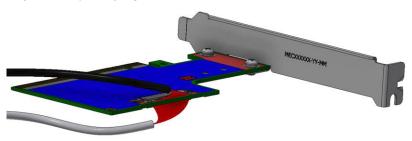

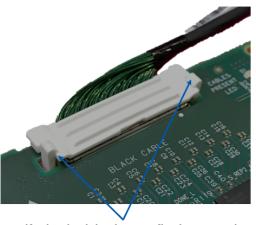

#### 3.2.12 Cabline CA-II Plus Connectors

The Cabline CA-II connectors on the DPU Controller enable connectivity to an additional PCIe x16 bus in addition to the PCIe x16 bus available through the golden-fingers. The Cabline CA-II Plus connectors allow connectivity to flash cards and NVMe SSD drives.

Specific applications have an interest in direct connectivity to the far end of the Cabline CA-II cables, through the two 60-pin Cabline CA-II connectors, directly to the motherboard, in order to cut the insertion loss and/or the additional space associated with a PCIe x16 Flash Auxiliary Board.

The Cabline CA-II connectors mate with two 60-pin Cabline CA-II cables that can be distinguished by their black or white external insulators and connector pinouts. The black Cabline CA-II cable mates with the DPU Controller's component (top) side, whereas the white Cabline CA-II cable mates with the DPU Controller print (bottom) side. The Cabline CA-II cables are offered in three standard lengths; 150mm and 350mm. For connector pinouts, please refer to <u>Cabline CA-II Plus Connectors</u> Pinouts.

# 3.2.13 Integrated BMC Interface

The DPU Controller incorporates an onboard integrated NIC BMC and an Ethernet switch. The BMC becomes available once the host server powers up the card. The NIC BMC can control the DPU Controller's power and enables DPU Controller shutdown and power-up.

#### 3.2.14 NVMe SSD Interface

The Self Encrypting Disk (SED) capability is not supported.

The on-board 128GB NVMe SSD is utilized for the storage of user applications and logs. It is important to note that all SSD devices come with a limitation on the total number of write operations they can handle throughout their lifespan. This limit is influenced significantly by the software use case and specific parameters like block size and the pattern of data access (whether it is sequential or random).

It is the customer's responsibility to oversee the rate at which the SSD ages during both the validation of the code and its usage in the field, ensuring that it aligns with the intended use case.

# 3.2.15 RTC Battery

BlueField-3 incorporates a coin type Lithium battery CR621 for RTC (Real Time Clock).

#### 3.2.16 eMMC Interface

The eMMC is an x8 NAND flash used for Arm boot and operating system storage. Memory size is 128GB, where it is effectively pSLC 40GB.

# 4 Pinouts Description

# 4.1 PCI Express Interface

The below tables lists the PCI Express pins description. For further details, please refer to  $\underline{PCI}$  Express Interface.

#### DPU PCI Express x16 Pin Description

| Pin<br># | Signal<br>Name | Description                                                            | Pin<br># | Signal<br>Name | Description                                                        |

|----------|----------------|------------------------------------------------------------------------|----------|----------------|--------------------------------------------------------------------|

| A1       | PRSNT1#        | Mechanical Present                                                     | B1       | 12V            |                                                                    |

| A2       | 12V            |                                                                        | B2       | 12V            |                                                                    |

| A3       | 12V            |                                                                        | В3       | 12V            |                                                                    |

| A4       | GND            |                                                                        | B4       | GND            |                                                                    |

| A5       | TCK            | JTAG - Not Connected                                                   | B5       | SMCLK          | Host SMBus                                                         |

| A6       | TDI            | JTAG - Not Connected                                                   | В6       | SMDAT          | Host SMBus                                                         |

| Α7       | TDO            | JTAG - Not Connected                                                   | В7       | GND            |                                                                    |

| A8       | TMS            | JTAG - Not Connected                                                   | B8       | 3.3V           | 3.3V - (Connected in 900-9D3B4-00CC-EA0 & 900-9D3B4-00SC-EA0 only) |

| A9       | 3.3V           | 3.3V - (Connected in 900-9D3B4-00CC-<br>EA0 & 900-9D3B4-00SC-EA0 only) | В9       | TRST#          | JTAG - Not Connected                                               |

| A10      | 3.3V           | 3.3V - (Connected in 900-9D3B4-00CC-<br>EA0 & 900-9D3B4-00SC-EA0 only) | B10      | 3.3V_AUX       |                                                                    |

| A11      | PERST#         | PCIe Reset                                                             | B11      | WAKW#/RSVD     |                                                                    |

| A12      | GND            |                                                                        | B12      | SER_DI         |                                                                    |

| A13      | REFCLK+        | Host Reference Clock                                                   | B13      | GND            |                                                                    |

| A14      | REFCLK-        | Host Reference Clock                                                   | B14      | PETP0          |                                                                    |

| A15      | GND            |                                                                        | B15      | PETN0          |                                                                    |

| A16      | PERP0          |                                                                        | B16      | GND            |                                                                    |

| A17      | PERN0          |                                                                        | B17      | RSVD           |                                                                    |

| A18      | GND            |                                                                        | B18      | GND            |                                                                    |

| A19      | SER_DO         |                                                                        | B19      | PETP1          |                                                                    |

| A20      | GND            |                                                                        | B20      | PETN1          |                                                                    |

| A21      | PERP1          |                                                                        | B21      | GND            |                                                                    |

| A22      | PERN1          |                                                                        | B22      | GND            |                                                                    |

| A23      | GND            |                                                                        | B23      | PETP2          |                                                                    |

| A24      | GND            |                                                                        | B24      | PETN2          |                                                                    |

| A25      | PERP2          |                                                                        | B25      | GND            |                                                                    |

| Pin<br># | Signal<br>Name  | Description | Pin<br># | Signal<br>Name | Description |

|----------|-----------------|-------------|----------|----------------|-------------|

| A26      | PERN2           |             | B26      | GND            |             |

| A27      | GND             |             | B27      | PETP3          |             |

| A28      | GND             |             | B28      | PETN3          |             |

| A29      | PERP3           |             | B29      | GND            |             |

| A30      | PERN3           |             | B30      | RSVD           |             |

| A31      | GND             |             | B31      | RSVD           |             |

| A32      | SER_CLK         |             | B32      | GND            |             |

| A33      | SER_CAPTUR<br>E |             | B33      | PETP4          |             |

| A34      | GND             |             | B34      | PETN4          |             |

| A35      | PERP4           |             | B35      | GND            |             |

| A36      | PERN4           |             | B36      | GND            |             |

| A37      | GND             |             | B37      | PETP5          |             |

| A38      | GND             |             | B38      | PETN5          |             |

| A39      | PERP5           |             | B39      | GND            |             |

| A40      | PERN5           |             | B40      | GND            |             |

| A41      | GND             |             | B41      | PETP6          |             |

| A42      | GND             |             | B42      | PETN6          |             |

| A43      | PERP6           |             | B43      | GND            |             |

| A44      | PERN6           |             | B44      | GND            |             |

| A45      | GND             |             | B45      | PETP7          |             |

| A46      | GND             |             | B46      | PETN7          |             |

| A47      | PERP7           |             | B47      | GND            |             |

| A48      | PERN7           |             | B48      | RSVD           |             |

| A49      | GND             |             | B49      | GND            |             |

| A50      | RSVD            |             | B50      | PETP8          |             |

| A51      | GND             |             | B51      | PETN8          |             |

| A52      | PERP8           |             | B52      | GND            |             |

| A53      | PERN8           |             | B53      | GND            |             |

| A54      | GND             |             | B54      | PETP9          |             |

| A55      | GND             |             | B55      | PETN9          |             |

| A56      | PERP9           |             | B56      | GND            |             |

| A57      | PERN9           |             | B57      | GND            |             |

| A58      | GND             |             | B58      | PETP10         |             |

| A59      | GND             |             | B59      | PETN10         |             |

| A60      | PERP10          |             | B60      | GND            |             |

| Pin<br># | Signal<br>Name | Description | Pin<br># | Signal<br>Name | Description        |

|----------|----------------|-------------|----------|----------------|--------------------|

| A61      | PERN10         |             | B61      | GND            |                    |

| A62      | GND            |             | B62      | PETP11         |                    |

| A63      | GND            |             | B63      | PETN11         |                    |

| A64      | PERP11         |             | B64      | GND            |                    |

| A65      | PERN11         |             | B65      | GND            |                    |

| A66      | GND            |             | B66      | PETP12         |                    |

| A67      | GND            |             | B67      | PETN12         |                    |

| A68      | PERP12         |             | B68      | GND            |                    |

| A69      | PERN12         |             | B69      | GND            |                    |

| A70      | GND            |             | B70      | PETP13         |                    |

| A71      | GND            |             | B71      | PETN13         |                    |

| A72      | PERP13         |             | B72      | GND            |                    |

| A73      | PERN13         |             | B73      | GND            |                    |

| A74      | GND            |             | B74      | PETP14         |                    |

| A75      | GND            |             | B75      | PETN14         |                    |

| A76      | PERP14         |             | B76      | GND            |                    |

| A77      | PERN14         |             | B77      | GND            |                    |

| A78      | GND            |             | B78      | PETP15         |                    |

| A79      | GND            |             | B79      | PETN15         |                    |

| A80      | PERP15         |             | B80      | GND            |                    |

| A81      | PERN15         |             | B81      | PRSNT2#        | Mechanical Present |

| A82      | GND            |             | B82      | GND            |                    |

# 4.2 External Power Supply Connector

The below table provides the External Power Supply pins of the external power supply interfaces on the DPU. For further details, please refer to <a href="External PCIe Power Supply Connector">External PCIe Power Supply Connector</a>.

The mechanical pinout of the 8-pin external +12V power connector is shown below. The +12V connector is a GPU power PCIe standard connector. Care should be taken to ensure the power is applied to the correct pins as some 8-pin ATX-type connectors can have different pinouts.

|   | Pin Number | Description |

|---|------------|-------------|

| 1 |            | 12V         |

| 2 |            | 12V         |

| 3 |            | 12V         |

| Pin Number | Description |

|------------|-------------|

| 4          | Sense1      |

| 5          | GND         |

| 6          | Sense0      |

| 7          | GND         |

| 8          | GND         |

# 4.3 NC-SI Management Interface

The below tables list the NC-SI management interface pinout descriptions. For further details, please refer to NC-SI Management Interface.

| Pin | Signal          | 1/0                                 | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|-----------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| #   | Name            |                                     | , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1   | GND             | GND                                 | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2   | PKG_ID1         | Input (to<br>BlueField-<br>3)       | NC-SI PKG_ID Shoul be connected to the Primary controller NC-SI PKG_ID pins to set the appropriate package ID. PKG_ID0 should be connected to the endpoint device GPIO associated with Package ID[0]. PKG_ID1 should be associated with Package ID[1]. Baseboard should connect to GND or leave floating. DPU should have a 4.7k PU.                                                                                                                                                                                                   |

| 3   | RBT_RXD0        | Output<br>(from<br>BlueField-<br>3) | Receive data. Data signals from the network controller to the BMC. For baseboards, this pin should be connected between the baseboard NC-SI over RBT PHY and the connector. This signal requires a 100 k $\Omega$ pull down resistor to GND on the baseboard between the BMC and the RBT isolator to prevent the signal from floating when no card is installed. For DPUs, this pin should be connected between the connector and the RBT PHY. External termination determined by the DPU RBT PHY requirements.                        |

| 4   | RBT_REF_C<br>LK | Input                               | RBT Reference clock. Synchronous clock reference for receive, transmit and control interface. The clock should have a typical frequency of 50MHz ±50 ppm.  For baseboards, this pin should be connected between the baseboard NC-SI over RBT PHY and the DPU cable connector. The RBT_REF_CLK should not be driven until 3.3V AUX is present on the DPU. The RBT_REF_CLK should be continuous once it has started.  For DPUs, this pin should be connected between the connector and the RBT PHY. No external termination is required. |

| 5   | RBT_RXD1        | Output                              | Receive data. Data signals from the network controller to the BMC. For baseboards, this pin should be connected between the baseboard NC-SI over RBT PHY and the connector. This signal requires a 100 k $\Omega$ pull down resistor to GND on the baseboard between the BMC and the RBT isolator to prevent the signal from floating when no card is installed. For DPUs, this pin should be connected between the connector and the RBT PHY. External termination determined by the DPU RBT PHY requirements.                        |

| 6   | GND             | GND                                 | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Pin<br># | Signal<br>Name    | 1/0    | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|-------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|