# Orin PVA VPU Programmer's Guide

Programmer Reference

# Review Status

|                    |                                  |

|--------------------|----------------------------------|

| <b>Title</b>       | Orin PVA VPU Programmers Guide-P |

| <b>Author</b>      | chingh                           |

| <b>Revision</b>    | May 29, 2025                     |

| <b>Reviewers</b>   | jsankaran, nshigihalli           |

| <b>Status</b>      | Completed                        |

| <b>Reviewed in</b> | NVIDIA CR #23918                 |

## Document History

SWE-PVA-076-PGRF

| <b>Version</b> | <b>Date</b>  | <b>Authors</b> | <b>Description of Change</b>                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------|--------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.5.1          | May 15, 2025 | chingh         | <ul style="list-style-type: none"><li>&gt; Branched from Orin_PVA_VPU_Programmings_Guide.docx into Orin_PVA_VPU_Programmers_Guide_pub.docx.</li><li>&gt; Restarted version number from 0.5.1, removed Proprietary/NDA tagging and cleaned up documentation control section.</li><li>&gt; Revised interpolated lookup example code to use PVA SDK Sampler API functions, in 8.5.4.</li></ul>                                                                               |

| 0.5.2          | May 22, 2025 | chingh         | <ul style="list-style-type: none"><li>&gt; Cindy Wilkinson imported into new template</li><li>&gt; Fixed footer and fixed some English mistakes in Chapters 1 through 4</li><li>&gt; Refined description of partitioning a task into sub-tasks for concurrent prefetch and execution, in 4.1.2</li><li>&gt; Removed reference to VPU config DMA feature for instruction cache invalidation for an address range, since it's not supported by PVA SDK, in 4.1.3.</li></ul> |

| 0.5.3          | May 22, 2025 | chingh         | <ul style="list-style-type: none"><li>&gt; Revised DLUT programming example to one included in Thor PVA VPU Programmer's Guide, since the Thor version has gone through review involving PVA SW team members, in 8.5.4.</li></ul>                                                                                                                                                                                                                                         |

| 0.5.4          | May 23, 2025 | chingh         | <ul style="list-style-type: none"><li>&gt; Propagated applicable revisions suggested from Thor PVA VPU Programmer's Guide review (#15825) to the Orin version, various sections.</li></ul>                                                                                                                                                                                                                                                                                |

| 0.5.5          | May 28, 2025 | chingh         | <ul style="list-style-type: none"><li>&gt; Added review table</li><li>&gt; Per CR comments, remove references to PVA User's Guide, in 2, 2.2</li><li>&gt; Per CR comments, fixed VPS block diagram, in 2.3</li><li>&gt; Per CR comments, removed references to shallow pipeline &amp; IA models, in 2.4</li></ul>                                                                                                                                                         |

| <b>Version</b> | <b>Date</b>  | <b>Authors</b> | <b>Description of Change</b>                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------|--------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |              |                | <ul style="list-style-type: none"> <li>&gt; Per CR comments, elaborated Superbanks A/B/C, in 5.3</li> <li>&gt; Fixed code indentation issues, in chapter 8 sections.</li> <li>&gt; Fixed instruction report white spaces so that execution count and cycle count numbers line up vertically, in chapter 8 sections.</li> <li>&gt; Per CR comments, fixed instruction detail table indentation and width, in chapter 9 sections</li> </ul> |

| 0.5.6          | May 28, 2025 | chingh         | <ul style="list-style-type: none"> <li>&gt; Fixed typos and issues identified from Thor version review, various sections</li> </ul>                                                                                                                                                                                                                                                                                                       |

| 1.0            | May 29, 2025 | chingh         | <ul style="list-style-type: none"> <li>&gt; CR completed, administrative update to fill review status as Completed</li> </ul>                                                                                                                                                                                                                                                                                                             |

# Table of Contents

|                                                                   |    |

|-------------------------------------------------------------------|----|

| Chapter 1. Introduction.....                                      | 12 |

| 1.1 Document Scope .....                                          | 12 |

| 1.2 References.....                                               | 12 |

| 1.2.1 Related External Documents.....                             | 12 |

| 1.2.2 Related NVIDIA-Internal Documents.....                      | 12 |

| 1.3 Glossary and Acronyms .....                                   | 12 |

| Chapter 2. Architecture Overview.....                             | 14 |

| 2.1 PVA.....                                                      | 14 |

| 2.2 DMA.....                                                      | 14 |

| 2.3 VPS.....                                                      | 15 |

| 2.4 VPU Processor Models and Differences.....                     | 16 |

| Chapter 3. VPU Core.....                                          | 18 |

| 3.1 Block Diagram.....                                            | 18 |

| 3.2 Processor Front End .....                                     | 19 |

| 3.3 Register Files.....                                           | 19 |

| 3.4 Scalar Unit .....                                             | 20 |

| 3.5 Vector Unit.....                                              | 21 |

| 3.6 Load/Store Unit.....                                          | 21 |

| Chapter 4. VPU Instruction Cache (I-Cache).....                   | 22 |

| 4.1 Overview.....                                                 | 22 |

| 4.2 Functionality.....                                            | 22 |

| 4.2.1 Preemption .....                                            | 23 |

| 4.2.2 Prefetch .....                                              | 23 |

| 4.2.3 Invalidation.....                                           | 24 |

| 4.2.4 ECC (Single-Bit-Error-Correct Double-Bit-Error-Detect)..... | 24 |

| Chapter 5. VPU Vector Memory (VMEM).....                          | 26 |

| 5.1 Overview.....                                                 | 26 |

| 5.2 VMEM Interface (VMEM I/F).....                                | 27 |

| 5.3 VMEM Superbanks .....                                         | 29 |

| 5.4 Memory Banking and Read/Write Access Patterns .....           | 30 |

| 5.5 Load Data Cache.....                                          | 32 |

| 5.6 Memory Allocation among VMEM Superbanks.....                  | 33 |

| Chapter 6. VPU Instruction Set Architecture.....                  | 34 |

| 6.1 Processor Architecture.....                                   | 34 |

| 6.1.1 Key Features .....                                          | 34 |

| 6.1.2 Program and Data Memory Spaces.....                         | 35 |

|            |                                                               |     |

|------------|---------------------------------------------------------------|-----|

| 6.1.3      | Architecture Registers.....                                   | 36  |

| 6.1.4      | Control Instructions.....                                     | 40  |

| 6.1.5      | C Function Calling Convention.....                            | 42  |

| 6.1.6      | Processor Execution States.....                               | 42  |

| 6.2        | Overview of Scalar/Vector Math Instructions .....             | 44  |

| 6.2.1      | Scalar Integer Math Instructions.....                         | 45  |

| 6.2.2      | Scalar Predicate Instructions.....                            | 45  |

| 6.2.3      | Vector Math Instruction General Rules.....                    | 45  |

| 6.2.4      | Scalar/Vector Floating-Point Math Instructions .....          | 53  |

| 6.3        | Memory Operations.....                                        | 59  |

| 6.3.1      | Memory Coherency .....                                        | 59  |

| 6.3.2      | Memory Address Alignment .....                                | 60  |

| 6.3.3      | Memory Address Range Constraints .....                        | 61  |

| 6.3.4      | Scalar Data Types .....                                       | 62  |

| 6.3.5      | Vector Data Types and Promotion/Demotion .....                | 62  |

| 6.3.6      | Vector Load/Store Distribution Options.....                   | 64  |

| 6.3.7      | Transposing Load/Store .....                                  | 66  |

| 6.3.8      | Parallel Lookup, Histogram and Vector-Addressed Store .....   | 71  |

| 6.4        | Address Generator Features .....                              | 77  |

| 6.4.1      | Multi-Dimensional Address Calculation .....                   | 78  |

| 6.4.2      | Automatic Predication .....                                   | 80  |

| 6.4.3      | Rounding and Saturation .....                                 | 81  |

| 6.4.4      | Min and Max Value Collection .....                            | 83  |

| 6.4.5      | Save and Restore to/from Memory.....                          | 84  |

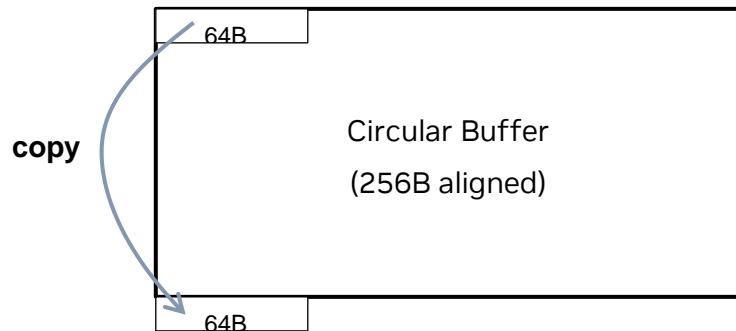

| 6.4.6      | Circular Buffer Addressing.....                               | 84  |

| Chapter 7. | Decoupled Lookup Unit (DLUT).....                             | 88  |

| 7.1        | Overview.....                                                 | 88  |

| 7.2        | DLUT Features.....                                            | 89  |

| 7.3        | Task Structure and Operation Modes.....                       | 90  |

| 7.4        | Task Sequencing and VPU/DLUT Interaction.....                 | 91  |

| Chapter 8. | Programming Examples .....                                    | 92  |

| 8.1        | Typical Test Case Organization.....                           | 92  |

| 8.2        | 1D Array Addition.....                                        | 93  |

| 8.2.1      | Scalar Code.....                                              | 93  |

| 8.2.2      | Optimization 1: Vectorized Code.....                          | 95  |

| 8.2.3      | Optimization 2: Unroll and Pipeline the Loop.....             | 97  |

| 8.3        | 2D Array Addition.....                                        | 100 |

| 8.3.1      | Scalar Code.....                                              | 100 |

| 8.3.2      | Optimization 1: Vectorized, Unrolled and Pipelined Loop ..... | 102 |

| 8.3.3      | Optimization 2: Leveraging Agen to Collapse Nested Loops..... | 105 |

|            |                                                                |     |

|------------|----------------------------------------------------------------|-----|

| 8.3.4      | Performance Across 2D Array Dimensions .....                   | 109 |

| 8.4        | 2D Convolution.....                                            | 109 |

| 8.4.1      | Scalar Code.....                                               | 109 |

| 8.4.2      | Optimization 1: Vectorized and Agen Optimized Loop.....        | 112 |

| 8.4.3      | Optimization 2: Leveraging Denser MAC Instruction .....        | 120 |

| 8.4.4      | Further Optimization for Power .....                           | 125 |

| 8.5        | Interpolated 2D Lookup.....                                    | 127 |

| 8.5.1      | Scalar Code.....                                               | 127 |

| 8.5.2      | VPU Parallel Lookup .....                                      | 128 |

| 8.5.3      | VPU Parallel Lookup in Two Loops.....                          | 130 |

| 8.5.4      | Leveraging DLUT .....                                          | 132 |

| Chapter 9. | Instruction Set Reference .....                                | 135 |

| 9.1        | VPU Changes from Xavier to Orin .....                          | 135 |

| 9.2        | VPU Math Operation Throughput.....                             | 137 |

| 9.2.1      | Multiply/MAC Instructions .....                                | 137 |

| 9.2.2      | MAC-Related Instructions .....                                 | 139 |

| 9.2.3      | Other Accelerated Vector Math Instructions.....                | 140 |

| 9.2.4      | Scalar/Vector Floating-point Instructions.....                 | 141 |

| 9.2.5      | Scalar Integer Math Instructions.....                          | 142 |

| 9.3        | VPU Compatibility .....                                        | 144 |

| 9.3.1      | Compatibility Exceptions .....                                 | 144 |

| 9.3.2      | Removed/Emulated Instructions .....                            | 145 |

| 9.4        | Instruction Execution Ordering .....                           | 145 |

| 9.4.1      | Processor Pipeline .....                                       | 145 |

| 9.4.2      | Default/General Behavior.....                                  | 146 |

| 9.4.3      | Delay Slots for Branch Instructions.....                       | 147 |

| 9.4.4      | Exception for Instructions Accessing Address Generator .....   | 147 |

| 9.4.5      | Exception for Instructions Accessing HW Loop Registers.....    | 148 |

| 9.4.6      | Exception for Instructions Accessing FP Invalid Flag.....      | 149 |

| 9.4.7      | Hardware Stalls to Comply with Sequential Execution Order..... | 150 |

| 9.5        | Instruction Predication .....                                  | 151 |

| 9.5.1      | Instruction-Level Predication for Register Moves .....         | 151 |

| 9.5.2      | Instruction-Level Predication for Vector Math .....            | 151 |

| 9.5.3      | Predication for Load/Store.....                                | 152 |

| 9.6        | Control Instructions .....                                     | 154 |

| 9.6.1      | Instruction Summary.....                                       | 154 |

| 9.6.2      | Branch/Jump/Call Delay Slots.....                              | 156 |

| 9.6.3      | Jump and Link (JAL, JALR).....                                 | 157 |

| 9.6.4      | Jump (J, JR).....                                              | 158 |

| 9.6.5      | Conditional Branch (BEQZ, BNEZ).....                           | 159 |

|             |                                                          |     |

|-------------|----------------------------------------------------------|-----|

| 9.6.6       | Software Break Point (SWBRK) .....                       | 159 |

| 9.6.7       | Hardware Zero-Overhead Loop (RPT) .....                  | 160 |

| 9.6.8       | General Purpose Output (GPO_*) .....                     | 161 |

| 9.6.9       | General Purpose Input (GPI_RD) .....                     | 164 |

| 9.6.10      | Wait for GPI Event (WFE_GPI) .....                       | 164 |

| 9.6.11      | Wait for R5 Event (WFE_R5) .....                         | 165 |

| 9.6.12      | Signal R5 (SIG_R5) .....                                 | 165 |

| 9.6.13      | Performance Counter (ENABLE/RD_TSC) .....                | 166 |

| 9.6.14      | Floating-Point Invalid Flag .....                        | 167 |

| 9.6.15      | OCD Load/Store .....                                     | 168 |

| 9.6.16      | Configure VMEM Superbanks (CFG_VMEM_SBA/B/C) .....       | 168 |

| 9.6.17      | Coprocessor Control/Status Register Load/Store .....     | 169 |

| 9.6.18      | Memory Fence .....                                       | 170 |

| 9.7         | Scalar ALU Instructions .....                            | 171 |

| 9.7.1       | ALU RRR Instructions .....                               | 171 |

| 9.7.2       | ALU RIR Instructions .....                               | 182 |

| 9.7.3       | Long Multiplication Instructions .....                   | 193 |

| 9.7.4       | Predicate Instructions .....                             | 195 |

| 9.7.5       | Scalar Floating-point Instructions .....                 | 202 |

| 9.7.6       | Other Scalar ALU Instructions .....                      | 225 |

| 9.8         | Vector ALU Instructions .....                            | 232 |

| 9.8.1       | Move Instructions .....                                  | 232 |

| 9.8.2       | Vector OP11 Instructions .....                           | 239 |

| 9.8.3       | Vector OP12 Instructions .....                           | 254 |

| 9.8.4       | Vector OP21 Instructions .....                           | 263 |

| 9.8.5       | Vector OP22 Instructions .....                           | 295 |

| 9.8.6       | Vector OP31 Instructions .....                           | 300 |

| 9.8.7       | Vector Multiply-Add Instructions .....                   | 326 |

| 9.8.8       | Vector Floating-point Instructions .....                 | 370 |

| 9.8.9       | Vector Misc Instructions .....                           | 405 |

| 9.9         | Load/Store Instructions .....                            | 414 |

| 9.9.1       | Scalar Load/Store .....                                  | 414 |

| 9.9.2       | Scalar-Based Vector Load/Store .....                     | 417 |

| 9.9.3       | Agen Configuration .....                                 | 423 |

| 9.9.4       | Agen-Based Vector Load/Store .....                       | 436 |

| 9.9.5       | Agen-Based Scalar Load/Store .....                       | 455 |

| 9.9.6       | Parallel Lookup, Histogram, Vector Addressed Store ..... | 458 |

| 9.9.7       | Misc Register Store .....                                | 473 |

| Chapter 10. | Decoupled Lookup Unit (DLUT) Reference .....             | 475 |

| 10.1        | Index and Output Data Format .....                       | 475 |

|             |                                                              |     |

|-------------|--------------------------------------------------------------|-----|

| 10.2        | Table Data Format .....                                      | 479 |

| 10.3        | Index Calculation .....                                      | 481 |

| 10.3.1      | 1D Lookup .....                                              | 481 |

| 10.3.2      | 1D Lookup with interpolation.....                            | 482 |

| 10.3.3      | 2D Lookup.....                                               | 483 |

| 10.3.4      | 2D Lookup with Interpolation.....                            | 484 |

| 10.3.5      | 2D Lookup with Interpolation with Auto Index Generation..... | 485 |

| 10.4        | Duplicate Detection and Consolidation.....                   | 487 |

| 10.5        | Conflict Resolution and Lookup .....                         | 487 |

| 10.6        | Post Lookup Interpolation .....                              | 487 |

| 10.7        | 2D Conflict-free Lookup with Interpolation .....             | 488 |

| 10.8        | Table Reformatting .....                                     | 490 |

| 10.9        | VPU/DLUT Interface .....                                     | 493 |

| 10.9.1      | Task Parameters.....                                         | 493 |

| 10.9.2      | Interaction Sequence .....                                   | 497 |

| 10.9.3      | Incorrect Task Configuration .....                           | 499 |

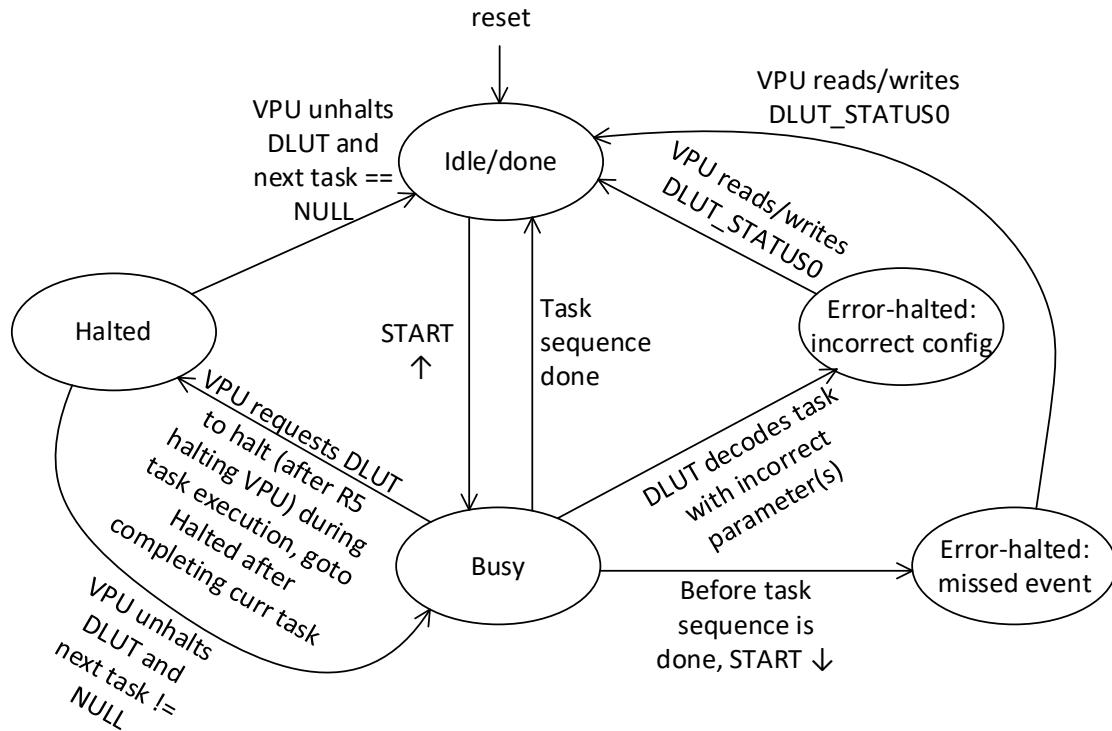

| 10.9.4      | DLUT Execution States, Error Handling, Halt and Debug .....  | 500 |

| 10.9.5      | Other Control/Status Registers .....                         | 503 |

| Chapter 11. | Register Spec.....                                           | 504 |

| 11.1        | VPS Coprocessor Registers.....                               | 504 |

| 11.1.1      | Revision ID Register.....                                    | 504 |

| 11.1.2      | DLUT Task Control/Status Registers .....                     | 505 |

| Chapter 12. | General Purpose Input/Output .....                           | 507 |

| 12.1        | VPU/DMA Control Interface.....                               | 507 |

| 12.2        | Summary of GPI/GPO Signals .....                             | 508 |

| Chapter 13. | Design for Test and Safety .....                             | 510 |

| 13.1        | Debug Features.....                                          | 510 |

| 13.2        | Soft Error Cases and Handling.....                           | 511 |

| 13.3        | Safety Features.....                                         | 514 |

# List of Figures

|                                                                                                           |     |

|-----------------------------------------------------------------------------------------------------------|-----|

| Figure 1. VPU Subsystem (VPS) block diagram .....                                                         | 16  |

| Figure 2. VPU core block diagram .....                                                                    | 18  |

| Figure 3. VMEM block diagram.....                                                                         | 27  |

| Figure 4. VMEM access pattern examples for consecutive accesses .....                                     | 31  |

| Figure 5. VMEM transposed access pattern examples .....                                                   | 31  |

| Figure 6. VMEM access pattern examples for parallel table lookup and histogram .....                      | 32  |

| Figure 7. AGEN data format in memory.....                                                                 | 38  |

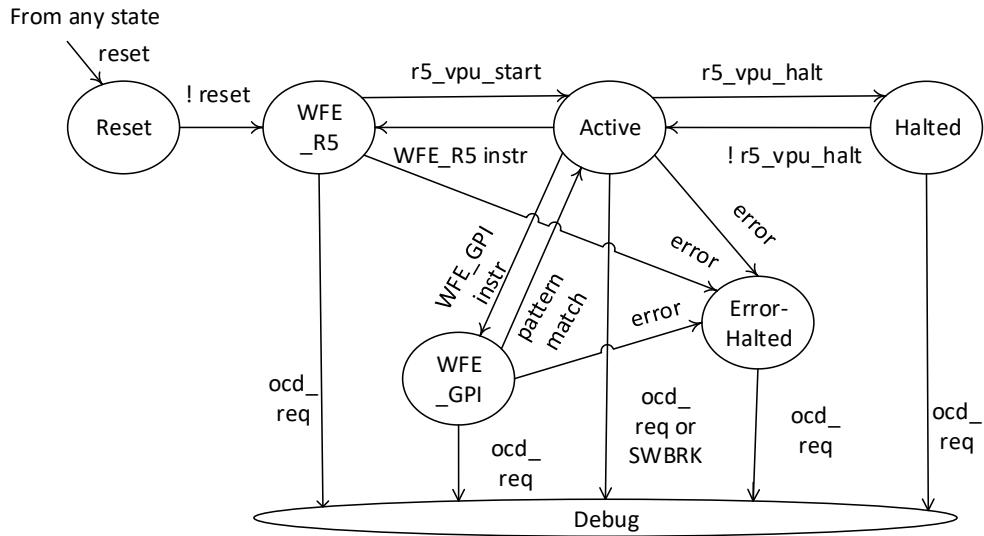

| Figure 8. VPU execution state diagram .....                                                               | 43  |

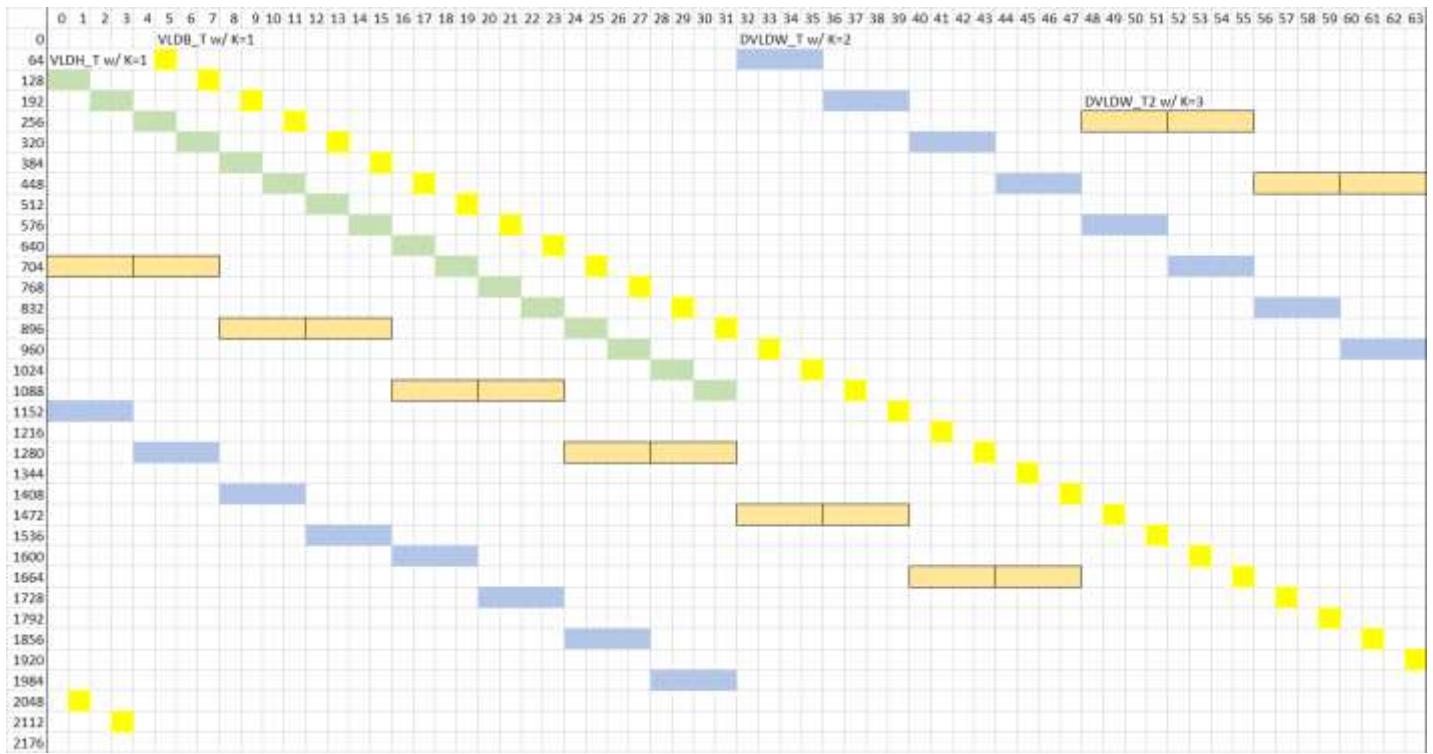

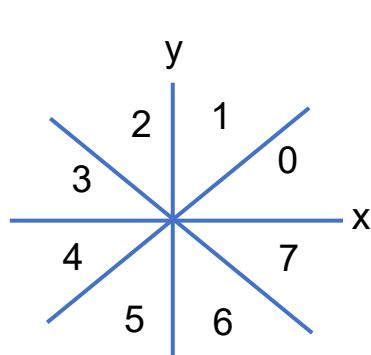

| Figure 9. Access patterns of transposition modes T and T2 .....                                           | 69  |

| Figure 10. Access patterns of transposition modes T4, T8, T16 and T32 .....                               | 70  |

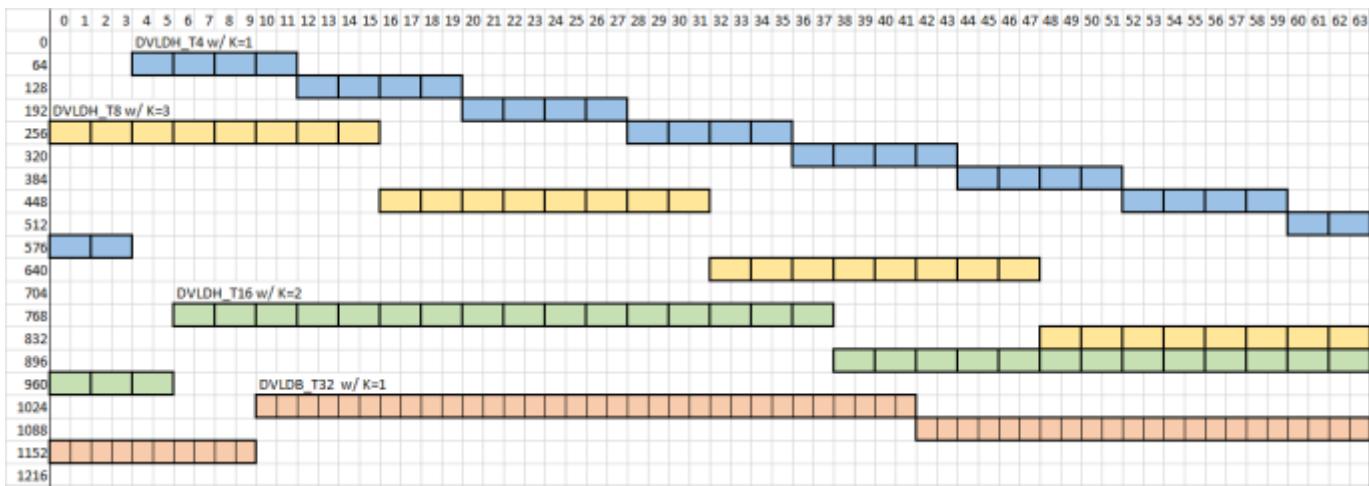

| Figure 11. Parallel lookup, histogram and VAST data organization for various types and parallelism.....   | 71  |

| Figure 12. Workaround for vector accesses across circular buffer boundary.....                            | 87  |

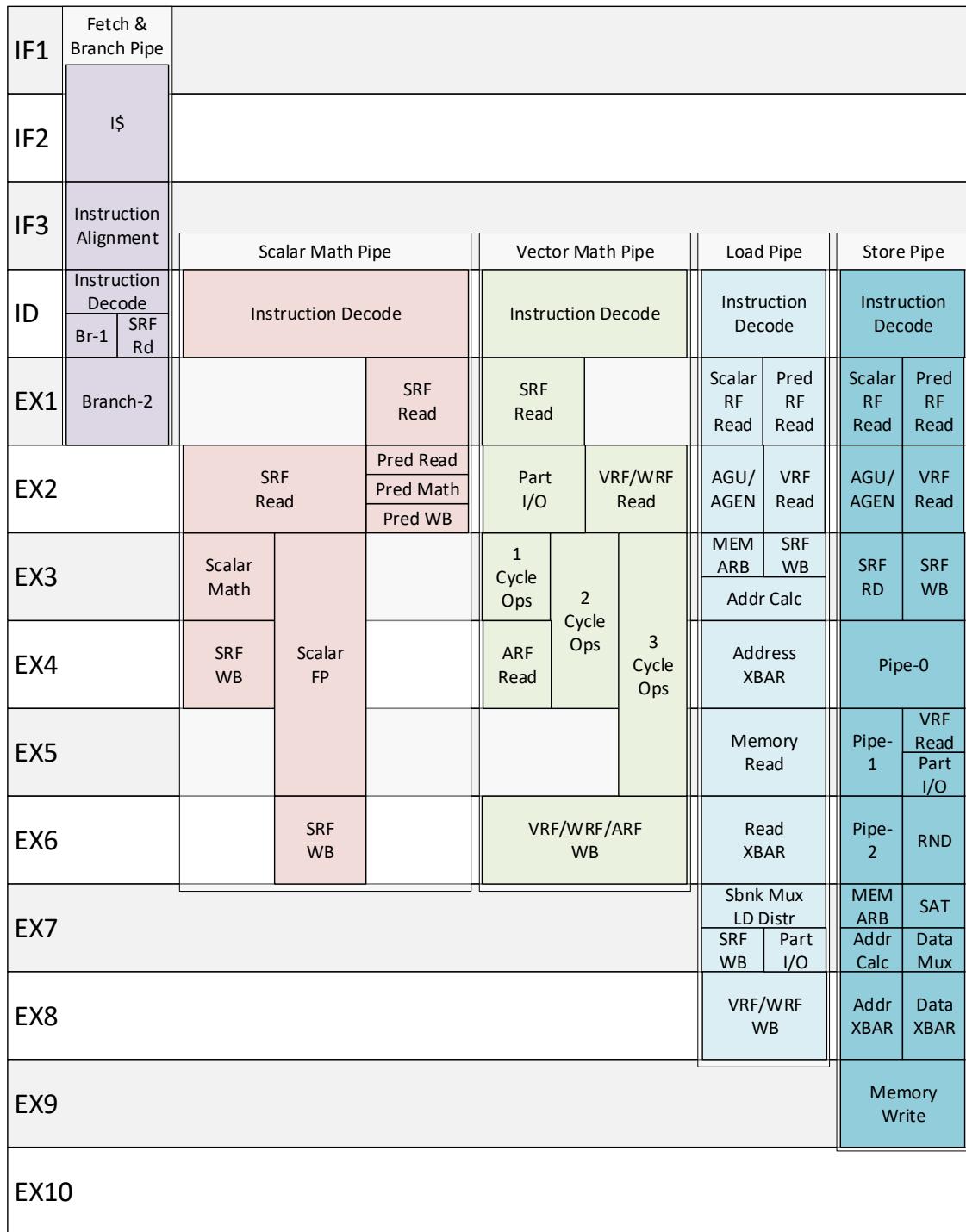

| Figure 13. VPU processor pipeline .....                                                                   | 146 |

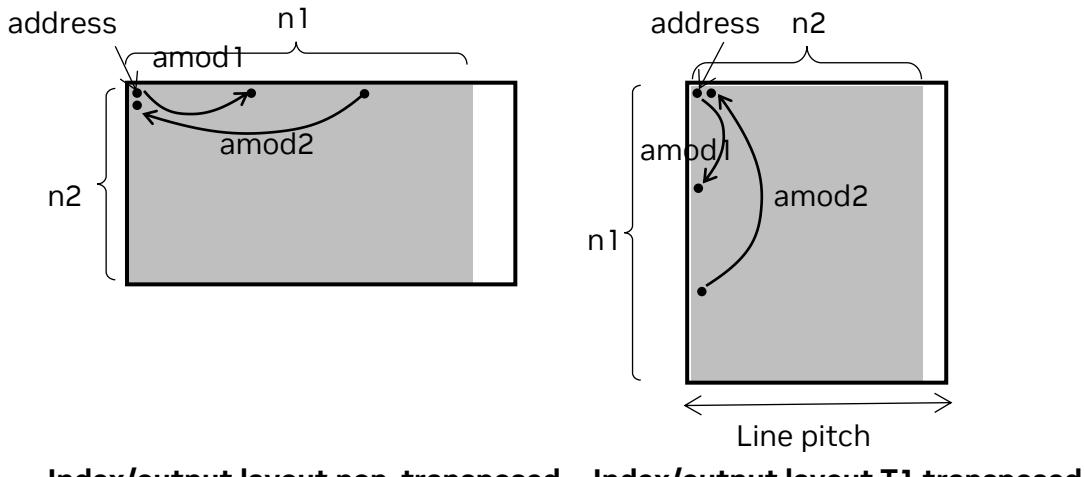

| Figure 14. DLUT index/output data layout .....                                                            | 477 |

| Figure 15. DLUT table data layout.....                                                                    | 479 |

| Figure 16. Example to leverage out-of-range handling to split a large table as two sub-table lookups..... | 481 |

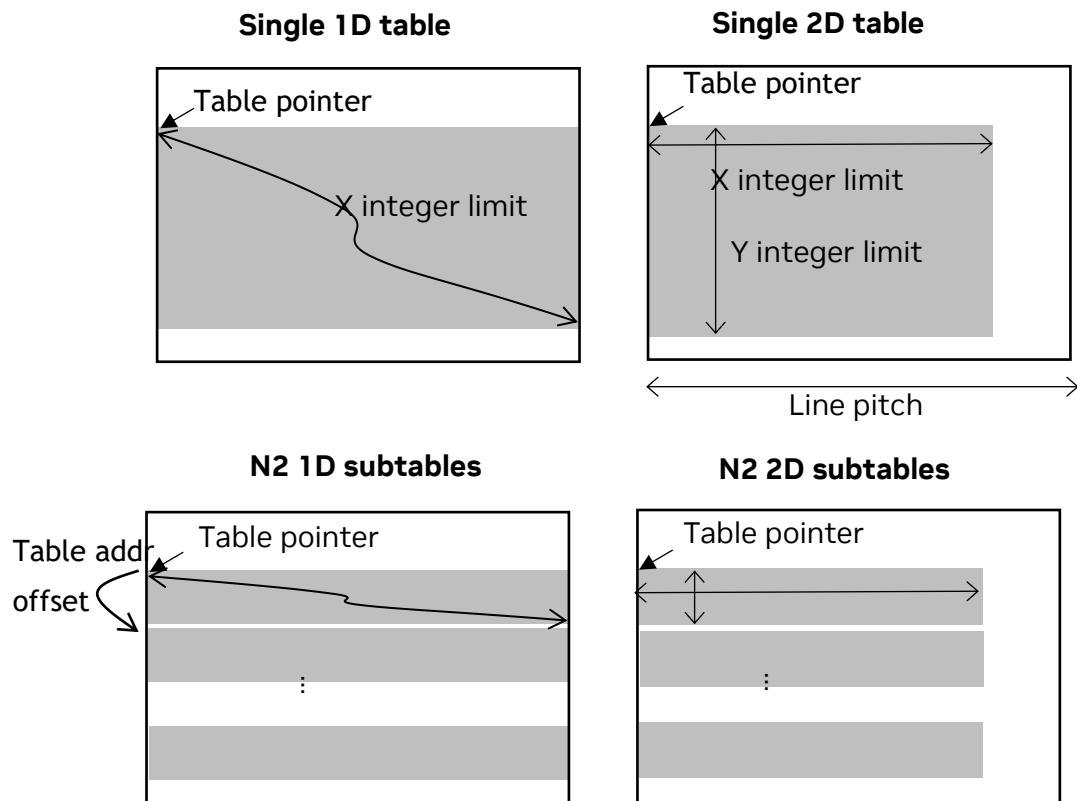

| Figure 17. Table layout for VPU lookup instructions.....                                                  | 488 |

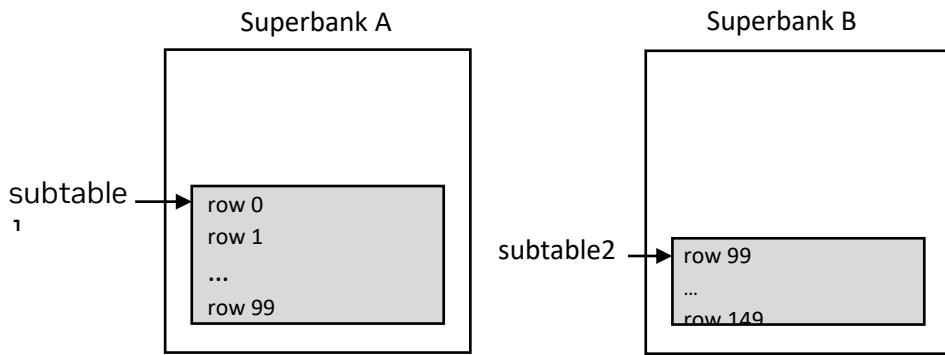

| Figure 18. Table layout for DLUT 2D conflict-free lookup w/ interpolation .....                           | 489 |

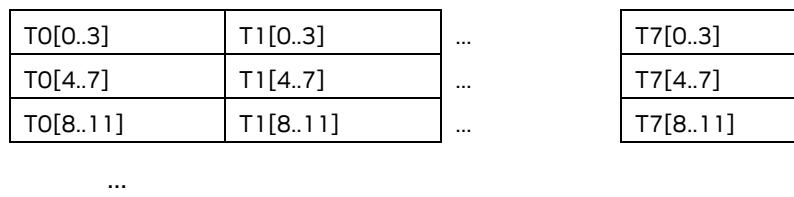

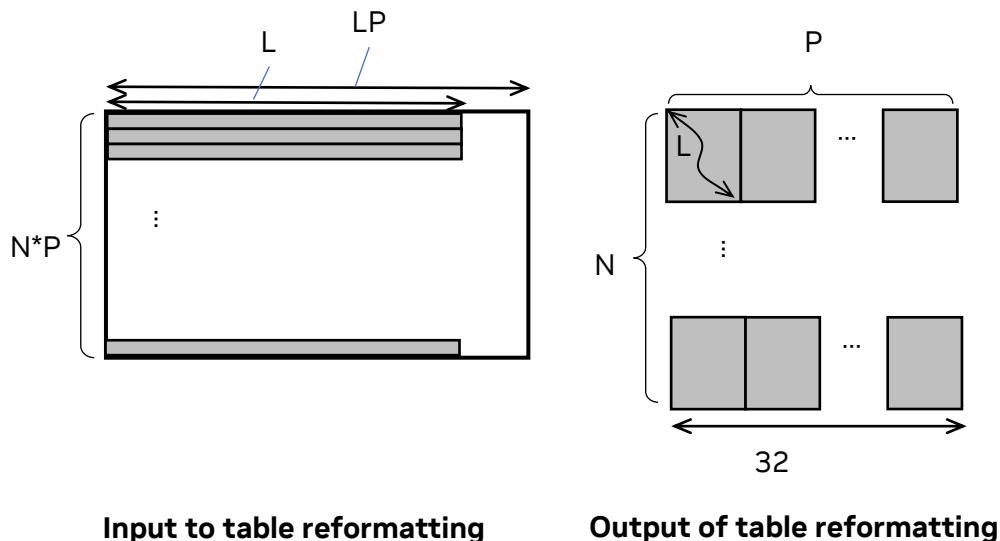

| Figure 19. Table reformatting input/output layout scheme .....                                            | 491 |

| Figure 20. Table reformatting input/output layout example .....                                           | 492 |

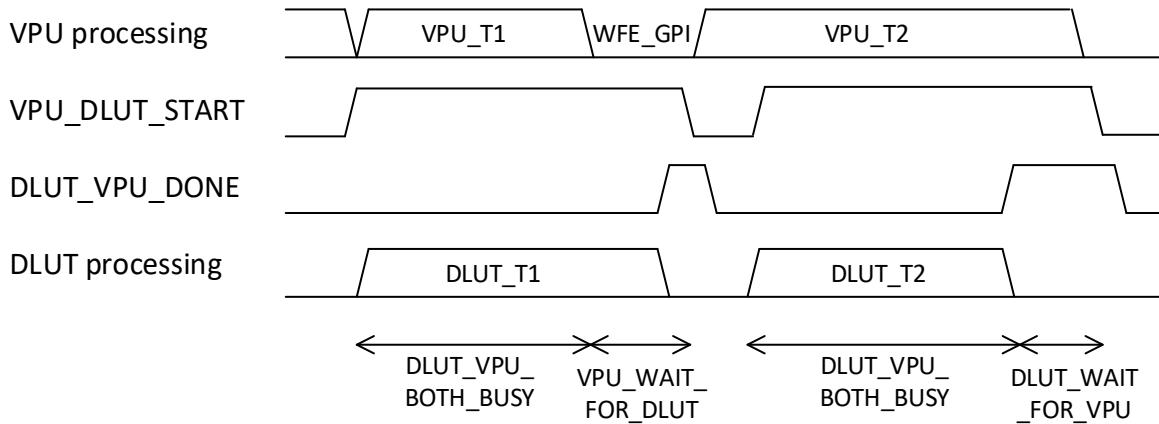

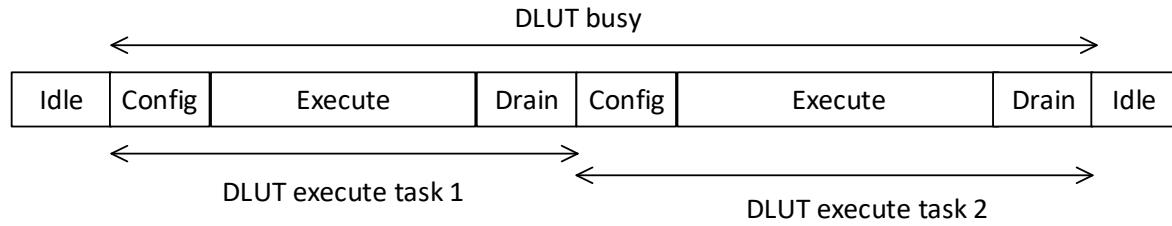

| Figure 21. VPU/DLUT interaction timing diagram .....                                                      | 498 |

| Figure 22. DLUT processing stages.....                                                                    | 499 |

| Figure 23. DLUT execution state conceptual state diagram.....                                             | 501 |

# List of Tables

|                                                                      |     |

|----------------------------------------------------------------------|-----|

| Table 1. Support of scalar/vector operations in register files ..... | 20  |

| Table 2. VPU I-cache characteristics.....                            | 22  |

| Table 3. VMEM address map.....                                       | 29  |

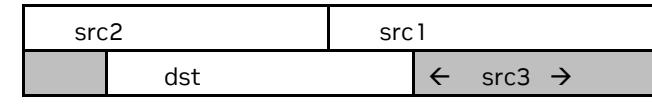

| Table 4. VLIW instruction format .....                               | 35  |

| Table 5. Little Endian layout of various data types .....            | 51  |

| Table 6. FP add/subtract/multiply corner cases.....                  | 54  |

| Table 7. FP multiply-add/subtract corner cases.....                  | 55  |

| Table 8. FP multiply corner cases in Gen-1 and Gen-2 VPU.....        | 56  |

| Table 9. FP/INT conversion corner cases.....                         | 57  |

| Table 10. Scalar load/store data types.....                          | 62  |

| Table 11. Scalar-based vector load/store data types.....             | 63  |

| Table 12 Agen-based vector load/store data types.....                | 63  |

| Table 13. Line pitch constraint for various transposition modes..... | 67  |

| Table 14. Table lookup 2-point and 2x2-point support.....            | 73  |

| Table 15. Histogram support .....                                    | 75  |

| Table 16. Vector addressed store support .....                       | 75  |

| Table 17. Performance optimization across array dimensions .....     | 109 |

| Table 18. Multiply/MAC instructions.....                             | 137 |

| Table 19. Scalar/vector load/store predication support.....          | 152 |

| Table 20. Vector register predicated vector store variations.....    | 153 |

| Table 21. Control instructions .....                                 | 155 |

| Table 22. Scalar ALU RRR instructions.....                           | 171 |

| Table 23. Scalar ALU RIR instructions.....                           | 182 |

| Table 24. Scalar ALU long multiply instructions .....                | 193 |

| Table 25. Scalar predicate instructions .....                        | 196 |

| Table 26. Scalar floating-point instructions.....                    | 202 |

| Table 27. Other scalar ALU instructions .....                        | 225 |

| Table 28 Scalar/vector move instructions .....                       | 232 |

| Table 29 vector register move support matrix .....                   | 233 |

| Table 30. Vector OP11 instructions .....                             | 239 |

| Table 31. Vector OP12 instructions .....                             | 254 |

| Table 32 Vector OP21 instructions .....                              | 263 |

| Table 33. Vector OP22 instructions .....                             | 295 |

| Table 34 Vector OP31 instructions .....                              | 300 |

| Table 35. Vector multiply-add instructions .....                     | 330 |

| Table 36. Vector floating-point instructions.....                    | 370 |

| Table 37. Vector miscellaneous instructions.....                     | 405 |

| Table 38. Scalar load/store instructions .....                       | 414 |

|                                                                                |     |

|--------------------------------------------------------------------------------|-----|

| Table 39. Scalar-based vector load/store instructions.....                     | 417 |

| Table 40. Agen config instructions.....                                        | 423 |

| Table 41. Agen-based vector load/store instructions.....                       | 436 |

| Table 42. Agen-based scalar load/store instructions .....                      | 455 |

| Table 43 Parallel lookup, histogram, vector addressed store instructions ..... | 459 |

| Table 44 Miscellaneous register store instructions.....                        | 473 |

| Table 44 Index and output line pitch and transpose modes.....                  | 477 |

| Table 45. DLUT task parameter data structure.....                              | 493 |

| Table 46. DLUT parameter usage and constraints.....                            | 496 |

| Table 47. VPU revision ID register.....                                        | 504 |

| Table 48. VPU DLUT task control/status registers.....                          | 505 |

| Table 49. VPU/DMA control signal list.....                                     | 507 |

| Table 50. VPU GPI/GPO signal list .....                                        | 508 |

| Table 51. VPU soft error cases and handling.....                               | 512 |

| Table 52. VPU safety error cases and handling .....                            | 514 |

---

# Chapter 1. Introduction

## 1.1 Document Scope

This document serves as a Programmer’s Guide for PVA VPU. It covers VPU processor architecture, instruction set overview, example code, and instruction details.

## 1.2 References

### 1.2.1 Related External Documents

- PVA SDK Documentation

### 1.2.2 Related NVIDIA-Internal Documents

- PVA VPS IAS

- PVA Cluster IAS

- PVA DMA IAS

- PVA L1 RAMIC IAS

- PVA VPS MAS

- PVA DLUT MAS

## 1.3 Glossary and Acronyms

|            |                                                                                                                                                                               |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>CV</b>  | Computer vision, field of study and application to recover 3D and motion information from camera views.                                                                       |

| <b>PVA</b> | Programmable vision accelerator, a unit in Orin that accelerates computer vision algorithms in autonomous driving use cases, includes VPU, DMA, and Cortex R5 RISC processor. |

| <b>SEC</b> | Safety and Event Control at PVA top level. It collects safety error events in PVA, logs, aggregates, and forwarded as interrupts to the Cortex R5 processor.                  |

| <b>VPU</b> | Vector processing unit, the main data processing engine in PVA.                                                                                                               |

|               |                                                                                                                                                                             |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>VMEM</b>   | VPU vector memory, the local/L1 data memory for VPU, also shared with DMA and DLUT                                                                                          |

| <b>DMA</b>    | Direct memory access, a hardware block in charge of copying data between local memory and some other space in the system, which can be on-chip memory or system memory/DDR. |

| <b>DLUT</b>   | Decoupled lookup unit                                                                                                                                                       |

| <b>VPS</b>    | VPU subsystem, including VPU, its I-cache, DLUT and VMEM                                                                                                                    |

| <b>Host1X</b> | Command and synchronization unit that works with CPU, image/video processing and computer vision engines                                                                    |

| <b>ISP</b>    | Image Signal Processor, processes camera images                                                                                                                             |

| <b>VIC</b>    | Video and Image Compositor, capable of affine/perspective image transformation and format conversion                                                                        |

| <b>OFA</b>    | Optical Flow Accelerator, capable of dense optical flow and stereo disparity                                                                                                |

| <b>DLA</b>    | Deep Learning Accelerator                                                                                                                                                   |

---

# Chapter 2. Architecture Overview

A high-level overview of PVA, DMA, and VPS architecture is given in this chapter. For more in-depth coverage of PVA architecture and DMA programming details, please consult PVA SDK documentation.

## 2.1 PVA

PVA (programmable vision accelerator) is a computer vision (CV) processor targeting Autonomous Driving (AD) applications, including camera, LiDAR, RADAR processing and sensor fusion. PVA includes a control processor, Cortex R5, 2 copies of vector processing subsystems (VPS) as data processing engines, and 2 copies of directed memory access (DMA) as data movement engines. Orin PVA also includes an L2 SRAM memory to be shared between the 2 sets of VPS and DMA.

The Cortex R5 processor interacts with other SOC components (for example, ISP, VIC, OFA, DLA) through Host1X for control and synchronization at the subframe-application level. R5 configures the VPUs and DMAs at the task level.

The VPUs act like coprocessors in system-level programming model. For each VPU task, R5 configures DMA, optionally prefetches VPU program into VPU I-cache, and kicks off each VPU-DMA pair to process a task that runs for typically hundreds of micro-seconds to a few mini-seconds. Each VPU and DMA pair synchronize between themselves on tile granularity, and there are typically tens to hundreds of tiles per task.

For Orin, the second generation of PVA, we have one PVA having 2 VPUs, each VPU having 2 symmetrical vector functional units of 384-bit data path each.

For memory operations we have 3x32x16-bit throughput, having 3 memory slots and 3 superbanks, each superbank comprising of 32 banks of 16-bit-wide memories, and each superbank can perform both read and write in the same clock cycle.

## 2.2 DMA

DMA moves data among external memory, PVA L2 memory, the 2 VMEMs (one in each VPS), R5 TCM (tightly coupled memory), DMA descriptor memory, and PVA-level config registers.

Orin DMA contains the following resources

- 16 channels, each channel can be configured to move data from a source to a destination. The 16 channels work in parallel and can be optionally coordinated through programming.

- 64 descriptors, each descriptor includes up to 5 dimensions to advance source/destination address pointers. Descriptors can work in parallel or in sequence through programming.

- A set of internal buffers (ADB and VDB) to be allocated among channels. ADB, AXI data buffer, is for storing data read from the external memory controller temporarily, and VDB, VMEM data buffer, is for storing data read from the VMEM temporarily.

Please consult PVA SDK documentation for additional details in DMA programming.

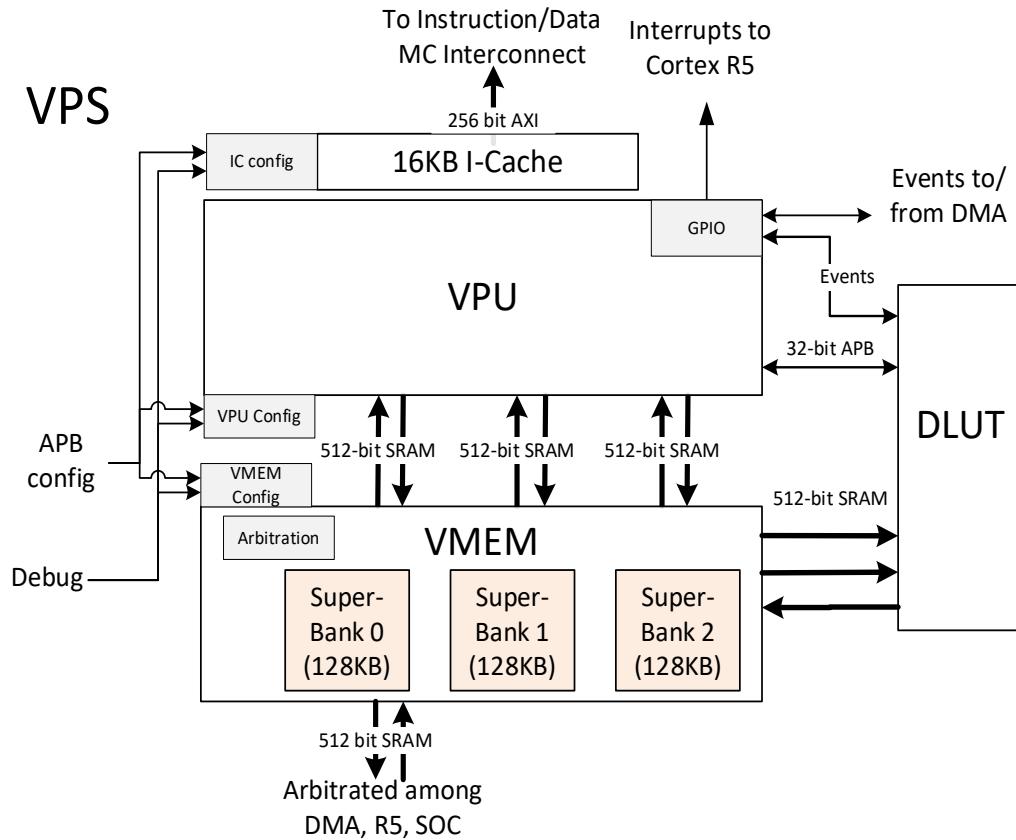

## 2.3 VPS

The VPU Subsystem (VPS) consists of the following major components:

- VPU core, the processor and main block of VPS.

- VPU instruction cache (I-cache) supplies instruction words to VPU and maintains temporary instruction storage, with prefetch/invalidation support and with interface to the system memory through MC interconnects.

- VPU vector memory (VMEM) houses data memory and supports various complex memory access functionalities, including transposition, table lookup, histogram, and vector addressed stores. It also supports accesses from outside-VPS hosts like DMA and R5, to allow data exchange with R5 and other system-level components.

- DLUT, decoupled lookup coprocessor, offloads lookup and interpolation tasks from VPU

Each major component will be described in more detail in subsequent chapters.

The following block diagram of VPS shows the major components in VPS and how they are connected.

Figure 1. VPU Subsystem (VPS) block diagram

## 2.4 VPU Processor Models and Differences

To facilitate model development as well as application software development, a number of VPU processor models have been constructed.

The most accurate model is the deep pipeline (Working) model. The VPU working model instruction set simulator (ISS) shall be cycle accurate with VPU processor inside Orin silicon.

There is a Native compilation model generated by the ASIP tool suite from the shallow pipeline model. It is mostly an application development platform. It is a collection of header files and C library that allows application code to be compiled in generic (thus named Native) environments, including Linux GCC and Windows Microsoft Visual Studio. It is functionally accurate with hardware for math operations. In memory operations it is mostly functionally accurate with hardware, but there are exceptions.

Because Native is compiled in a generic compute platform, there is no hard limit in data memory footprint, so is useful for early-stage software development. In this platform VPU code can access almost unlimited amount of memory, to directly process a whole frame of image, as opposed to processing one tile at a time through DMA.

Note that, depending on the physical memory size of the compute platform it is run on, large enough memory usage in Native simulation may still lead to excessive thrashing and slowdown.

Differences in behavior between Native compilation environment and final product, which is deep pipeline ISS and silicon are:

- There is no notion of clock cycles in Native compilation, thus Time Stamp Counter is not functional.

- There is no forced memory address alignment to 16-bit/32-bit with load/store of short/int types (see [Memory Address Alignment](#)).

- There is no forced memory address alignment to 512-bit with lookup, histogram, or vector-addressed stores (see [Memory Address Alignment](#)).

- There is no forced memory address alignment to 512-bit with agen circular buffer feature (see [Circular Buffer Addressing](#)).

- General purpose input and output (GPIO) in Native is non-functional, toggling GPO ignored and reading GPI returns 0. In ISS, the subset of GPIO pins that connect to the decoupled lookup coprocessor (DLUT) are functional for interaction between VPU and DLUT.

In working model ISS, the decoupled lookup table coprocessor (DLUT) is simulated functionally accurately (bit-exact), but is currently only cycle approximate, NOT cycle-accurate.

Although PVA-level simulator incorporating R5, DMA, VPU, DLUT component simulators does incorporate budgetary system-level latency, for example external memory controller latency, but it does not model components outside PVA so cannot predict actual latency. Thus, PVA-level simulation, even when incorporating cycle-accurate VPU working ISS, is NOT cycle-accurate with silicon when the simulation involves outside-VPU interactions, for example, reading from or writing to external memory.

# Chapter 3. VPU Core

## 3.1 Block Diagram

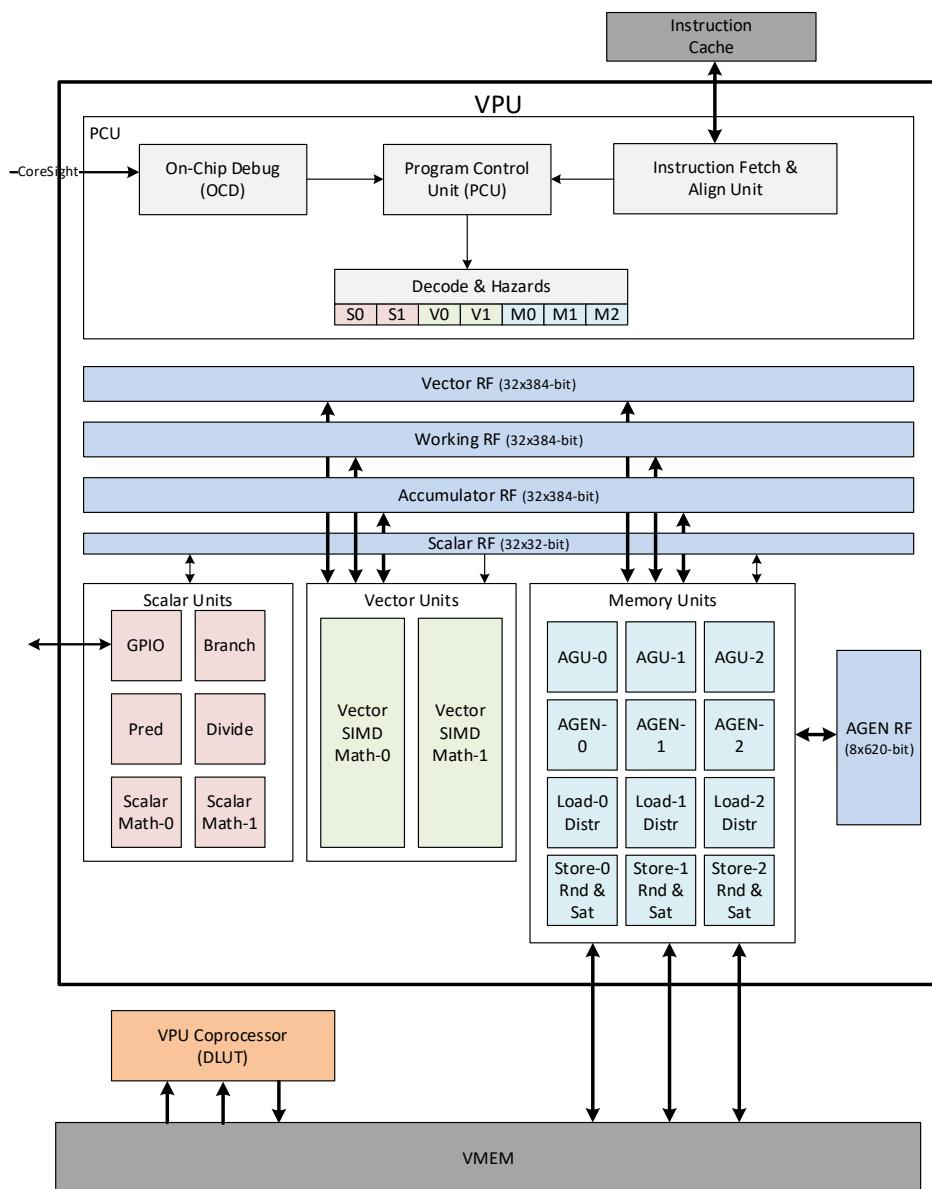

Figure 2. VPU core block diagram

The VPU core is a vector SIMD VLIW DSP optimized for computer vision. It fetches instructions through the I-cache, and accesses data through the vector memory (VMEM). Major components inside VPU core are

- Processor front end including config/status interface and PC control

- Register files

- Scalar unit with two scalar ALUs

- Vector unit with two vector ALUs

- Memory unit with 3 load/store units and address generators

## 3.2 Processor Front End

The VPU instruction format is a 7-way VLIW, consisting of:

- 2 scalar operation slots (s0/s1)

- 2 vector operation slots (v0/v1)

- 3 memory slots (m0/m1/m2)

Each instruction is encoded in 32-bit, and the instruction encoding supports variable-length instructions, thus each execution packet contains between 1 and 7 32-bit words. The compressed instruction stream is decompressed to full 7 instructions per packet and dispatched to the scalar, vector, and memory units.

Example of compressed instruction packet:

```

ADD R1, R2, R3 || LDW *R4[20], R5

```

Corresponding decompressed instruction packet:

```

ADD R1, R2, R3 || s1_NOP || v0_NOP || v1_NOP || LDW *R4[20], R5 || m1_NOP || m2_NOP

```

The front end of the processor includes an interface to the instruction cache, 2-level hardware loops, loop instruction buffer, and fetch/decode stages of the processor pipeline.

The front end includes illegal instruction detection, both while expanding compressed variable-length instruction packet into full 7-instruction packet using leading few bits of each 32-bit instruction, and while decoding entire 32-bit instruction in scalar/vector/memory units.

## 3.3 Register Files

The following register files are in the VPU core:

- Scalar register file (Scalar RF): 32 entries x 32-bit

- Predicate register file (Predicate RF): 16 entries x 32-bit

- Main vector register file (VRF): 32 entries x 384-bit

- Working register file (WRF): 32 entries x 384-bit

- Extended accumulator register file (XARF): 32 entries x 512-bit

- Accumulator register file (ARF): 32 entries x 384-bit, part of XARF

- > Agen register file: 8 entries x 620-bit

The vector register files VRF, WRF and ARF support the following data types:

- > Word: each 384-bit entry is logically partitioned into 8 lanes x 48-bit

- > Halfword: each 384-bit entry is logically partitioned into 16 lanes x 24-bit

- > Byte: each 384-bit entry is logically partitioned into 32 lanes x 12-bit

XARF register file supports

- > Word: each 512-bit entry partitioned into 16 lanes x 32-bit (for VFilt4x2x2BBW, VDotP4BBW, VDotP4x2BBW instructions)

- > Halfword: each 512-bit entry partitioned into 32 lanes x 16-bit (for VXNorAnd8x4x2 instruction)

Support of operations in various register files is tabulated as follows:

**Table 1. Support of scalar/vector operations in register files**

|                                      | <b>Scalar RF</b> | <b>Predicate RF</b>         | <b>VRF</b>              | <b>WRF</b>    | <b>ARF/XARF</b>      |

|--------------------------------------|------------------|-----------------------------|-------------------------|---------------|----------------------|

| <b>Scalar math</b>                   | Yes              | Yes, as src or dst of a few |                         |               |                      |

| <b>Instruction level predication</b> |                  | Yes                         |                         |               |                      |

| <b>Per-lane predication</b>          |                  | Yes                         | V0~V15                  |               |                      |

| <b>Vop11/12</b>                      |                  |                             | Yes                     | Yes           |                      |

| <b>Vop21</b>                         | Yes, as src2     |                             | Yes                     | Yes           |                      |

| <b>Vop31</b>                         | some, as src2    |                             | Yes                     | some          |                      |

| <b>Vop31_CA, MAC</b>                 | some, as src2    | Yes, P0~P15 as predicate    | Yes, as src1, src2, dst | some, as src2 | Yes, as dst, src3dst |

| <b>FP</b>                            | Yes              |                             | Yes                     | Yes           |                      |

| <b>Load destination</b>              | Yes              |                             | Yes                     | Yes           |                      |

| <b>Store source</b>                  | Yes              |                             | Yes                     |               | Yes                  |

## 3.4 Scalar Unit

The scalar unit supports conventional scalar RISC instruction set, executing up to 2 scalar operations per cycle.

32-bit integer/fixed-point as well as 16/32-bit floating-point Add, Sub, Mul, MAdd, compare operations are supported through instructions. Some FP32 math functions (square root, reciprocal, reciprocal of square root, exp2, log2, sin, cos, tanh) and various FP/INT conversions are supported as well.

## 3.5 Vector Unit

The vector unit executes up to 2 vector math instructions per cycle. Various integer arithmetic and logic operations are implemented in the vector unit, with support for Byte (extended to 12-bit), Halfword (extended to 24-bit) and Word (extended to 48-bit) data types. Bitwise logic operations are also supported.

In addition to conventional arithmetic/logic operations, some larger or complex operations (e.g., 3-input min/max/median) as well as FP32/FP16 operations Add, Sub, Mul, MAdd, and compare are supported. Some FP32 math functions (square root, reciprocal, reciprocal of square root, exp2, log2, sin, cos, tanh) and various FP/INT conversions are supported as well.

## 3.6 Load/Store Unit

The load/store unit supports up to 3 load/store instructions per cycle. Word, Halfword, Byte, and selected promotion/demotion options are supported. For load, both signed/unsigned flavors are supported. Source and destination can be single scalar register, double scalar register, single vector register, or double vector register. Quad-vector-register store is also available to facilitate key filtering benchmarks. Load/store unit also supports various data distributions.

In Orin we have added load-and-permute instructions to manipulate/reorganize data from a double vector in memory to a double vector register destination in any permutation pattern. This enables various data access patterns to be efficiently carried out through such instructions.

In general, we would like memory transactions from load/store instructions to be executed in order through memory dependency checking and dynamic stalling. The VPU has a rich set of load/store features, and for some features it is cost prohibitive to implement the dependency checking. Scalar load/store instructions as well as consecutive-location vector load/store are included in the dependency checking, so they are guaranteed to execute in order. Transposing load/store, parallel table lookup, parallel histogram, and vector addressed stores are excluded in the checking, so they are not guaranteed to execute in order. A MemFence instruction is available to serialize memory transactions that hardware dependency checking does not cover. See [Memory Coherency](#) for additional details.

---

# Chapter 4. VPU Instruction Cache (I-Cache)

## 4.1 Overview

The VPU Instruction Cache (I-cache) supplies instruction data to the VPU when requested, requests missing instruction data from system memory, and basically maintains temporary instruction storage for the VPU. It also implements the prefetch command to reduce cache misses, as well as the invalidation command as needed for error correction and debug.

Having an instruction cache allows for large total code size to be stored in the system memory, while having small physical memory footprint for area efficiency.

## 4.2 Functionality

The following table captures the characteristics of the I-cache.

Table 2. VPU I-cache characteristics

| Characteristic                                                                                                          | Configuration                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Capacity                                                                                                                | 16KB                                                                                                                                                           |

| Associativity                                                                                                           | 2-way                                                                                                                                                          |

| Instruction width                                                                                                       | 256-bit                                                                                                                                                        |

| Instruction alignment                                                                                                   | 256-bit                                                                                                                                                        |

| Block size                                                                                                              | 128 bytes                                                                                                                                                      |

| Replacement policy                                                                                                      | LRU                                                                                                                                                            |

| Write policy                                                                                                            | None (I-cache read only)                                                                                                                                       |

| Hit under miss (nonblocking, if/when VPU requests another instruction word that's available, go ahead and return hit)   | No, fetch interface is in-order, so after a miss, if following fetch request hits, it's not possible to indicate so.                                           |

| Miss under miss (if/when VPU requests another instruction word that's unavailable, request for that cache line as well) | Yes (request/ready pipelining allows following fetch request to be conveyed, and if it's a miss involving another cache line, request can be sent out as well) |

| Hit latency                                                                                                             | 2 cycles                                                                                                                                                       |

| Characteristic                                                      | Configuration                                                                                                                                                                                                                            |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Prefetch (software request to fetch cache lines ahead of execution) | Yes, up to full cache capacity in a single R5/VPU interaction. Depending on outstanding transaction allocation may request in batches                                                                                                    |

| Interface for misses                                                | 256-bit AXI, AR, R channels only                                                                                                                                                                                                         |

| Prefetch request from R5 and VPU                                    | Yes, will have separate config register entries for concurrency                                                                                                                                                                          |

| Prefetch and fetch concurrency                                      | Yes, giving fetch higher priority                                                                                                                                                                                                        |

| ECC single error correction                                         | Yes, corrected on the fly and sent back to VPU                                                                                                                                                                                           |

| ECC single/double error detection                                   | Single errors are corrected but correction not written back to cache; single error handling software should invalidate cache line to initiate refetch when the line is requested again.<br>Double errors are detected but not corrected. |

| Invalidation from R5                                                | Yes, configurable address range                                                                                                                                                                                                          |

| Invalidation from VPU                                               | Yes, configurable address range                                                                                                                                                                                                          |

## 4.2.1 Preemption

The VPU fetch/align unit fetches ahead of execution, and thus may request some instruction data, but in the next few cycles branches to another PC location that renders the previous request unnecessary. In such cases, the fetch/align unit cancels a previous request and issues a request for the new PC location. This feature is called preemption and is particularly useful when one of the no-longer-needed requests triggered a cache miss. VPU execution would be stalled if hardware does not have the capability to cancel such requests.

The I-cache handles preemption by clearing the preempted request from the pipeline. In case the preempted request has been sent to the MC, the MC read request is not affected, and returned data from MC would be written to a cache line normally, possibly evicting instruction data on that cache line.

## 4.2.2 Prefetch

Prefetch capability is provided to both the R5 and the VPU. They use separate register entries and command queues to avoid any race conditions, although SW on both sides should be coherent and not attempt to request prefetch or invalidation at the same time.

When a program for a task fits the I-cache, the R5 should prefetch the whole task, then start VPU at its task PC. The VPU may initially see instruction-cache misses until the whole task is loaded.

When program for a task does not fit the I-cache, we recommend that the task code is partitioned into subtasks for concurrent execution and prefetch. Given the 2-way set

associativity characteristics of instruction cache and the cache capacity of 16KB, each subtask should ideally be under 8KB.

The R5 should prefetch just the first subtask before starting the VPU task. VPU code for a subtask should prefetch the next subtask at the appropriate time so that ideally the prefetch is hidden behind execution.

R5 SW should not start requesting prefetch for VPU's next task until VPU has completed its current task and is idle. This also ensures prefetches from R5 and VPU do not contend for cache lines.

### 4.2.3 Invalidation

The I-cache supports two concurrent invalidation interfaces through the config registers; one designated for R5 and the other designated for VPU. Each invalidation interface can selectively invalidate an address range or the whole cache.

Invalidating the whole cache by VPU is supported via GPO sideband signaling (see [Summary of GPI/GPO Signals](#)). Invalidating an address range by VPU is currently not supported by software.

Invalidation can be used to provide a clean slate for I-cache at the beginning of every task, and the R5 should be the one invalidating the entire cache.

Invalidation can also be used to handle I-cache single error detection. When a single error is detected (when the VPU requesting instruction(s) that contains an error), the I-cache sends the corrected instruction data back to VPU but does not write the corrected instruction data back to the I-cache's memory. The R5 software handling I-cache single error detection should invalidate the cache line to cause the line to be refreshed from DRAM, which we assume is ECC protected as well and contains the correct program data.

Invalidation is also needed for VPU debug software breakpoint, which is implemented by substituting code data at selected break point with SWBRK, software breakpoint instruction. As I-cache is read-only, code change is implemented by altering the code image in external memory and invalidating the corresponding cache line.

### 4.2.4 ECC (Single-Bit-Error-Correct Double-Bit-Error-Detect)

To reduce fault rate against memory cell transient faults, the VPU I-cache is protected by single bit error correction, double bit error detection scheme.

A single-bit error within a 256-bit instruction word is corrected on the fly, and an error event is sent to the PVA top-level SEC block, and from there it is forwarded to R5 and optionally to system-level error collator.

A double-bit error within a 256-bit instruction word is detected but not corrected. An error event is sent to the PVA top-level SEC block, and from there it is forwarded to R5

and optionally to system-level error collator. The erroneous instruction word is returned to VPU, which continues to be executed.

Optionally, I-cache can be configured to suspend upon detection of double bit error, until R5 software comes in to query I-cache for the error and reset VPS. This feature may be useful during software development phase to differentiate RAM soft error from other error sources.

---

# Chapter 5. VPU Vector Memory (VMEM)

## 5.1 Overview

VPU vector memory (VMEM) houses local data memory for VPU to access so it can implement various image processing and computer vision algorithms efficiently. VMEM supports various complex memory access patterns from VPU, including consecutive read/write of various lengths, transposition, table lookup, histogram, vector addressed stores. It also supports accesses from outside-VPS hosts like DMA and R5, to allow data exchange with R5 and other system-level components.

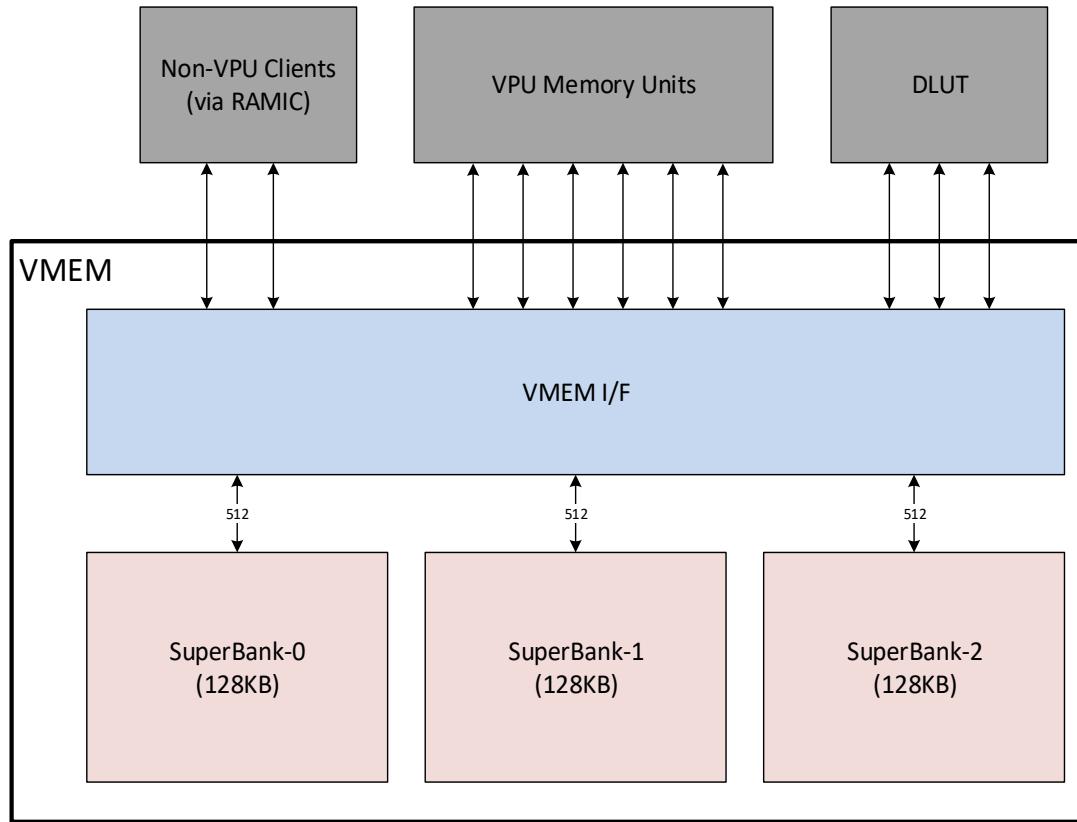

VMEM includes VMEM I/F arbitration block and three VMEM superbanks of 128KB each. Each superbanks incorporates dual port memory and supports one read AND one write per cycle. VMEM I/F arbitrates reads and writes separately for each superbanks.

The VPU vector memory block diagram is as follows.

Figure 3. VMEM block diagram

## 5.2 VMEM Interface (VMEM I/F)

The VMEM I/F block performs arbitration among VPU load/store and external requests (including DMA), and handles histogram read-modify-write requests. Memory arbitration is carried out in superbank granularity and parallel between reads and writes. We have a fixed priority scheme as follows:

Read priority (highest to lowest)

- External (including DMA) read request-high

- VPU M0 load (including table lookup and histogram read)

- VPU M1 load

- VPU M2 load

- Stream0 read (DLUT lookup)

- Stream1 read (DLUT index/config)

- External (including DMA) read request-low

Write priority (highest to lowest)

- > Histogram write

- > External (including DMA) write request-high

- > VPU M0 store

- > VPU M1 store

- > VPU M2 store

- > Stream0 write (DLUT output)

- > External (including DMA) write request-low

We have VPU load/store prioritized over stream read/write in VMEM arbitration. Stream read/write are driven by coprocessors. Normally coprocessors should have stream buffers so performance may not be affected by occasional stalls. In comparison, arbitration loss in VPU is likely to lead to performance loss.

Ideally, programmers should allocate memory objects to avoid VPU processing and coprocessor processing to compete for any superbank read/write. When that is not possible, programmers should consider coprocessor VMEM traffic and allocate memory objects to minimize VMEM contentions.

The cases when there are read(s) and write(s) in near execution packets to near address ranges in the memory are governed by memory coherency handling and are discussed separately in [Memory Coherency](#). Here we are discussing VMEM arbitration for memory read/write transactions being executed at the same clock cycle.

Multiple memory transactions at the same clock cycle and going to the same superbank are executed sequentially following the above arbitration priority, when they are all reads or all writes. Mixed read/write cases (in the same execution packet) are:

- > RW: Execute both in parallel, read will return the previous value

- > RWW: Carry out the read and the first write in parallel, then the second write. The read will return the previous value,

- > RRW: Carry out the first read, then the second read and the write in parallel. Both reads return the previous value.

A 2-bit QoS signal is sent with each external request, and the QoS is translated into a time-out count via VMEM config registers. Each external request is initially assigned to the external-low priority. If/when the request waits out the time-out count, it's escalated to the external-high priority, which prompts it to be served at next available cycle, thus ensuring some (configurable) minimal BW to VMEM for each QoS level.

The VPU supports memory accesses (table lookup, histogram, vector-addressed store, transposing load/store) that can potentially span a large address range. As each memory access is routed to a selected superbank based on the base address, no single memory access can straddle multiple superbanks.

## 5.3 VMEM Superbanks

The three memory superbanks appear as three memory regions in the VPU memory map, differentiated by high address bits to allow programmers to allocate, based on memory footprint and BW needs.

One simple way to allocate VMEM superbanks and avoid contention is

- Superbank A write = DMA

- Superbank A read = VPU

- Superbank B read/write = VPU

- Superbank C write = VPU

- Superbank C read = DMA

This allows DMA to move data from system memory to Superbank A. VPU code would read that data for processing, and can use Superbank B for intermediate outcome, and write final outcome to Superbank C. DMA would then move data from Superbank C to system memory. The DMA input and output buffers can be ping-ponged to allow simultaneous read/write by VPU and DMA, without causing any contention.

This ideal, contention-free allocation scheme is only possible when DLUT is not involved, and DMA input/output buffer as well as intermediate buffers fit the 3 superbanks respectively.

When the buffer sizing does not work out, or when DLUT is involved, one will need to allocate buffers among superbanks carefully to minimize contention among the VPU, DMA and DLUT.

Each superbank has 128KB of capacity each. Each superbank sits in 256KB of space to allow for future expansion. 1 MB is allocated for the 3 superbanks (384KB total capacity). Address aliasing in the 1 MB space is as shown in the following table.

**Table 3. VMEM address map**

| <b>Byte address</b> | <b>Memory</b>            | <b>Primary/Alias</b> |

|---------------------|--------------------------|----------------------|

| 0x00000 ~ 0x1FFFF   | Superbank A first 128KB  | Primary              |

| 0x20000 ~ 0x3FFFF   | Superbank A second 128KB | Alias                |

| 0x40000 ~ 0x5FFFF   | Superbank B first 128KB  | Primary              |

| 0x60000 ~ 0x7FFFF   | Superbank B second 128KB | Alias                |

| 0x80000 ~ 0x9FFFF   | Superbank C first 128KB  | Primary              |

| 0xA0000 ~ 0xBFFFF   | Superbank C second 128KB | Alias                |

| 0xC0000 ~ 0xDFFFF   | Superbank C third 128KB  | Alias                |

| 0xE0000 ~ 0xFFFFF   | Superbank C last 128KB   | Alias                |

**Note:** Address aliasing is a side effect of address decoder logic and should not be taken advantage of in the software, as it is possible to set up address watch point via debugger to detect out-of-valid-range memory read/write and trigger error interrupts to PVA-top Cortex R5 processor.

Future generation hardware may change physical memory sizes and memory address mapping. Best practice for VPU software is to use A/B/C memory region naming (for example, `chess_segment(A/B/C)`) instead of hard-coding memory addresses, and to avoid using the alias memory regions.

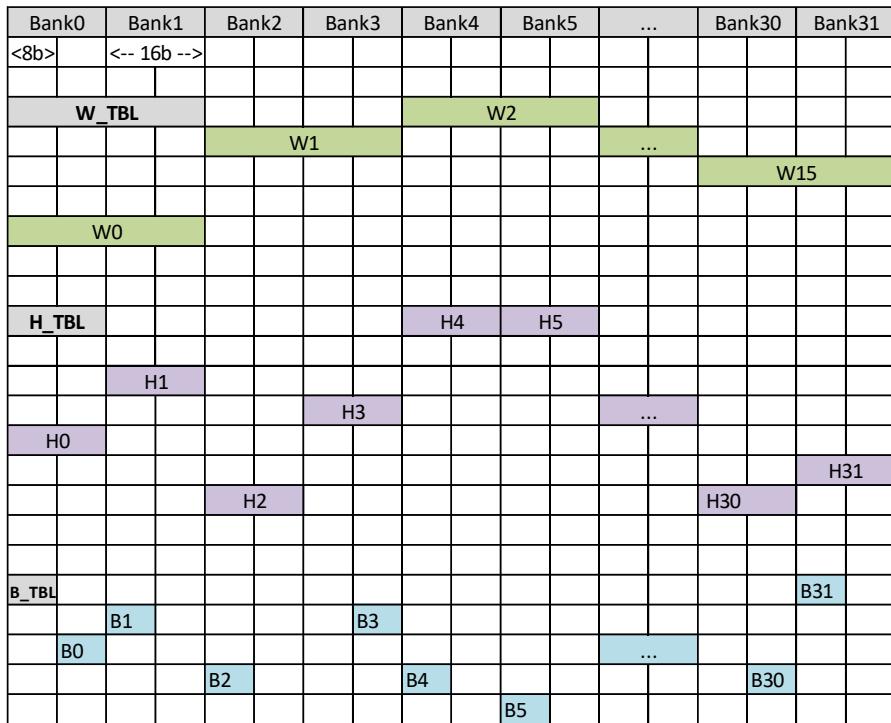

## 5.4 Memory Banking and Read/Write Access Patterns

Each VMEM superbank consists of 32 banks of 16-bit wide RAMs. Each of the 32 memory banks are independently addressable per clock cycle. This enables a rich set of access patterns:

- Read/write one byte on any byte alignment

- Read/write one 16-bit half-word on any half-word alignment

- Read/write one 32-bit word on any word alignment

- Read/write 8 or 16 consecutive 32-bit words from any half-word alignment.

- Read/write 16, 24 or 32 consecutive 16-bit half-words from any half-word alignment

- Read/write 32 consecutive 8-bit bytes from any byte alignment

- Read/write 64 consecutive 8-bit bytes from any half-word alignment (starting odd byte is not supported, and shall be forcefully aligned to an even byte)

- Read/write in various transposed addressing patterns.

- Read/write independent memory rows in each 16-bit bank, leveraged by parallel table lookup, parallel histogram, and vector addressed store.

Various transposed load/store options, parallel table lookup, histogram, and vector addressed store options are discussed later. This is just describing access patterns from VMEM hardware capability point of view.

Example access patterns are shown in the following figures.

Figure 4. VMEM access pattern examples for consecutive accesses

Figure 5. VMEM transposed access pattern examples

| Bank 0 | Bank 1    | Bank 2 | Bank 3 | Bank 4 | Bank 5 | ... | Bank 30 | Bank 31 |

|--------|-----------|--------|--------|--------|--------|-----|---------|---------|

| <8b>   | <- 16b -> |        |        |        |        |     |         |         |

|        |           |        | W0     |        |        |     |         |         |

|        |           |        |        |        | W1     |     |         |         |

|        | H0        |        |        |        |        | ... |         |         |

|        |           | H1     |        |        |        |     |         |         |

|        |           |        | H2     |        |        |     |         |         |

|        |           |        |        | H3     |        |     |         |         |

|        |           |        |        |        | H4     |     |         |         |

|        |           |        |        |        |        | ... |         |         |

|        |           |        |        |        |        |     | H29     |         |

|        |           |        |        |        |        |     |         | H30     |

|        | B0        |        |        |        |        |     |         |         |

|        |           | B1     |        |        |        |     |         |         |

|        |           |        | B2     |        |        |     |         |         |

|        |           |        |        | B3     |        |     |         |         |

|        |           |        |        |        | B4     |     |         |         |

|        |           |        |        |        |        | ... |         |         |

|        |           |        |        |        |        |     | B29     |         |

|        |           |        |        |        |        |     |         | B30     |

|        | B31       |        |        |        |        |     |         |         |

Figure 6. VMEM access pattern examples for parallel table lookup and histogram

## 5.5 Load Data Cache

Each VMEM memory bank contains a load data cache for power reduction. VPU processor pipeline including load timing accommodate both cache-hit and cache-miss cases. The cache can be enabled or disabled (see 9.6.16 for details) on a superbank granularity.

The load cache, when enabled, only caches the following types of memory read transactions:

- Single/double vector load of 32-byte or 64-byte consecutive data

The following types of memory read transactions are ignored by the load cache:

- Single vector WX-type load (48-byte transaction)

- Single/double vector S (scalar) and C2 (circulating 2 items) distributions

- Scalar register loads

- Lookups

- DMA reading VMEM

- DLUT reading VMEM

When enabled, the load cache monitors ALL memory transactions to invalidate cache entries when there's a hit, including

- Scalar/vector stores

- Histogram/VAST operations

- DMA writing VMEM

- DLUT writing VMEM

When cache is enabled and cache hit occurs, load data is retrieved from the cache and memory read transaction is not issued, saving some power. When the cache is enabled and a cache miss occurs, there is no performance penalty, but there is a small power penalty. Thus, enable/disable control is exposed to the programmer for power optimization. Load data cache should be enabled when there are repeated accesses to small localities, like in the case of filtering, and should otherwise be disabled.

## 5.6 Memory Allocation among VMEM Superbanks

VPU application code may use storage specifiers {DMb, RAM\_Ab, RAM\_Bb, RAM\_Cb}, together with chess\_segment(A/B/C) and optional alignment constraint to allocate scalar or array variables onto specific superbank.

Using RAM\_Ab, RAM\_Bb, RAM\_Cb with chess\_segment(A/B/C) causes the linker to allocate variable to superbank A, B, or C, respectively

**Example 1:**

```

short chess_storage(RAM_Ab % 512: chess_segment(A)) foo[256];

```

This allocates foo as a 256-element short array on superbank A with 512-byte alignment.

**Example 2:**

```

char chess_storage(RAM_Bb % 512: chess_segment(B)) bar[256];

```

This allocates bar as a 256-element char array on superbank B with 512-byte alignment.

**Example 3:**

```

int chess_storage(DMb % 4) more_foo[256];

```

Using DMb storage specifier causes the linker to allocate such variables to superbank A first, followed by B, then C, where it fits. Reserved regions between superbanks are skipped automatically. This allocates more\_foo as a 256-element int array with 4-byte alignment in one of the superbanks.

**Example 4:**

```

int more_bar[128];

```

Not using any storage specifier causes the linker to allocate the variable to global memory (\_global segment in BCF file). Application project can supply a custom BCF file to place \_global segment in a valid memory range. Otherwise, the default BCF file applies and places \_global segment in superbank A.

---

# Chapter 6. VPU Instruction Set Architecture

## 6.1 Processor Architecture

### 6.1.1 Key Features

The VPU instruction set architecture has the following key features:

- VLIW and Wide SIMD vector processor, with multiple operations and multiple load/store slots.

- Multi-dimension address generation (6 dimensions).

- Multiple levels of zero-overhead hardware looping (2 levels).

- Instruction-level predication of certain vector operation, scalar load/store, vector load.

- Lane predication for vector store.

- Loop collapsing to reduce overhead across data block and filter kernel dimension, enabled by address generation and predication.

- Reduced code size and library construction effort for filtering and other windowing operations, enabled by zero-overhead nested looping through loop collapsing.

- Memory banking and parallel lookup, histogram, and vector addressed store.

- Memory bank address calculation to implement transposed vector load/store for various transposition options.

- Circular buffer addressing for memory-copy-free data/compute reuse.

- Rich set of load and store data distribution patterns.

- Vector load with permutation of loaded data.

- Vector-lane predication of selected store operations.

- Protected pipeline with sequential execution (except branch delay slots) and hardware dependency stalling.

The VPU instructions are scheduled in the following 7-way VLIW format. Each instruction word is 32-bit long, and up to 7 instruction words can be executed together as an execution packet.

**Table 4. VLIW instruction format**

| S0                                                                | S1               | V0               | V1               | M0                                                                       | M1                           | M2                           |

|-------------------------------------------------------------------|------------------|------------------|------------------|--------------------------------------------------------------------------|------------------------------|------------------------------|

| Scalar operation or Control (branch, call, return, SW breakpoint) | Scalar operation | Vector operation | Vector operation | Load/store, scalar or vector, lookup, histogram, vector-addressed stores | Load/store, scalar or vector | Load/store, scalar or vector |

Variable-length packet encoding is supported, so that NOP (no operation) instructions are skipped and not taking up any code space. There is an exception though. Compiler may insert NOPs intentionally to align branch target, beginning of function, etc., execution packets to reduce branch penalty.

In general, control instructions are available only in S0 slot. Scalar operations are available in both scalar slots. Vector operations are available in both vector slots. Memory operations are available in all 3 memory slots, except lookup, histogram, and vector-addressed store are available only in M0. Additional details:

- Agen save/restore instructions are available only in M0 slot.

- Quad-vector store instructions are available only in M0 slot.

- Per-lane predicated store instructions via vector register file are available only in M0 slot.

- Per-lane rounding store (double vector only) instructions are available only in M0 slot.

## 6.1.2 Program and Data Memory Spaces

Program memory space is 32-bit byte address, with valid range [0 , 2<sup>32</sup> – 4], as instruction words are 32-bit each.

Data memory space is 20-bit byte address that spans 1MB, but only valid inside each of three 128KB superbanks, for a total of 384KB of physical memory. Please see [VMEM Overview](#) for the memory map.