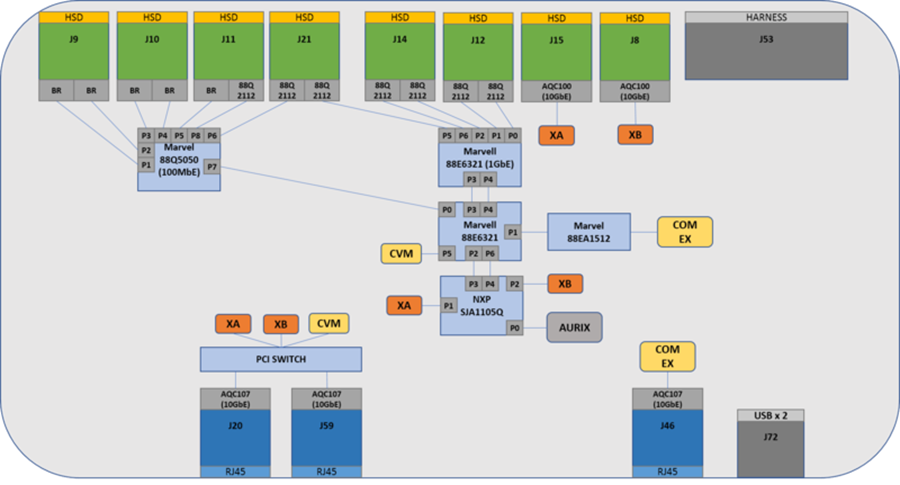

Ethernet 100M/1G Networking

This section explains the 100M/1G networking architecture/topology of DRIVE development platforms, along with all the use case specific configurations enabled for VLAN, PTP etc. and known limitations, if any.:

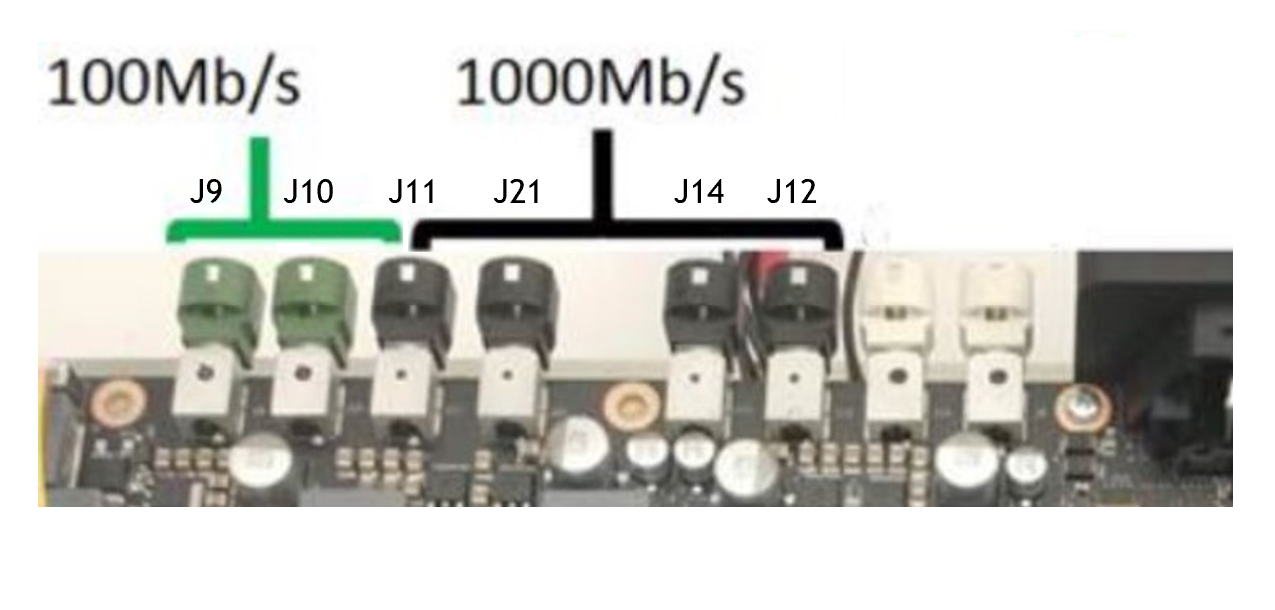

There are 12 total channels (100M/1G) that are exposed through 6 HSD ports as follows (i.e., 2 channels per port).

Ports are color coded based on the speed supported.

• Green ports = 100 Mbps channels

• Black ports = 1 Gbps channels

Note: | The one exception: Channel A of J11 only supports 100 Mbps. |

Network Configuration

DRIVE OS development platform support following networking configurations:

• PDK Standard configuration (default)

• HYPERION_7_DDPX

• HYPERION_8_PROTO

Configuration selection is enabled via AURIX MCU AUTOSAR firmware commands. Commands details are as below:

gethyperionconfig : Get the current network config info

sethyperionconfig <config value>: Sets network config for next MCU boot

Where:

Configuration | Value |

Standard/Non Hyperion | 0 |

HYPERION_7_DDPX | 1 |

HYPERION_8_PROTO | 2 |

Example

1. To set the configuration to standard configuration, run:

sethyperionconfig 0

aurixrest

2. To set the configuration to Hyperion 7 configuration, run:

sethyperionconfig 1

aurixrest

3. To set the configuration to Hyperion 8 configuration, run:

sethyperionconfig 2

aurixrest

4. To get the current configuration:

gethyperionconfig

Standard Network Configuration

HSD Port | Color | Channel | Port Role | Speed Supported | Board setup->Setting UP 3550 Platform->Front panel port mapping |

J9 | Green | Channel A | Secondary | 100 Mbps | 802.3bw 100Mbps channel 1 |

Channel B | Secondary | 100 Mbps | 802.3bw 100Mbps channel 2 | ||

J10 | Green | Channel A | Secondary | 100 Mbps | 802.3bw 100Mbps channel 3 |

Channel B | Secondary | 100 Mbps | 802.3bw 100Mbps channel 4 | ||

J11 | Black | Channel A | Secondary | 100 Mbps | 802.3bw 100Mbps channel 5 |

Channel B | Secondary | 1 Gbps | 802.3bp 1Gbps channel 7 | ||

J21 | Black | Channel A | Secondary | 1 Gbps | 802.3bp 1Gbps channel 6 |

Channel B | Secondary | 1 Gbps | 802.3bp 1Gbps channel 5 | ||

J14 | Black | Channel A | Secondary | 1 Gbps | 802.3bp 1Gbps channel 4 |

Channel B | Secondary | 1 Gbps | 802.3bp 1Gbps channel 3 | ||

J12 | Black | Channel A | Secondary | 1 Gbps | 802.3bp 1Gbps channel 2 |

Channel B | Secondary | 1 Gbps | 802.3bp 1Gbps channel 1 |

Hyperion 7 Network Configuration

HSD Port | Color | Channel | Port Role | Speed Supported | L2 switch forwarding restriction to external ports (if any) | Board setup->Setting UP 3550 Platform->Front panel port mapping |

J9 | Green | Channel A | Primary | 100 Mbps | L2 routing restricted to all other external ports | 802.3bw 100Mbps channel 1 |

Channel B | Primary | 100 Mbps | L2 routing restricted to all other external ports | 802.3bw 100Mbps channel 2 | ||

J10 | Green | Channel A | Primary | 100 Mbps | L2 routing restricted to all other external ports | 802.3bw 100Mbps channel 3 |

Channel B | Primary | 100 Mbps | L2 routing restricted to all other external ports | 802.3bw 100Mbps channel 4 | ||

J11 | Black | Channel A | Primary | 100 Mbps | L2 routing restricted to all other external ports | 802.3bw 100Mbps channel 5 |

Channel B | Primary | 100 Mbps | L2 routing restricted to all other external ports | 802.3bp 1Gbps channel 7 | ||

J21 | Black | Channel A | Primary | 100 Mbps | L2 routing restricted to all other external ports | 802.3bp 1Gbps channel 6 |

Channel B | Primary | 100 Mbps | L2 routing restricted to all other external ports | 802.3bp 1Gbps channel 5 | ||

J14 | Black | Channel A | Secondary | 1 Gbps | L2 routing restricted to all other external ports except J14 link 3 (J14 Channel B) | 802.3bp 1Gbps channel 4 |

Channel B | Secondary | 1 Gbps | L2 routing restricted to all other external ports except J14 link 4 (J14 Channel A) | 802.3bp 1Gbps channel 3 | ||

J12 | Black | Channel A | Primary | 100 Mbps | L2 routing restricted to all other external ports | 802.3bp 1Gbps channel 2 |

Channel B | Primary | 100 Mbps | L2 routing restricted to all other external ports | 802.3bp 1Gbps channel 1 |

Hyperion 8 Network Configuration

HSD Port | Color | Channel | Port Role | Speed Supported | L2 switch forwarding restriction to external ports (if any) | Board setup->Setting UP 3550 Platform->Front panel port mapping |

J9 | Green | Channel A | Primary | 100 Mbps | L2 routing restricted to all other external ports | 802.3bw 100Mbps channel 1 |

Channel B | Primary | 100 Mbps | L2 routing restricted to all other external ports | 802.3bw 100Mbps channel 2 | ||

J10 | Green | Channel A | Primary | 100 Mbps | L2 routing restricted to all other external ports | 802.3bw 100Mbps channel 3 |

Channel B | Primary | 100 Mbps | L2 routing restricted to all other external ports | 802.3bw 100Mbps channel 4 | ||

J11 | Black | Channel A | Primary | 100 Mbps | L2 routing restricted to all other external ports | 802.3bw 100Mbps channel 5 |

Channel B | Primary | 100 Mbps | L2 routing restricted to all other external ports | 802.3bp 1Gbps channel 7 | ||

J21 | Black | Channel A | Primary | 100 Mbps | L2 routing restricted to all other external ports | 802.3bp 1Gbps channel 6 |

Channel B | Primary | 1 Gbps | L2 routing restricted to all other external ports | 802.3bp 1Gbps channel 5 | ||

J14 | Black | Channel A | Secondary | 1 Gbps | L2 routing restricted to all other external ports | 802.3bp 1Gbps channel 4 |

Channel B | Primary | 1 Gbps | L2 routing restricted to all other external ports | 802.3bp 1Gbps channel 3 | ||

J12 | Black | Channel A | Primary | 1 Gbps | L2 routing restricted to all other external ports | 802.3bp 1Gbps channel 2 |

Channel B | Primary | 1 Gbps | L2 routing restricted to all other external ports | 802.3bp 1Gbps channel 1 |

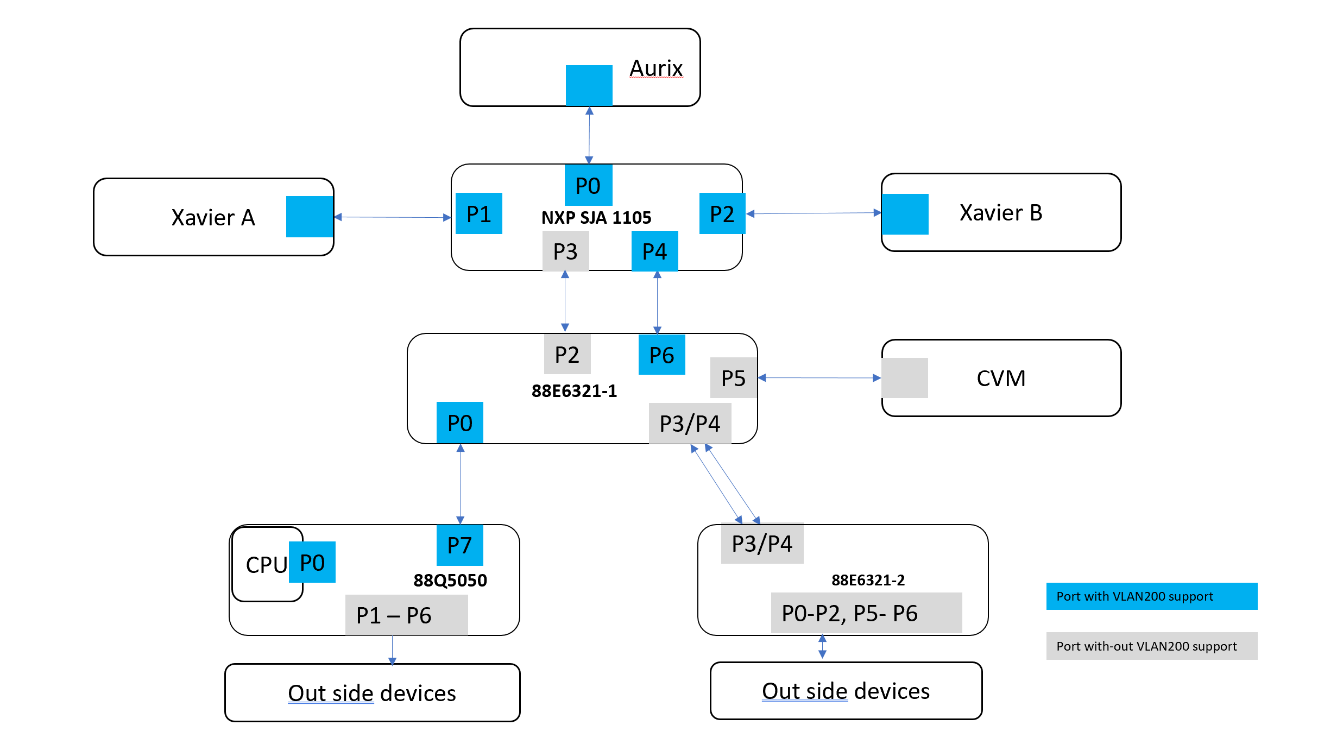

VLAN Configurations

VLAN 200 (TACP networking) is enabled in Xavier A, Xavier B, CVM, NXP SJA1105Q switch, and Marvell 88EA6321 switch. When enabled:

• Provides a secure channel between multiple SoCs/VMs and between the SoC and MCU (AURIX).

• Makes safety MCU (AURIX) inaccessible from the outside.

• Used for MCU communication, including cameras, firmware updates, etc.

• Used for firmware update of 88Q5050 switch from Xavier A.

PTP Support

All the networking nodes of the DRIVE OS development platform are made time-aware systems/nodes i.e., all the CPU nodes such as Xavier and Aurix (MCU) act as time-aware end-stations and all the switches act as time-aware bridges.

DRIVE OS development platforms have a total of three (3) different models of Ethernet switches connected on board from two different vendors:

• NXP SJA1105Q switch.

• 88EA6321 switch (multi instance)

• Marvell 88Q5050 switch

Marvell 88Q5050 has its own internal MCU and firmware capable of handling the PTP locally inside switch. Hence, 88Q5050 is made time-aware bridge by enabling the PTP support in its firmware. Both NXP SJA1105Q and Marvell 6321 switches do not have internal CPU and firmware for PTP handling. Therefore, AURIX MCU is used for remote PTP handling of these switches.

The AURIX MCU side switch PTP implementation is based on 802.1AS PTP profile, while 88Q5050 firmware supports AVNU AutoCDS v1.4 profile. Due to intermixing of the PTP protocol profile, all ports coming out of 6321-2 switch supports 802.1AS profile and all the ports coming out from 88Q5050 supports AVNU AutoCDS v1.4 profile.

Prerequisites

Pegasus boards must be flashed with the latest Marvell 88Q5050 switch firmware version and AURIX firmware version to use this PTP solution.

• Aurix MCU firmware version: >= 5.2.3

• 5050 Firmware version: >= 2.07.1001.07

Note: | Any other combination of AURIX MCU firmware version and Marvell 88Q5050 switch firmware version is not a supported configuration for AGX PTP. |

How to verify the firmware version

• AURIX MCU firmware: Using version command on AURIX MCU console.

• Marvell 88Q5050 switch firmware version: Refer to section Marvell 88Q5050 Firmware Management.

PTP Limitations

• No BMCA on ANVU AutoCDS 1.4 protocol supporting ports as per protocol compliance.

• No BMCA handling in switch/bridge PTP implementation. The implementation only supports E2E announce packet forwarding.

• No signaling support in switch/bridge PTP implementation.

• No PTP over VLAN support as per 802.1AS protocol.

• Limitation per port PTP message handling:

• Maximum one peer delay message per second from each PTP secondary devices on external/internal nodes.

• Maximum of eight (8) number of syncs and follow-up messages per second from primary reference clock.

• Maximum announce interval.

Compatibility Recommendation for Devices on External Ports

• "neighborPropDelayThresh" value must be increased up to 12 microseconds on secondary devices if it connects through HSD-RJ45 dongle.

• Signaling message support must be disabled on external devices.

• External devices must restrict the message frequency as per limitation given in the Limitations section above.

Standard PTP Port Roles of External Ports

HSD Port | Color | Channel | Port Role | Protocol Support | PTP device allowed to connect to this port (Role/Protocol) |

J9 | Green | Channel A | Primary | AVNU AutoCDS v1.4 | Secondary/AVNU AutoCDS v1.4 |

Channel B | Primary | AVNU AutoCDS v1.4 | Secondary/AVNU AutoCDS v1.4 | ||

J10 | Green | Channel A | Primary | AVNU AutoCDS v1.4 | Secondary/AVNU AutoCDS v1.4 |

Channel B | Primary | AVNU AutoCDS v1.4 | Secondary/AVNU AutoCDS v1.4 | ||

J11 | Black | Channel A | Primary | AVNU AutoCDS v1.4 | Secondary/AVNU AutoCDS v1.4 |

Channel B | Primary | AVNU AutoCDS v1.4 | Secondary/AVNU AutoCDS v1.4 | ||

J21 | Black | Channel A | Primary | AVNU AutoCDS v1.4 | Secondary/AVNU AutoCDS v1.4 |

Channel B | Transparent | 802.1-AS | Primary & Secondary/802.1-AS | ||

J14 | Black | Channel A | Transparent | 802.1-AS | Primary & Secondary/802.1-AS |

Channel B | Transparent | 802.1-AS | Primary & Secondary/802.1-AS | ||

J12 | Black | Channel A | Transparent | 802.1-AS | Primary & Secondary/802.1-AS |

Channel B | Transparent | 802.1-AS | Primary & Secondary/802.1-AS |

Hyperion 7 PTP Port Roles of External Ports

HSD Port | Color | Channel | Port Role | Protocol Support | PTP device allowed to connect to this port (Role/Protocol) |

J9 | Green | Channel A | Primary | AVNU AutoCDS v1.4 | Secondary/AVNU AutoCDS v1.4 |

Channel B | Primary | AVNU AutoCDS v1.4 | Secondary/AVNU AutoCDS v1.4 | ||

J10 | Green | Channel A | Primary | AVNU AutoCDS v1.4 | Secondary/AVNU AutoCDS v1.4 |

Channel B | Primary | AVNU AutoCDS v1.4 | Secondary/AVNU AutoCDS v1.4 | ||

J11 | Black | Channel A | Primary | AVNU AutoCDS v1.4 | Secondary/AVNU AutoCDS v1.4 |

Channel B | Primary | AVNU AutoCDS v1.4 | Secondary/AVNU AutoCDS v1.4 | ||

J21 | Black | Channel A | Primary | AVNU AutoCDS v1.4 | Secondary/AVNU AutoCDS v1.4 |

Channel B | Primary | 802.1-AS | Secondary/802.1-AS | ||

J14 | Black | Channel A | Transparent | 802.1-AS | Primary & Secondary/802.1-AS |

Channel B | Transparent | 802.1-AS | Primary & Secondary/802.1-AS | ||

J12 | Black | Channel A | Primary | 802.1-AS | Secondary/802.1-AS |

Channel B | Primary | 802.1-AS | Secondary/802.1-AS |

Hyperion 8 PTP Port Roles of External Ports

HSD Port | Color | Channel | Port Role | Protocol Support | PTP device allowed to connect to this port (Role/Protocol) |

J9 | Green | Channel A | Primary | AVNU AutoCDS v1.4 | Secondary/AVNU AutoCDS v1.4 |

Channel B | Primary | AVNU AutoCDS v1.4 | Secondary/AVNU AutoCDS v1.4 | ||

J10 | Green | Channel A | Primary | AVNU AutoCDS v1.4 | Secondary/AVNU AutoCDS v1.4 |

Channel B | Primary | AVNU AutoCDS v1.4 | Secondary/AVNU AutoCDS v1.4 | ||

J11 | Black | Channel A | Primary | AVNU AutoCDS v1.4 | Secondary/AVNU AutoCDS v1.4 |

Channel B | Primary | AVNU AutoCDS v1.4 | Secondary/AVNU AutoCDS v1.4 | ||

J21 | Black | Channel A | Primary | AVNU AutoCDS v1.4 | Secondary/AVNU AutoCDS v1.4 |

Channel B | Primary | 802.1-AS | Secondary/802.1-AS | ||

J14 | Black | Channel A | Transparent | 802.1-AS | Primary & Secondary/802.1-AS |

Channel B | Primary | 802.1-AS | Secondary/802.1-AS | ||

J12 | Black | Channel A | Primary | 802.1-AS | Secondary/802.1-AS |

Channel B | Primary | 802.1-AS | Secondary/802.1-AS |

All Xavier side PTP related binaries are available at:

/home/nvidia/drive-t186ref-linux/samples/nvavb/daemons

Supported PTP Configurations and Commands

This section describes the PTP support for 802.1AS & AVNU AutoCDS v1.4 conforming time synchronization messages for hardware time synchronization in the following configuration.

Single Pegasus time synchronization: Aurix MCU as Primary reference clock (GM)

• Single Pegasus: Xavier as primary reference clock (GM)

• Single Pegasus: External device as primary reference clock (GM)

• Dual Pegasus: Using standard network configuration

• Dual Pegasus: Using Hyperion 8 proto configuration

Single Pegasus Time Synchronization: AURIX MCU as Primary Reference Clock (GM)

AURIX (as GM)

1. In the AURIX console, enter the date in UNIX-style seconds.

For example:

date 0x77DA7A8F

2. Enable gPTP on AURIX:

gptpon

Linux (as Secondary)

Disable NTP on both Xaviers. The following command disables NTP, which is persistent across reboots.

timedatectl set-ntp 0

On both the Xavier A and Xavier B consoles, enter the following commands:

./phc2sys -s /dev/ptp0 -w -S 1.0 -O 0 &

./ptp4l -f ./gPTP_slave.cfg -p /dev/ptp0 -i eth0 -m

Single Pegasus: Xavier as Primary Reference Clock (GM)

gPTP based time sync between on board nodes XA, XB, CVM, and external devices.

1. Disable NTP on both Xaviers. The following command disables NTP, which is persistent across reboots.

timedatectl set-ntp 0

2. On the Primary Xavier run following commands.

./phc2sys -s /dev/ptp0 -w -S 1.0 -O 0 &

./ptp4l -f ./gPTP.cfg -p /dev/ptp0 -i eth0 -m

3. On the Secondary Xavier run following commands.

./phc2sys -s /dev/ptp0 -w -S 1.0 -O 0 &

./ptp4l -f ./gPTP_slave.cfg -p /dev/ptp0 -i eth0 -m

Single Pegasus: Xavier as Primary Reference Clock (GM)

gPTP based time sync between on board nodes XA, XB ,CVM and external GM device.

The external GM must be connected to one of the ports that has a transparent PTP role.

1. Disable NTP on both Xaviers. The following command disables NTP, which is persistent across reboots.

timedatectl set-ntp 0

2. On all Xaviers run following commands.

./phc2sys -s /dev/ptp0 -w -S 1.0 -O 0 &

./ptp4l -f ./gPTP_slave.cfg -p /dev/ptp0 -i eth0 -m

Dual Pegasus: Using Standard Network Configuration

gPTP based time sync between nodes (XA, XB and external devices) of two (2_ Pegasus connected back to back.

Setup Info

Pegasus-1 1000 Base-T1 HSD connector (J14/J12/J21 CH-B ) <----> E3579/E3580 HSD | E3579/E3580 R45 <-------> E3579/E3580 RJ45 | E3579/E3580 HSD <------> Pegasus-2 1000 Base-T1 HSD connector (J14/J12/J21 CH-B)

1. Disable NTP on both Xaviers. The following command disables NTP, which is persistent across reboots.

timedatectl set-ntp 0

2. On the Primary Xavier run the following commands.

./phc2sys -s /dev/ptp0 -w -S 1.0 -O 0 &

./ptp4l -f ./gPTP.cfg -p /dev/ptp0 -i eth0 -m

3. On the Secondary Xavier run following commands.

./phc2sys -s /dev/ptp0 -w -S 1.0 -O 0 &

./ptp4l -f ./gPTP_slave.cfg -p /dev/ptp0 -i eth0 -m

Dual Pegasus: Using Hyperion 8 Proto Configuration

gPTP based time sync between nodes (XA, XB and external devices) of two (2) Pegasus connected back to back.

Setup Info

Pegasus-1 1000 Base-T1 HSD connector (J14 CH-A ) <----> E3579/E3580 HSD | E3579/E3580 R45 <-------> E3579/E3580 RJ45 | E3579/E3580 HSD <------> Pegasus-2 1000 Base-T1 HSD connector (J14 CH-A)

1. Disable NTP on both Xaviers. The following command disables NTP, which is persistent across reboots.

timedatectl set-ntp 0

2. On the Primary Xavier run the following commands.

./phc2sys -s /dev/ptp0 -w -S 1.0 -O 0 &

./ptp4l -f ./gPTP.cfg -p /dev/ptp0 -i eth0 -m

3. On theSecondary Xavier run the following commands.

./phc2sys -s /dev/ptp0 -w -S 1.0 -O 0 &

./ptp4l -f ./gPTP_slave.cfg -p /dev/ptp0 -i eth0 -m

Marvell 88Q5050 Firmware Management

DRIVE OS development supports two flavors of Marvell 88Q5050 firmware packaged in SDK:

Version | File Name | Function Supported | AURIX Firmware Compatibility for PTP Support | Description |

2.07.1001.07 | 88Q5050_flash.v2.07.1001.07.bin | Basic switch+ PTP(AVNU CDS) | > = 5.2.3 | DDPX PTP with all bridges/switches as time aware system |

2.07.1001.06 | 88Q5050_flash.v2.07.1001.06.bin | Basic | < 5.2.3 | DDPX PTP with bridges/switches in pass-through mode |

Note: | The purpose of release non PTP firmware is to allow PTP in pass-through mode for backward compatibility mode, if required. All other combinations (apart from table) is not supported. |

Marvell 88Q5050 Firmware Update from Xavier over Ethernet

It is possible to update the Marvell 88Q5050 firmware from Xavier through the update_firmware.sh script packaged in the file system.

Silent feature of update process/framework is as below:

• Automatic upgrade is by default enabled for latest packaged firmware via boot-up service/script from the root file system.

• Manual force upgrade is also possible via script.

• Provision to get the current flashed firmware is also possible via script.

Prerequisites

Either AURIX MCU is flashed with firmware version >= 5.2.3

-OR-

AURIX MCU is flashed with firmware version < 5.2.3 and no external network connected via external ports.

Manually Upgrading or Degrading the Firmware

To manually upgrade or degrade the firmware:

/lib/firmware/marvell_ethernet/tools/linux/nvidia/update-firmware.sh --useversion 88Q5050_flash.v2.07.1001.<xx>.bin

Where <xx> is the config version. Refer to the table above for more information.

Note: | The command above must be followed by an aurixreset AURIX MCU reset on the MCU console to make 88Q5050 boot with newly flashed firmware. |

To print the currently flashed version:

/lib/firmware/marvell_ethernet/tools/linux/nvidia/update-firmware.sh --printversion

Note: | When AURIX MCU is flashed with firmware version <= 5.2.3, the commands may fail. The workaround for this issue is to remove all external network connection via external ports and to change the value of ETH_INTERFACE to eth0 from eth0.200 in the E3550_Q5050.cfg file before retrying. Changing values of any other flags in E3550_Q5050.cfg may lead to OTA failure and is not recommended. Manual running of update-firmware.sh script is only restricted to options specified in this document. |

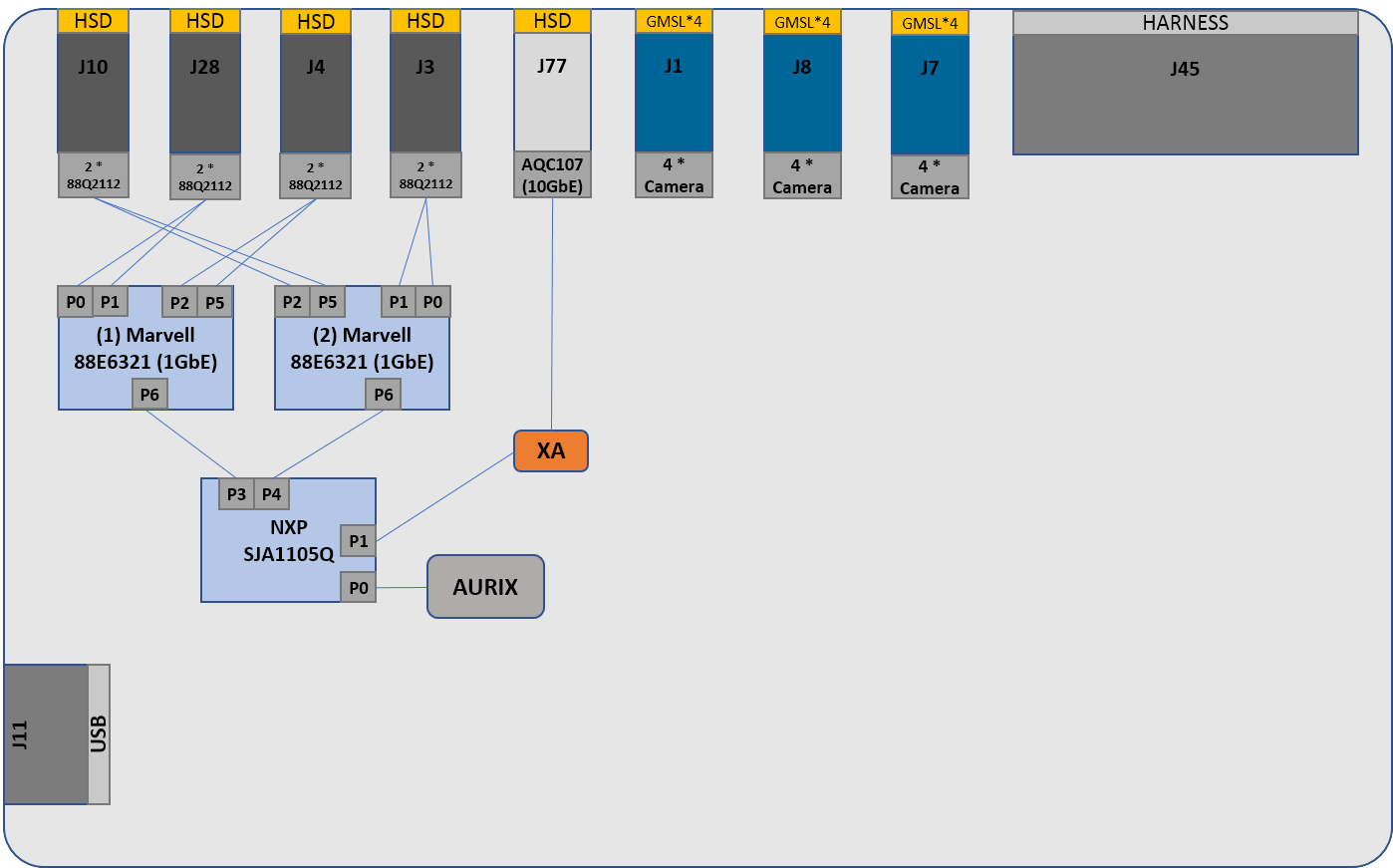

P3479

This section explains 1G networking architecture/topology of the P3479 board.

Port Roles

HSD Port | Color | Channel | 100/1000 Base T1 Primary/Secondary | Speed Supported |

J10 | Black | Channel A | Secondary | 1 Gbps |

Channel B | Secondary | 1 Gbps | ||

J28 | Black | Channel A | Secondary | 1 Gbps |

Channel B | Secondary | 1 Gbps | ||

J4 | Black | Channel A | Secondary | 1 Gbps |

Channel B | Secondary | 1 Gbps | ||

J3 | Black | Channel A | Secondary | 1 Gbps |

Channel B | Secondary | 1 Gbps |