|

|

NVIDIA DRIVE OS Linux API Reference5.1.0.2 Release |

|

|

NVIDIA DRIVE OS Linux API Reference5.1.0.2 Release |

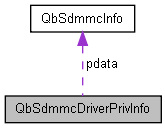

Holds the context structure for the SDMMC driver.

A pointer to this structure is passed into the driver's Init() routine. This pointer is the only data that can be kept in a global variable for later reference.

Data Fields | |

| NvBool | IsEsd |

| Defines whether the driver is for an ESD card (vs eMMC). More... | |

| NvU8 | BlockSizeLog2 |

| Holds the block size. More... | |

| NvU8 | PageSizeLog2 |

| Holds the page size. More... | |

| NvU8 | PagesPerBlockLog2 |

| Holds the number of pages per block. More... | |

| NvU32 | CardRca |

| Holds the card's Relative Card Address. More... | |

| NvU32 | SdmmcResponse [NVBOOT_SDMMC_RESPONSE_BUFFER_SIZE_IN_BYTES/sizeof(NvU32)] |

| Holds a response buffer. More... | |

| QbDeviceStatus | DeviceStatus |

| Holds the device status. More... | |

| NvU32 | XferStartTime |

| Holds the Movi Nand Read/Write start time. More... | |

| NvBool | HighSpeedMode |

| Defines whether to access the card in high speed mode. More... | |

| NvBool | EnhancedStrobeMode |

| Defines whether to access the card in HS400 ESM. More... | |

| NvBool | IsHighCapacityCard |

| Defines whether the card is a high capacity card. More... | |

| NvU8 | SpecVersion |

| Holds the spec version. More... | |

| NvU8 | ExtCsdSpecVersion |

| Holds the ExtCsdSpecVersion. More... | |

| NvU32 | EmmcBootPartitionSize |

| Holds Emmc Boot Partition size. More... | |

| SdmmcAccessRegion | CurrentAccessRegion |

| Holds the current access region. More... | |

| NvBootSdmmcCardClock | CurrentClockRate |

| Holds the current clock rate. More... | |

| NvU8 | SdmmcInternalBuffer [NVBOOT_SDMMC_ECSD_BUFFER_SIZE_IN_BYTES] |

| Defines a buffer for selecting high speed, reading extended CSD and SCR. More... | |

| NvU8 | taac |

| Defines read access time1. More... | |

| NvU8 | nsac |

| Defines read access time2. More... | |

| NvU8 | TranSpeed |

| Defines the clock frequency when not in high speed mode. More... | |

| NvU8 | TranSpeedInMHz |

| Defines the transfer speed in MHz. More... | |

| NvBool | HostSupportsHighSpeedMode |

| Defines whether the host supports high speed mode. More... | |

| NvBool | CardSupportsHighSpeedMode |

| Defines whether the card supports high speed mode. More... | |

| NvU8 | PageSizeLog2ForCapacity |

| Holds the page size to use for card capacity calculation. More... | |

| NvU8 | PowerClass26MHz360V |

| Holds the power class for 26MHz at 3.6V. More... | |

| NvU8 | PowerClass52MHz360V |

| Holds the power class for 52MHz at 3.6V. More... | |

| NvU8 | PowerClass26MHz195V |

| Holds the power class for 26MHz at 1.95V. More... | |

| NvU8 | PowerClass52MHz195V |

| Holds the power class for 52MHz at 1.95V. More... | |

| NvU8 | BootConfig |

| Holds the boot config from ExtCSD. More... | |

| NvBool | IsHighVoltageRange |

| Defines whether high voltage range is used for card identification. More... | |

| NvU8 | MaxPowerClassSupported |

| Holds the Max Power class supported by target board. More... | |

| NvU32 | NumOfBlocks |

| Holds the number of blocks present in card. More... | |

| NvU32 | XferTimeOutInUs |

| Holds read/write time out at current card clock frequency. More... | |

| NvU8 | SdmmcBootModeBuffer [NVBOOT_SDMMC_BOOT_MODE_BUFFER_SIZE_IN_BYTES] |

| Holds data read in boot mode. More... | |

| NvBool | BootModeReadInProgress |

| Defines whether you are reading in boot mode. More... | |

| NvU8 | CardSupportSpeed |

| Flag to indicate the card speed and operating voltage level. More... | |

| NvU8 | PowerClass52MHzDdr360V |

| Power class for 52 Mhz DDR @ 3.6V. More... | |

| NvU8 | PowerClass52MHzDdr195V |

| Power class for 52 Mhz DDR @ 1.95V. More... | |

| NvU8 | PowerClass200MHzDdr180V |

| Power class for 200 Mhz DDR @ 3.6V. More... | |

| NvU8 | IsDdrMode |

| Indicates whether Ddr mode is used for data transfer. More... | |

| NvBool | IsPLLP |

| Indicates whether Parent clock source is PLLP or PLLC4. More... | |

| NvU32 | RegPhyBase |

| NvU32 | RegLen |

| NvU32 | RegVirtBase |

| QbSdmmcInfo * | pdata |

| NvU32 | VendorClockCtrl |

| SdmmcInitLevel | SdmmcInitType |

| NvBool | DisableHS400 |

| NvBool | IsCardReady |

| NvBool | Support64BitDmaAddr |

| NvU8 QbSdmmcDriverPrivInfo::BlockSizeLog2 |

| NvU8 QbSdmmcDriverPrivInfo::BootConfig |

| NvBool QbSdmmcDriverPrivInfo::BootModeReadInProgress |

| NvU32 QbSdmmcDriverPrivInfo::CardRca |

| NvBool QbSdmmcDriverPrivInfo::CardSupportsHighSpeedMode |

| NvU8 QbSdmmcDriverPrivInfo::CardSupportSpeed |

| SdmmcAccessRegion QbSdmmcDriverPrivInfo::CurrentAccessRegion |

| NvBootSdmmcCardClock QbSdmmcDriverPrivInfo::CurrentClockRate |

| QbDeviceStatus QbSdmmcDriverPrivInfo::DeviceStatus |

| NvU32 QbSdmmcDriverPrivInfo::EmmcBootPartitionSize |

| NvBool QbSdmmcDriverPrivInfo::EnhancedStrobeMode |

| NvU8 QbSdmmcDriverPrivInfo::ExtCsdSpecVersion |

| NvBool QbSdmmcDriverPrivInfo::HighSpeedMode |

| NvBool QbSdmmcDriverPrivInfo::HostSupportsHighSpeedMode |

| NvU8 QbSdmmcDriverPrivInfo::IsDdrMode |

| NvBool QbSdmmcDriverPrivInfo::IsEsd |

| NvBool QbSdmmcDriverPrivInfo::IsHighCapacityCard |

| NvBool QbSdmmcDriverPrivInfo::IsHighVoltageRange |

| NvBool QbSdmmcDriverPrivInfo::IsPLLP |

| NvU8 QbSdmmcDriverPrivInfo::MaxPowerClassSupported |

| NvU32 QbSdmmcDriverPrivInfo::NumOfBlocks |

| NvU8 QbSdmmcDriverPrivInfo::PageSizeLog2 |

| NvU8 QbSdmmcDriverPrivInfo::PageSizeLog2ForCapacity |

| NvU8 QbSdmmcDriverPrivInfo::PagesPerBlockLog2 |

| QbSdmmcInfo* QbSdmmcDriverPrivInfo::pdata |

| NvU8 QbSdmmcDriverPrivInfo::PowerClass200MHzDdr180V |

| NvU8 QbSdmmcDriverPrivInfo::PowerClass26MHz195V |

| NvU8 QbSdmmcDriverPrivInfo::PowerClass26MHz360V |

| NvU8 QbSdmmcDriverPrivInfo::PowerClass52MHz195V |

| NvU8 QbSdmmcDriverPrivInfo::PowerClass52MHz360V |

| NvU8 QbSdmmcDriverPrivInfo::PowerClass52MHzDdr195V |

| NvU8 QbSdmmcDriverPrivInfo::PowerClass52MHzDdr360V |

| NvU8 QbSdmmcDriverPrivInfo::SdmmcBootModeBuffer[NVBOOT_SDMMC_BOOT_MODE_BUFFER_SIZE_IN_BYTES] |

| SdmmcInitLevel QbSdmmcDriverPrivInfo::SdmmcInitType |

| NvU8 QbSdmmcDriverPrivInfo::SdmmcInternalBuffer[NVBOOT_SDMMC_ECSD_BUFFER_SIZE_IN_BYTES] |

| NvU32 QbSdmmcDriverPrivInfo::SdmmcResponse[NVBOOT_SDMMC_RESPONSE_BUFFER_SIZE_IN_BYTES/sizeof(NvU32)] |

| NvU8 QbSdmmcDriverPrivInfo::SpecVersion |

| NvU8 QbSdmmcDriverPrivInfo::TranSpeed |

| NvU8 QbSdmmcDriverPrivInfo::TranSpeedInMHz |

| NvU32 QbSdmmcDriverPrivInfo::XferStartTime |

| NvU32 QbSdmmcDriverPrivInfo::XferTimeOutInUs |