DIP Switches Description

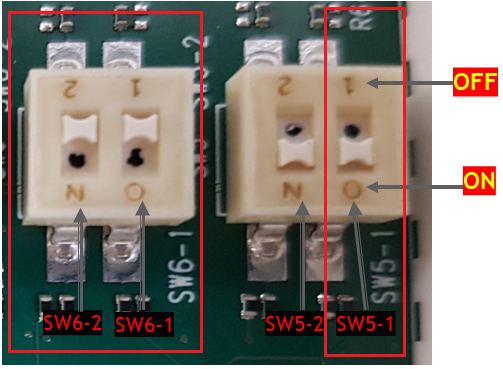

The below table defines the SMBus connectivity of the OCP 3.0 board to hosts 0-3.

SW# | SW6-1 | SW6-2 | SW5-1 | Notes |

I2C_MUX[Y0]: NC | OFF | OFF | OFF | |

I2C_MUX[Y1]: HOST#0 | OFF | OFF | ON | Default |

I2C_MUX[Y2]: HOST#1 | OFF | ON | OFF | |

I2C_MUX[Y3]: HOST#2 | OFF | ON | ON | |

I2C_MUX[Y4]: HOST#3 | ON | OFF | OFF | |

I2C_MUX[Y5]: NCSI | ON | OFF | ON | |

I2C_MUX[Y1]: HOST#0 | ON | ON | OFF | Unused (Defined as Host#0) |

I2C_MUX[Y1]: HOST#0 | ON | ON | ON | Unused (Defined as Host#0) |

TBD

The below table defines the MAIN_POWER_ENABLE and AUX_POWER_ENABLE DIP-switches status.

The OCP3.0 board should be connected to MEMH-OCP3 multi-host adapter.

SW# | SW3-2 | SW3-1 | Notes |

MAIN_POWER_ENABLE = constant "0" | N/A | OFF | |

MAIN_POWER_ENABLE = constant "1" | OFF | ON | |

MAIN_POWER_ENABLE = “1” according to the power sequence flow | ON | ON | Default |

AUX_POWER_ENABLE = “0” | OFF | N/A | |

AUX_POWER_ENABLE = “1” according to the power sequence flow | ON | N/A | Default |

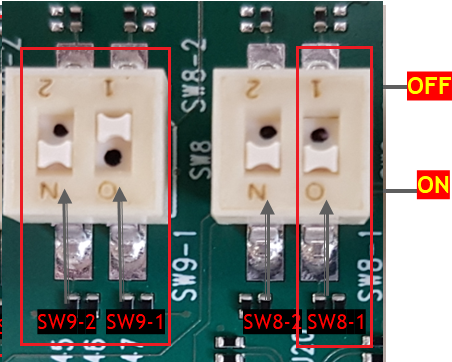

The below table defines the bifurcation bits status. The default value of the multi-host board is 0b110.

SW# | SW8-1 | SW9-2 | SW9-1 |

BIF [2] | ON | - | - |

BIF [1] | - | ON | - |

BIF [0] | - | - | OFF |