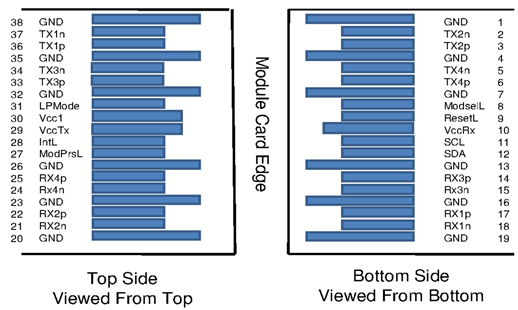

Pin Descriptions

The Active Optical Cable (AOC) pin assignment is SFF-8679 compliant.

Pin | Symbol | Description | Pin | Symbol | Description |

1 | Ground | Ground | 20 | Ground | Ground |

2 | Tx2n | Connected to Port 1 lane Rx2 Inverted Data | 21 | Rx2n | Connected to Port 1 lane Tx2 Inverted Data |

3 | Tx2p | Connected to Port 1 lane Rx2 Non-Inverted Data | 22 | Rx2p | Connected to Port 1 lane Tx2 Non-Inverted Data |

4 | Ground | Ground | 23 | Ground | Grounds |

5 | Tx4n | Connected to Port 2 lane Rx2 Non-Inverted Data | 24 | Rx4n | Connected to Port 2 lane Tx2 Inverted Data |

6 | Tx4p | Connected to Port 2 lane Rx2 Inverted Data | 25 | Rx4p | Connected to Port 2 lane Tx2 Non-Inverted Data |

7 | Ground | Ground | 26 | Ground | Ground |

8 | Mod-SelL | Cable Select | 27 | ModPrsL | Cable Present |

9 | ResetL | Cable Reset | 28 | IntL | Interrupt |

10 | Vcc Rx | +3.3V Power supply receiver | 29 | Vcc Tx | +3.3V Power supply transmitter |

11 | SCL | 2-wire serial interface clock | 30 | Vcc1 | +3.3V Power Supply |

12 | SDA | 2-wire serial interface data | 31 | LPMode | Low Power Mode |

13 | Ground | Ground | 32 | Ground | Ground |

14 | Rx3p | Connected to Port 2 lane Tx1 Non-Inverted Data | 33 | Tx3p | Connected to Port 2 lane Rx1 Non-Inverted Data |

15 | Rx3n | Connected to Port 2 lane Tx1 Inverted Data | 34 | Tx3n | Connected to Port 2 lane Rx1 Inverted Data |

16 | Ground | Ground | 35 | Ground | Ground |

17 | Rx1p | Connected to Port 1 lane Tx1 Non-Inverted Data | 36 | Tx1p | Connected to Port 1 lane Rx1 Non-Inverted Data |

18 | Rx1n | Connected to Port 1 lane Tx1 Inverted Data | 37 | Tx1n | Connected to Port 1 lane Rx1 Inverted Data |

19 | Ground | Ground | 38 | Ground | Ground |

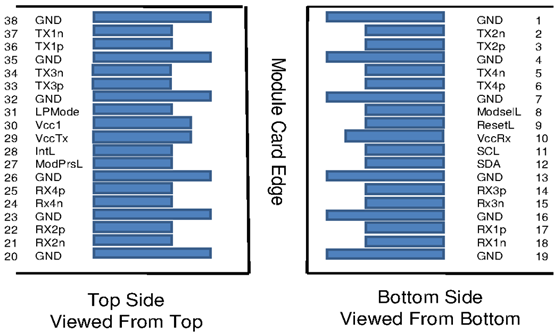

QSFP56 Module Pad Layout

Pin | Symbol | Description | Pin | Symbol | Description |

1 | Ground | Ground | 20 | Ground | Ground |

2 | Tx2n | Connected to lane Rx2 Inverted Data | 21 | Rx2n | Connected to lane Tx2 Inverted Data |

3 | Tx2p | Connected to lane Rx2 Non-Inverted Data | 22 | Rx2p | Connected to lane Tx2 Non-Inverted Data |

4 | Ground | Ground | 23 | Ground | Grounds |

5 | Not connected | Not connected | 24 | Not connected | Not connected |

6 | Not connected | Not connected | 25 | Not connected | Not connected |

7 | Ground | Ground | 26 | Ground | Ground |

8 | Mod-SelL | Cable Select | 27 | ModPrsL | Cable Present |

9 | ResetL | Cable Reset | 28 | IntL | Interrupt |

10 | Vcc Rx | +3.3V Power supply receiver | 29 | Vcc Tx | +3.3V Power supply transmitter |

11 | SCL | 2-wire serial interface clock | 30 | Vcc1 | +3.3V Power Supply |

12 | SDA | 2-wire serial interface data | 31 | LPMode | Low Power Mode |

13 | Ground | Ground | 32 | Ground | Ground |

14 | Not connected | Not connected | 33 | Not connected | Not connected |

15 | Not connected | Not connected | 34 | Not connected | Not connected |

16 | Ground | Ground | 35 | Ground | Ground |

17 | Rx1p | Connected to lane Tx1 Non-Inverted Data | 36 | Tx1p | Connected to lane Rx1 Non-Inverted Data |

18 | Rx1n | Connected to lane Tx1 Inverted Data | 37 | Tx1n | Connected to lane Rx1 Inverted Data |

19 | Ground | Ground | 38 | Ground | Ground |

QSFP56 Module Pad Layout

The pinout of the 100GbE ends of the cable is identical to the 200GbE end except that RF lanes 3 and 4 (pins 5, 6, 14, 15, 24, 25, 33, 34) are not used.

The transceiver complies with the SFF 8665 specification and has the following key features:

Physical layer link optimization:

Programmable Rx output amplitude

Programmable Rx output pre-emphasis

Digital Diagnostic Monitoring (DDM):

Rx receive optical power monitor

Tx transmit optical power monitor

Tx bias current monitor

Supply voltage monitor

Transceiver case temperature monitor

Other SFF-8636 functions and interrupt indications:

Tx & Rx LOS indication

Tx & Rx LOL indication