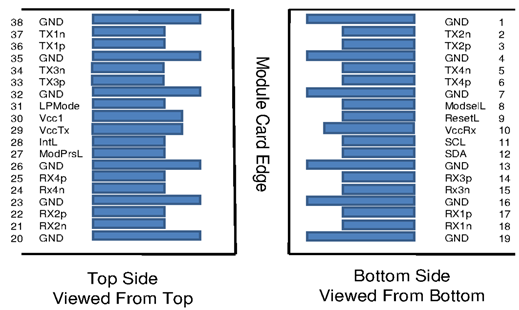

Pin Descriptions

The pin assignment is SFF-8679 compliant.

|

Pin |

Symbol |

Description |

Pin |

Symbol |

Description |

|

1 |

GND |

Ground |

20 |

GND |

Ground |

|

2 |

Tx2n |

Connected to Port 1 lane Rx2 Inverted Data |

21 |

Rx2n |

Connected to Port 1 lane Tx2 Inverted Data |

|

3 |

Tx2p |

Connected to Port 1 lane Rx2 Non-Inverted Data |

22 |

Rx2p |

Connected to Port 1 lane Tx2 Non-Inverted Data |

|

4 |

GND |

Ground |

23 |

GND |

Grounds |

|

5 |

Tx4n |

Transmitter Inverted Data Input |

24 |

Rx4n |

Connected to Port 1 lane Tx2 Inverted Data |

|

6 |

Tx4p |

Transmitter Non-Inverted Data Input |

25 |

Rx4p |

Connected to Port 1 lane Tx2 Non-Inverted Data |

|

7 |

GND |

Ground |

26 |

GND |

Ground |

|

8 |

ModSelL |

Module Select |

27 |

ModPrsL |

Module Present |

|

9 |

ResetL |

Module Reset |

28 |

IntL |

Interrupt |

|

10 |

Vcc Rx |

+3.3V Power Supply Receiver |

29 |

Vcc Tx |

+3.3V Power Supply Transmitter |

|

11 |

SCL |

2-wire Serial Interface Clock |

30 |

Vcc1 |

+3.3V Power Supply |

|

12 |

SDA |

2-wire Serial Interface Data |

31 |

LPMode |

Low Power Mode |

|

13 |

GND |

GND |

32 |

GND |

Ground |

|

14 |

Rx3p |

Receiver Non-Inverted Data Output |

33 |

Tx3p |

Connected to Port 1 lane Rx1 Non-Inverted Data |

|

15 |

Rx3n |

Receiver Inverted Data Output |

34 |

Tx3n |

Connected to Port 1 lane Rx1 Inverted Data |

|

16 |

GND |

Ground |

35 |

GND |

Ground |

|

17 |

Rx1p |

Connected to Port 1 lane Tx1 Non-Inverted Data |

36 |

Tx1p |

Connected to Port 1 lane Rx1 Non-Inverted Data |

|

18 |

Rx1n |

Connected to Port 1 lane Tx1 Inverted Data |

37 |

Tx1n |

Connected to Port 1 lane Rx1 Inverted Data |

|

19 |

GND |

Ground |

38 |

GND |

Ground |

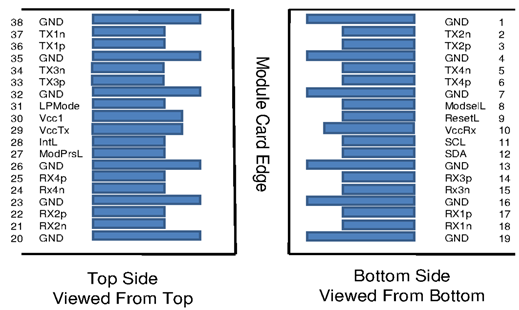

QSFP56 Module Pad Layout for 200Gb/s End

|

Pin |

Symbol |

Description |

Pin |

Symbol |

Description |

|

1 |

GND |

Ground |

20 |

GND |

Ground |

|

2 |

Tx2n |

Connected to lane Rx2 Inverted Data |

21 |

Rx2n |

Connected to lane Tx2 Inverted Data |

|

3 |

Tx2p |

Connected to lane Rx2 Non-Inverted Data |

22 |

Rx2p |

Connected to lane Tx2 Non-Inverted Data |

|

4 |

GND |

Ground |

23 |

GND |

Grounds |

|

5 |

Tx4n |

Not connected |

24 |

Rx4n |

Not connected |

|

6 |

Tx4p |

Not connected |

25 |

Rx4p |

Not connected |

|

7 |

GND |

Ground |

26 |

GND |

Ground |

|

8 |

ModSelL |

Module Select |

27 |

ModPrsL |

Module Present |

|

9 |

ResetL |

Module Reset |

28 |

IntL |

Interrupt |

|

10 |

Vcc Rx |

+3.3V Power Supply Receiver |

29 |

Vcc Tx |

+3.3V Power Supply Transmitter |

|

11 |

SCL |

2-wire Serial Interface Clock |

30 |

Vcc1 |

+3.3V Power Supply |

|

12 |

SDA |

2-wire Serial Interface Data |

31 |

LPMode |

Low Power Mode |

|

13 |

GND |

GND |

32 |

GND |

Ground |

|

14 |

Rx3p |

Not connected |

33 |

Tx3p |

Not connected |

|

15 |

Rx3n |

Not connected |

34 |

Tx3n |

Not connected |

|

16 |

GND |

Ground |

35 |

GND |

Ground |

|

17 |

Rx1p |

Connected to lane Tx1 Non-Inverted Data |

36 |

Tx1p |

Connected to lane Rx1 Non-Inverted Data |

|

18 |

Rx1n |

Connected to lane Tx1 Inverted Data |

37 |

Tx1n |

Connected to lane Rx1 Inverted Data |

|

19 |

GND |

Ground |

38 |

GND |

Ground |

QSFP56 Module Pad Layout for 100Gb/s End

The Pinout of the 100Gb/s ends of the cable is identical to the 200Gb/s end except that RF lanes 3 and 4 (pins 5, 6, 14, 15, 24, 25, 33, 34) are not connected.