Intrusion Prevention System (IPS)

NVIDIA DOCA IPS Reference Application Guide

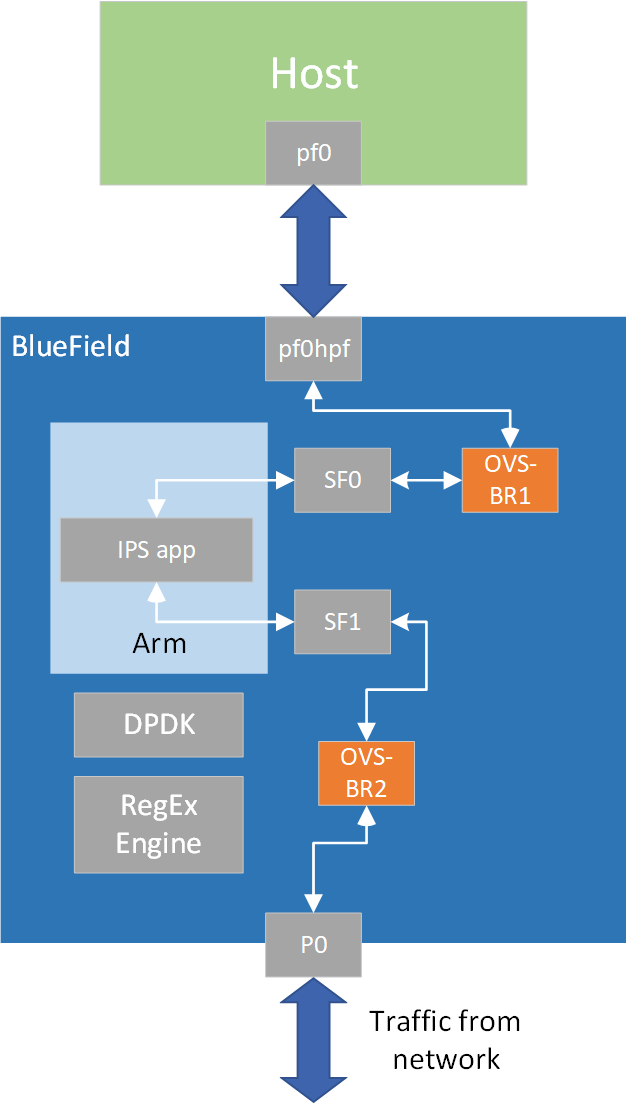

This document provides an intrusion prevention system (IPS) implementation on top of NVIDIA® BlueField® DPU.

Intrusion prevention system (IPS) is an application that monitors a network for malicious activity or policy violations.

IPS uses the deep packet inspection (DPI) engine to scan network flow for malicious content based on predefined Suricata signatures. Packets that are deemed malicious are dropped and a corresponding message is printed.

IPS supports NetFlow protocol for sending data from the DPU to remote NetFlow collector for further analysis.

Connection tracking is also supported for tracking all network connections or flows which helps the identification of all the packets that make up a flow for better handling of the network traffic.

This document describes how to build and run the IPS application both on the host and on the DPU.

IPS runs on top of DPDK-based stateful flow tracking (SFT) to identify the flow that each packet belongs to, then uses DPI to process L7 classification.

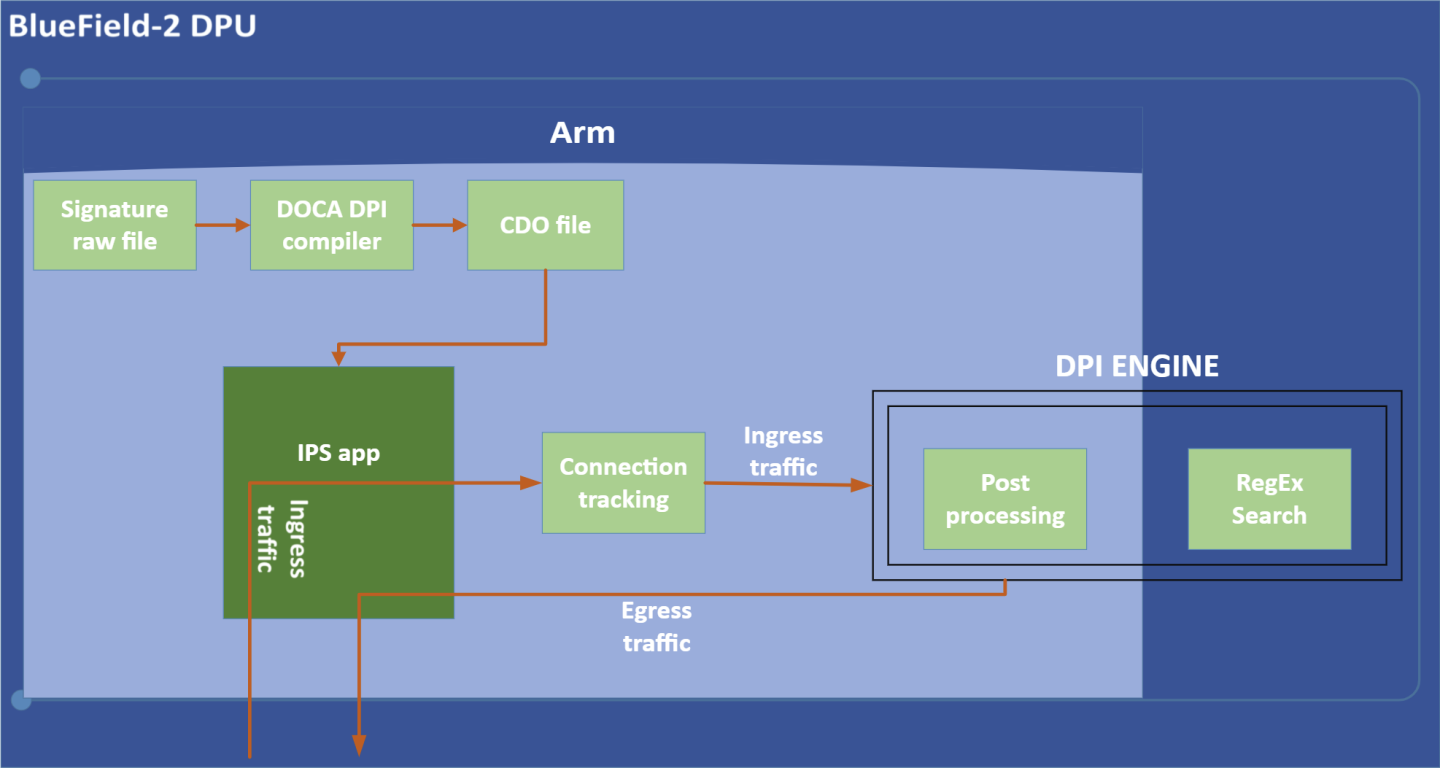

- Signatures are compiled by DPI compiler and then loaded to DPI engine. See DOCA DPI Compiler for more information.

- Ingress traffic is identified using the stateful table module which utilizes the connection tracking hardware offloads.

- Traffic is scanned against DPI-engine-compiled signature DB.

- Post-processing is performed for match decision.

- Matched flows are identified and drop actions can be offloaded to the hardware to increase performance as no further inspection is needed.

- Flow termination is done by a configurable aging timer set in the SFT to 60 seconds. When a flow is offloaded, it cannot be tracked and destroyed.

- Parse application argument.

arg_parser_init();

- Initialize Arg Parser resources.

- Register DOCA general flags.

register_ips_params();

- Register IPS application flags.

arg_parser_start();

- Parsing DPDK flags and calling

rte_eal_init()function. - Parsing APP flags.

- Initialize DPDK.

dpdk_init();

- Initialize SFT.

- Initialize DPDK ports, including mempool allocation.

- Initialize IPS application resources including DPI engine and NetFlow.

ips_init();

- Configure DPI packet processing.

ips_worker_lcores_run();

- Configure DPI enqueue packets.

- Send jobs to RegEx engine.

- Configure DPI dequeue packets.

- IPS destroy.

ips_destroy();

- Stop and free DPI resources.

- Destroy netflow resources.

- Stop SFT.

- Free IPS resources.

- Refer to DOCA Installation Guide for details on how to install BlueField related software.

- The IPS application binary is located under

/opt/mellanox/doca/examples/ips/bin/doca_ips. - To rebuild the application:

- Run:

cd /opt/mellanox/doca/examples/ips/src meson /tmp/build ninja -C /tmp/build

doca_ipsis created under/tmp/build. - The build process depends on the

PKG_CONFIG_PATHenvironment variable to locate the DPDK libraries. If the variable accidentally gets corrupted and the build fails, run the following command:- For Ubuntu:

export PKF_CONFIG_PATH=$PKG_CONFIG_PATH:/opt/mellanox/dpdk/lib/aarch64-linux-gnu/pkgconfig

- For CentOS:

export PKG_CONFIG_PATH=$PKG_CONFIG_PATH:/opt/mellanox/dpdk/lib64/pkgconfig

- For Ubuntu:

- Run:

- Pre-run setup

- The IPS example is based on DPDK libraries. Therefore, the user is required to provide DPDK flags and allocate huge pages. Run:

echo 2048 > /sys/kernel/mm/hugepages/hugepages-2048kB/nr_hugepages

- Make sure the RegEx engine is active:

systemctl status mlx-regex

Active: failed), run:systemctl start mlx-regex

- The IPS example is based on DPDK libraries. Therefore, the user is required to provide DPDK flags and allocate huge pages. Run:

- To run the application:

Usage: doca_ips [DPDK Flags] -- [DOCA Flags] [Program Flags] DOCA Flags: -h, --help Print a help synopsis -l, --log-level Set the log level for the app <CRITICAL=0, DEBUG=4> Program Flags: -p, --print-match Prints FID when matched in DPI engine -n, --netflow Collect netflow statistics and send according to conf file -o, --output-csv <path> Path to the output of the CSV file -c, --cdo <path> Path to CDO file compiled from a valid PDD

/opt/mellanox/doca/examples/ips/bin/doca_ips -a 0000:03:00.0,class=regex -a auxiliary:mlx5_core.sf.4,sft_en=1 -a auxiliary:mlx5_core.sf.5,sft_en=1 –– --cdo /root/ips.cdo -p -n

Using a JSON file:Note:The SFT supports a maximum of 64 queues. Therefore, the application cannot be run with more than 64 cores. To limit the number of cores, run:

/opt/mellanox/doca/examples/ips/bin/doca_ips -a 0000:03:00.0,class=regex -a auxiliary:mlx5_core.sf.4,sft_en=1 -a auxiliary:mlx5_core.sf.5,sft_en=1 -l 0-64 –– --cdo /root/ips.cdo -p -n

This limits the application to use 65 cores (core-0 to core-64). That is 1 core for the main thread and 64 cores to serve as workers.

doca_ips --json [json_file]

For example:/opt/mellanox/doca/examples/ips/bin/doca_ips –-json /root/ips_params.json

Note:Sub-functions must be enabled according to Scalable Function Setup Guide.

For additional information on available flags for DPDK, useNote:The flags

-a 0000:03:00.0,class=regex -a auxiliary:mlx5_core.sf.4,sft_en=1 -a auxiliary:mlx5_core.sf.5,sft_en=1are necessary for proper usage of the application. Modifying these flags results in unexpected behavior as only 2 ports are supported. The SF numbers are arbitrary and configurable. The RegEx device, however, is not and must be initiated on port 0.-hbefore the--separator:/opt/mellanox/doca/examples/ips/bin/doca_ips -h

For additional information on the app, use-hafter the--separator:/opt/mellanox/doca/examples/ips/bin/doca_ips -- -h

Refer to NVIDIA DOCA Arg Parser User Guide for more information.

| Flag Type | Short Flag | Long Flag/JSON Key | Description | JSON Content |

|---|---|---|---|---|

| DPDK Flags | a | devices | Adds a PCIe device into the list of devices to probe |

|

| l | core-list | Lists cores to run on |

|

|

| General Flags | l | log-level | Sets the log level for the application:

|

|

| h | help | Prints a help synopsis | N/A | |

| Program Flags | p | print-match | Prints FID when matched in DPI engine |

|

| n | netflow | Collects netflow statistics and sends according to .conf file |

|

|

| o | output-csv | Path to the output of the CSV file |

|

|

| c | cdo | Path to CDO file compiled from a valid PDD |

|

cd /opt/mellanox/doca/examples/ips/

./doca_ips -a 0000:21:00.0,class=regex -a 0000:21:00.3 -a 0000:21:00.4 -- --cdo ~/ips.cdo

Refer to section "Running DOCA Application on Host" in NVIDIA DOCA Virtual Functions User Guide.

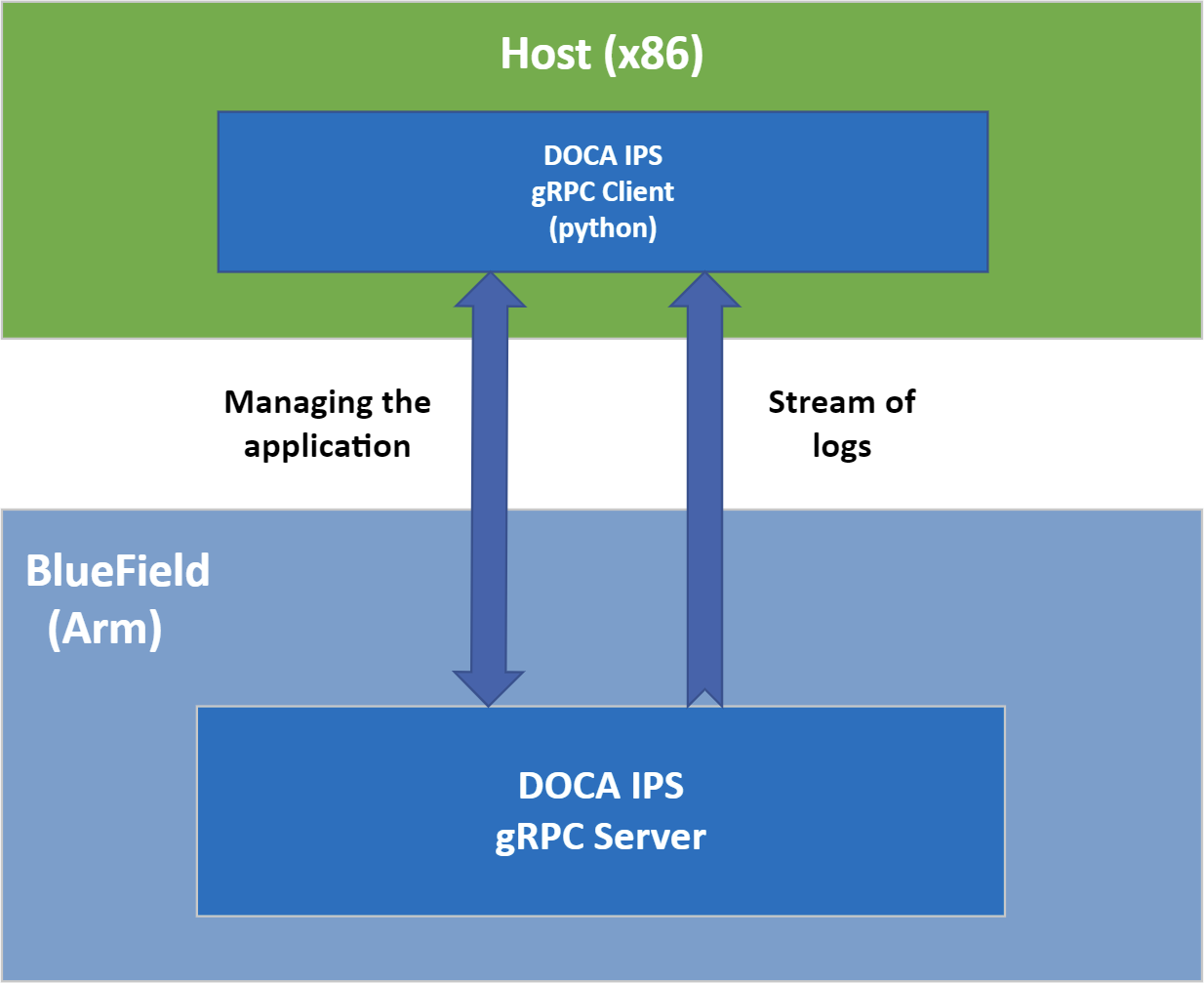

For instructions on running the gRPC application server on BlueField, refer to NVIDIA DOCA gRPC Infrastructure User Guide.

To run the Python client of the gRPC-enabled application:

./doca_ips_gRPC_client.py -d/--debug <server address[:server port]>

For example:

/opt/mellanox/doca/examples/ips/bin/grpc/client/doca_ips_gRPC_client.py 192.168.104.2

Refer to known issue 2872829 in NVIDIA DOCA Release Notes regarding the deployment of the gRPC enabled application using the DOCA gRPC orchestrator.

Please refer to known issue 2872883 in NVIDIA DOCA Release Notes regarding the execution of the gRPC python client.

The IPS example supports a container-based deployment. Refer to the NVIDIA DOCA Container Deployment Guide for more information.

Application-specific configuration steps may be found on NGC under the application's container page.

Notice

This document is provided for information purposes only and shall not be regarded as a warranty of a certain functionality, condition, or quality of a product. NVIDIA Corporation nor any of its direct or indirect subsidiaries and affiliates (collectively: “NVIDIA”) make no representations or warranties, expressed or implied, as to the accuracy or completeness of the information contained in this document and assume no responsibility for any errors contained herein. NVIDIA shall have no liability for the consequences or use of such information or for any infringement of patents or other rights of third parties that may result from its use. This document is not a commitment to develop, release, or deliver any Material (defined below), code, or functionality.

NVIDIA reserves the right to make corrections, modifications, enhancements, improvements, and any other changes to this document, at any time without notice.

Customer should obtain the latest relevant information before placing orders and should verify that such information is current and complete.

NVIDIA products are sold subject to the NVIDIA standard terms and conditions of sale supplied at the time of order acknowledgement, unless otherwise agreed in an individual sales agreement signed by authorized representatives of NVIDIA and customer (“Terms of Sale”). NVIDIA hereby expressly objects to applying any customer general terms and conditions with regards to the purchase of the NVIDIA product referenced in this document. No contractual obligations are formed either directly or indirectly by this document.

NVIDIA products are not designed, authorized, or warranted to be suitable for use in medical, military, aircraft, space, or life support equipment, nor in applications where failure or malfunction of the NVIDIA product can reasonably be expected to result in personal injury, death, or property or environmental damage. NVIDIA accepts no liability for inclusion and/or use of NVIDIA products in such equipment or applications and therefore such inclusion and/or use is at customer’s own risk.

NVIDIA makes no representation or warranty that products based on this document will be suitable for any specified use. Testing of all parameters of each product is not necessarily performed by NVIDIA. It is customer’s sole responsibility to evaluate and determine the applicability of any information contained in this document, ensure the product is suitable and fit for the application planned by customer, and perform the necessary testing for the application in order to avoid a default of the application or the product. Weaknesses in customer’s product designs may affect the quality and reliability of the NVIDIA product and may result in additional or different conditions and/or requirements beyond those contained in this document. NVIDIA accepts no liability related to any default, damage, costs, or problem which may be based on or attributable to: (i) the use of the NVIDIA product in any manner that is contrary to this document or (ii) customer product designs.

No license, either expressed or implied, is granted under any NVIDIA patent right, copyright, or other NVIDIA intellectual property right under this document. Information published by NVIDIA regarding third-party products or services does not constitute a license from NVIDIA to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property rights of the third party, or a license from NVIDIA under the patents or other intellectual property rights of NVIDIA.

Reproduction of information in this document is permissible only if approved in advance by NVIDIA in writing, reproduced without alteration and in full compliance with all applicable export laws and regulations, and accompanied by all associated conditions, limitations, and notices.

THIS DOCUMENT AND ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS, AND OTHER DOCUMENTS (TOGETHER AND SEPARATELY, “MATERIALS”) ARE BEING PROVIDED “AS IS.” NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY, OR OTHERWISE WITH RESPECT TO THE MATERIALS, AND EXPRESSLY DISCLAIMS ALL IMPLIED WARRANTIES OF NONINFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE. TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL NVIDIA BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF NVIDIA HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Notwithstanding any damages that customer might incur for any reason whatsoever, NVIDIA’s aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms of Sale for the product.

Trademarks

NVIDIA, the NVIDIA logo, and Mellanox are trademarks and/or registered trademarks of Mellanox Technologies Ltd. and/or NVIDIA Corporation in the U.S. and in other countries. The registered trademark Linux® is used pursuant to a sublicense from the Linux Foundation, the exclusive licensee of Linus Torvalds, owner of the mark on a world¬wide basis. Other company and product names may be trademarks of the respective companies with which they are associated.

Copyright

© 2022 NVIDIA Corporation & affiliates. All rights reserved.